常用EDA程序集Word下载.docx

《常用EDA程序集Word下载.docx》由会员分享,可在线阅读,更多相关《常用EDA程序集Word下载.docx(14页珍藏版)》请在冰豆网上搜索。

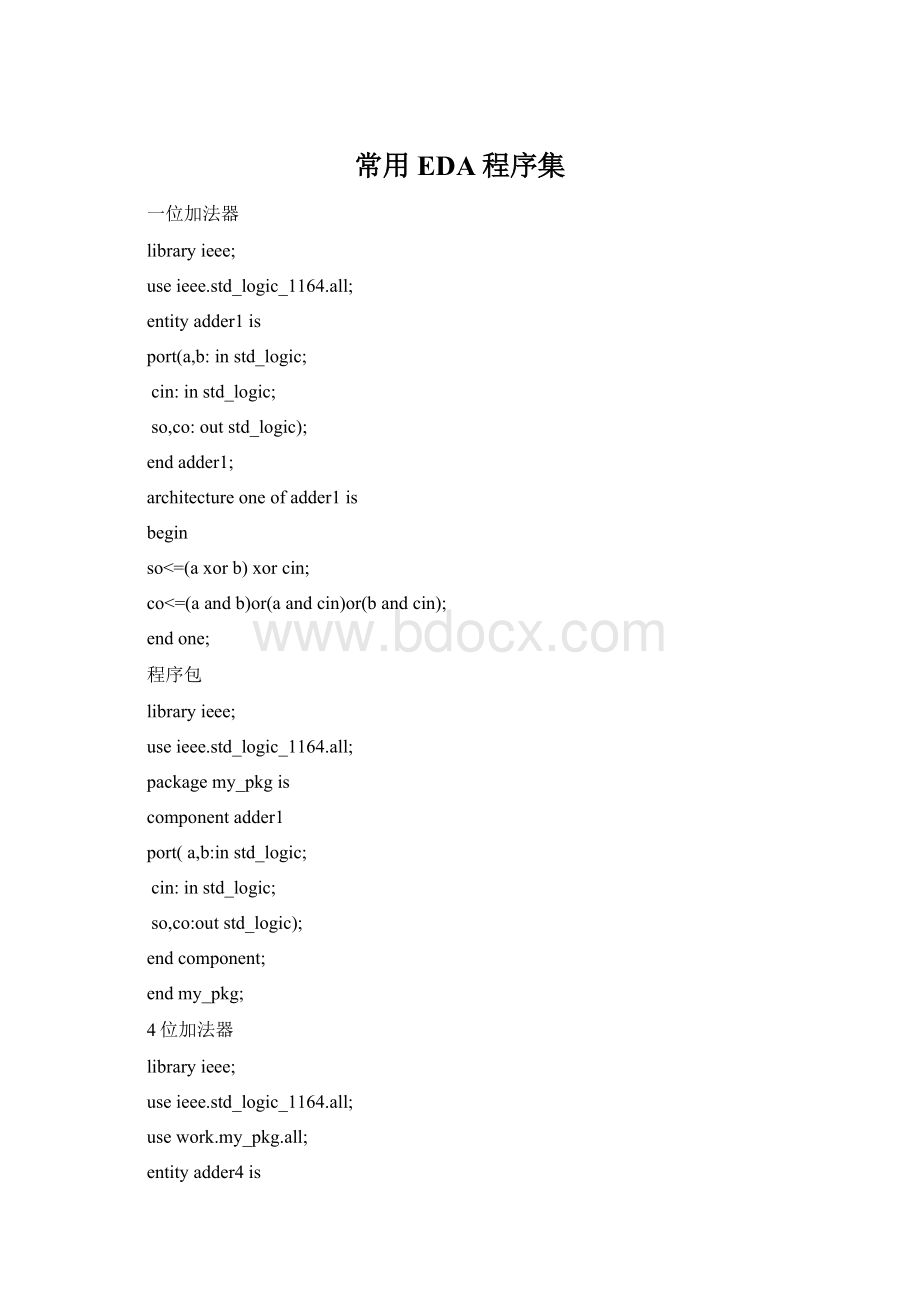

instd_logic;

outstd_logic);

endcomponent;

endmy_pkg;

4位加法器

usework.my_pkg.all;

entityadder4is

instd_logic_vector(3downto0);

sum:

outstd_logic_vector(3downto0);

cout:

endadder4;

architectureadder4behvofadder4is

signald:

std_logic_vector(1to3);

u1:

adder1portmap(a(0),b(0),cin,sum(0),d

(1));

u2:

adder1portmap(a

(1),b

(1),d

(1),sum

(1),d

(2));

u3:

adder1portmap(a

(2),b

(2),d

(2),sum

(2),d(3));

u4:

adder1portmap(a(3),b(3),d(3),sum(3),cout);

endadder4behv;

4位移位寄存器

entitydff1is

port(d,clk:

q:

enddff1;

architectureoneofdff1is

signalu:

std_logic:

='

0'

;

begin

process(d,clk,u)

if(clk'

eventandclk='

1'

)then

u<

=d;

endif;

q<

=u;

endprocess;

entityshifteris

port(d0,clk:

q0:

endshifter;

architectureonesofshifteris

componentdff1

port(d,clk:

signala:

dff1portmap(d0,clk,a

(1));

dff1portmap(a

(1),clk,a

(2));

dff1portmap(a

(2),clk,a(3));

dff1portmap(a(3),clk,q0);

endones;

4位二进制计数器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYcnt4eIS

port(clr,clk,ena:

INSTD_LOGIC;

cout:

OUTSTD_LOGIC;

BUFFERINTEGERRANGE0TO15);

ENDcnt4e;

ARCHITECTUREONEOFcnt4eIS

BEGIN

PROCESS(clr,clk,ena)

IFclr='

then

q<

=0;

cout<

elsifclk'

EVENTANDclk='

THEN

ifena='

ifq=15thenq<

cout<

elsifq=14Thenq<

=q+1;

elseq<

ENDIF;

ENDPROCESS;

ENDONE;

4选1数据选择器

entitymux4_1is

port(a,b,c,d:

s0,s1:

y:

endmux4_1;

architecturegoodofmux4_1is

signals:

std_logic_vector(1downto0);

s<

=s1&

s0;

process(a,b,c,d,s)

casesis

when"

00"

=>

y<

=a;

01"

=b;

10"

=c;

11"

whenothers=>

X'

endcase;

endgood;

componentmux4_1

endcomponent;

双4选1

entityddmux4_1is

port(a,b,c,d:

instd_logic_vector(3downto0);

outstd_logic_vector(3downto0));

endddmux4_1;

architectureoneofddmux4_1is

std_logic_vector(3downto0);

beginlab1:

fornin0to3generate

ux:

mux4_1portmap(a(n),b(n),c(n),d(n),s0,s1,u(n));

endgenerate;

38译码器

entitydecode38is

port(y:

instd_logic_vector(2downto0);

a:

outstd_logic_vector(7downto0));

enddecode38;

architectureoneofdecode38is

process(y)

if(y<

="

000"

)thena<

11111110"

elsif(y<

001"

11111101"

010"

11111011"

011"

11110111"

100"

11101111"

101"

11011111"

110"

10111111"

111"

01111111"

elsea<

11111111"

D触发器

entitydtriggeris

port(clk,d,clr:

enddtrigger;

architectureoneofdtriggeris

process(clk,d,clr)

if(clr='

)thenq<

elsif(clk'

1位减法器:

USEIEEE.STD_LOGIC_UNSIGNED.all;

entitysubber1is

port(a,b,cin:

s:

outstd_logic;

endsubber1;

architectureoneofsubber1is

s<

=(axorb)xorcin;

=((nota)nandb)nand(not(axorb)nandcin);

4位减法器:

USEWORK.my_pkg.all;

entitysubber4is

outstd_logic_vector(3downto0);

endsubber4;

architectureoneofsubber4is

signalcout0,cout1,cout2:

std_logic;

subber1portmap(a(0),b(0),cin,s(0),cout0);

subber1portmap(a

(1),b

(1),cout0,s

(1),cout1);

subber1portmap(a

(2),b

(2),cout1,s

(2),cout2);

subber1portmap(a(3),b(3),cout2,s(3),cout);

程序包:

USEIEEE.STD_LOGIC_1164.A