latchup分析Word文档格式.docx

《latchup分析Word文档格式.docx》由会员分享,可在线阅读,更多相关《latchup分析Word文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

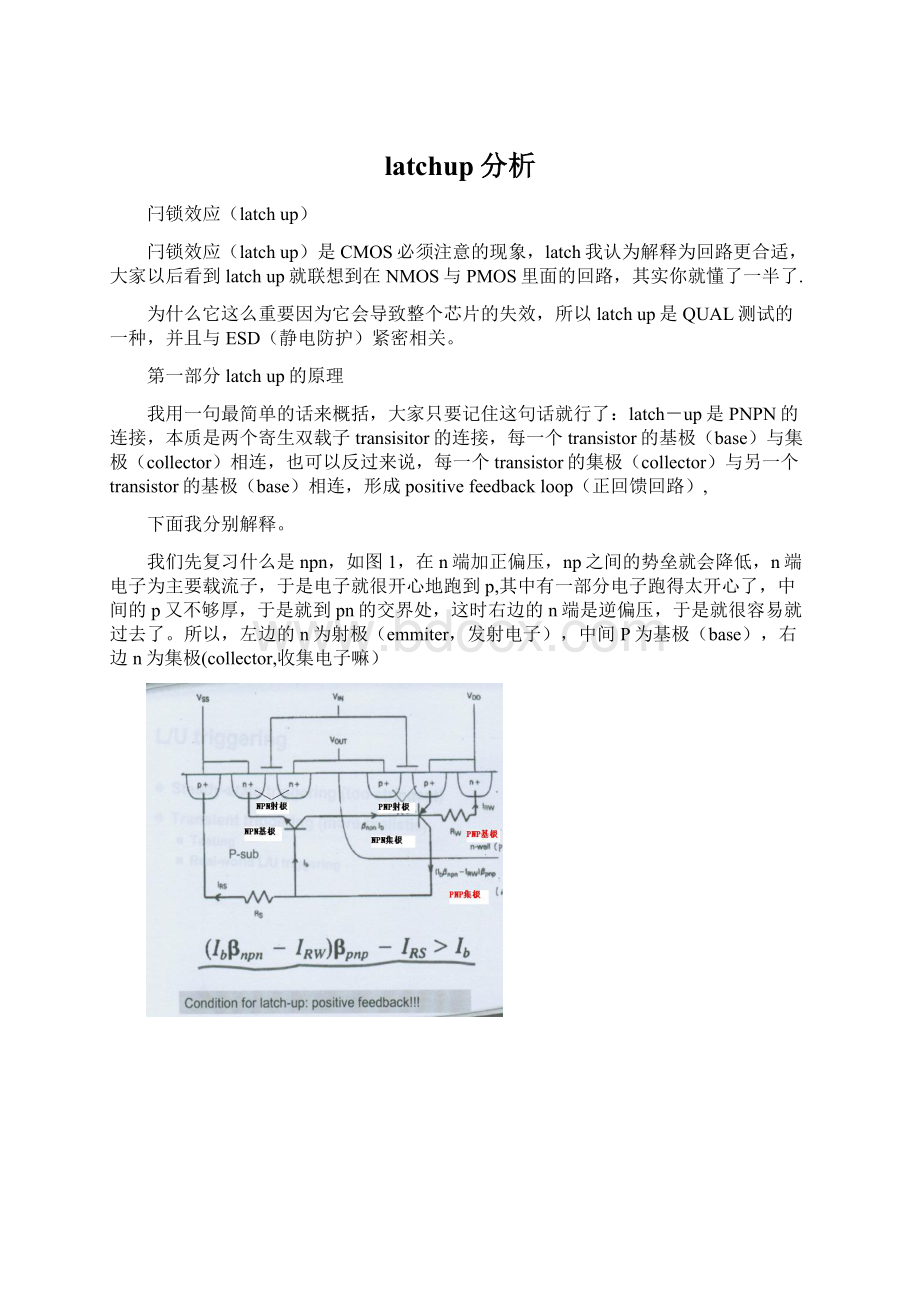

左边是npn,右边是pnp

图3是电路示意图。

大家可以看出,P-sub既是npn的基极,又是pnp的集极;

n-well既是既是pnp的基极,又是npn的集极,所以说,每一个transistor的集极(collector)与另一个transistor的基极(base)相连。

那么电流怎么走呢

比如在P+加5V-->

电洞被从P+推到Nwell-->

越过nwell再到psub-->

这个时候,大家注意,电洞有两条路可走,一是跑到NMOS的N+,二是跑到旁边的Nwell,nwell比n+深,当然更好去,所以电洞又回去了。

这样就形成回路,而且会循环下去,gate基本上就成了摆设,完全控制不了电子或电洞的走向,所以CMOS就失效了。

图4是一个公式,我也不知道是什么意思,反正2个β变小,latchup就不容易发生

。

图5是首位发现latchup的达人做出的解释:

latchup是由于fieldinversion(反转电场),值得记住,但我不懂。

第二部分如何解决latchup

大家只要记住一句话,电子和电洞,都是单纯的家伙,哪里容易去,他们就去哪里,就像他们本来想去看朋友,走到半路看到一个美女在对他们打招呼,于是就很自然的跑到美女那边去了,不去本来该去的地方。

所以,下面所有的解决方法,要么是阻止电子或电洞去看美女,或者找个更漂亮的美女吸引他们过去。

解决方法目前为止,我总结出7个,如下:

1.加大N+,P+距离,这是最容易想到的办法,虽然前面有美女,但是太远,所以还是不去了。

电子或电洞也是这样。

但是,这样的,必然会导致芯片的集成度下降,所以这是很傻的办法,没人用。

2.加深isolation.就是在NMOS和PMOS之间加隔离,比如STI以下)和FieldOX以上)。

但是,隔离深度总是有限的,电子或电洞总有办法绕过去。

3.SOI。

SilicononInsulator,在Si的表面加一层SiO2,使well或者N+无法直接与P-sub连接,这样电子或电洞就到不了下面。

4.Retrogradedwell,倒阱,用高能离子注入将杂质打入阱底部,这种阱不像常规的阱表面浓度最高,阱底部浓度最低,而是正相反,所以叫做倒阱。

这个概念极为重要!

下面的浓度很大,那么电子或电洞到了基极以后,高浓深井可以有效的增加复合,就不想到集极去了,降低bipolar的放大系数,使没有backbias偏置的晶体管免于latch-up。

5.EPIwafer。

这也是一个重要的概念,在heavydopedsubstrate上面,加上一层轻微掺杂的EPIlayer,这就是EPIwafer(即外延片,晶圆是wafer,在wafer基础上做EPI工艺出来的wafer就是EPIwafer)。

当这层EPIlayer够薄的时候,pnp的载流子就不想去npn了,而是跑到更舒服的heavydopedsubstrate,因为heavydoped底材的浓度比P-sub的掺杂浓度高多了。

如图6很明显,EPIlayer越薄越好,如图7,3um的EPIlayer,triggercurrent(引发latchup的电流)最大,最不容易发生latchup但是不能太薄,不然底材的离子就扩散到EPIlayer里面,造成离子浓度改变。

这是用EPIwafer的原因,EPIwafer缺点只有一个:

贵!

外延(Epitaxy,简称Epi)工艺是指在单晶衬底上生长一层跟衬底具有相同晶格排列的单晶材料,外延层可以是同质外延层(Si/Si),也可以是异质外延层(SiGe/Si或SiC/Si等);

6.Guardring。

在N+和P+的旁边加一个guardband,相当于保险,如图8。

大家看图9,应该会明白为什么Guardring能防止latchup,与EPI是类似的道理。

7.Designrule。

这个很简单,在design的时候,会规定P+,N+的距离,guardring离P+,N+的距离等等。

最后一个问题是,这么多解决方法,到底用哪一个答案还是很简单,只要你有钱,能一起用就一起用。

latchup(闩锁反应)

我们无可逃避,只能坚强应对。

首先来看一下latchup时拍到的照片

放大后的照片红点部分就是发生latchup的位置,latchup可谓芯片杀手,通过循环放大

Q"

Gsj;

ut:

y}芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA

c8\I*\aqnj芯片,设计,版图,芯片制造,工艺,制程,封装,测试,wafer,chip,ic,process,layout,package,FA,QA最终将芯片烧毁。

我不想告诉大家latchup有多可怕,但有一点是应该知道的

+}j

eXMlY芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA这种现象损害了芯片。

图片附件:

(2007-1-3016:

38,K)

9_NQ2QX0l{%G芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA

i|?

\#HFK芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA

]%g%jk0x6{在CMOS制程里,这种情况就是由于npn或pnp结构形成的放大电路造成的。

B$F@cmv0p&

|

P\g

所以要了解latchup现象,就必然首先了解放大电路是如何构成的,而最根本的就

归结到npn或pnp晶体管是如何工作的。

了解晶体管的工作原理是研究latchup的重点。

]GO9?

qk;

E

而解决这一问题的关键又在于了解放大电路是如何构成的,这是两个方面,以下着重讨论。

ajQBsRc_Ot

一、晶体管的工作原理

j_6J$mM+pQ)I6q&

k半导体工艺中,由高纯度的本征半导体进行掺杂,从而形成不同的形态。

如果掺杂5价原子因电子数大于空穴

'

C,OuP)X-Y

_3U"

K数即称为n型半导体,若掺杂3价原子因电子数小于空穴数即称为p型半导体。

空穴和电子都能搬运电荷,因而1rP

d芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,i'

m

gQf称载流子。

@"

}:

IAzI;

zg半导体技术天地[SemiconductorTechnologyWorld]将两种形态的半导体相邻结合到一起,由于彼此所含电子和空穴数浓度不同,因而相互扩散,由浓度高的向浓度低;

b})v[U-K0wL4J4yyF的地方移动,电子和空穴会在一定时间内相互结合而消失,以保持中性,这样形成一段没有载流子的空间,称为耗尽7b,nY/|4~ll"

q9|j半导体技术天地[SemiconductorTechnologyWorld]层。

耗尽层存在电位差,有电场的存在,称之为内电场。

在电场的作用下载流子发生定向移动,称之为漂移。

扩散0}/i/n&

_-M~芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA使电场增加,空间电荷范围加大,而漂移则在减弱空间电荷范围。

这种将pn相邻结合到一起制成的晶体结构,0m+wxX:

r+_F$n芯片,设计,版图,芯片制造,工艺,制程,封装,测试,wafer,chip,ic,process,layout,package,FA,QA称之为pn结。

M/IF+G3Pa0c1M\

pn结在没有外力的情况下,处于热平衡状态,这种平衡状态是处于动态之中的,即扩散运动与漂移运行达成的平衡状态。

C)Gr7Mz#s芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA

pn结的外加电压,如果p端的电位高于n端的电位,这样的外电电场削弱了内电场,有利于多数载流子的扩散,$O[Q(\xf~rq&

}6[W芯片,设计,版图,芯片制造,工艺,制程,封装,测试,wafer,chip,ic,process,layout,package,FA,QAxzVXwf$G形成从p流向n的电流,称为正向偏置,反之,载流子则几乎不发生移动,称为反向偏置。

反向电压大于某一值时,_

_K[1X1Z会有导致pn结击穿,称为齐纳击穿或隧道击穿。

另一种情况,是pn结两侧的杂质浓度过小,在高的反向电压作用下,\6it2@G!

oh(k_V6l引起价键的断裂,从而使电流成倍增加,称为电子雪崩现象或雪崩击穿。

pn结制作成元器件使用就是二极管。

8j#b5Fkl5OK

LL|1`o\[$n半导体技术天地[SemiconductorTechnologyWorld]

pn结,p区空穴向n区扩散,n区电子向p区扩散,在相遇处复合。

p区空穴扩散后留下负离子,而n区电子扩散后留下正Q+H7r~PZ@)p离子,形成由n指向p的内电场。

正向偏置时,p区不断提供复合留下的负离子,n区则复合留下的正离子,使得内电场s_/G芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafer,chip,ic,design,fabrication,process,layout,package,test,FA,RA,QA+jH+x8j^!

|芯片,设计,版图,晶圆制造,工艺,制程,封装,测试,wafe