数电复习题有标准答案样本Word文档格式.docx

《数电复习题有标准答案样本Word文档格式.docx》由会员分享,可在线阅读,更多相关《数电复习题有标准答案样本Word文档格式.docx(9页珍藏版)》请在冰豆网上搜索。

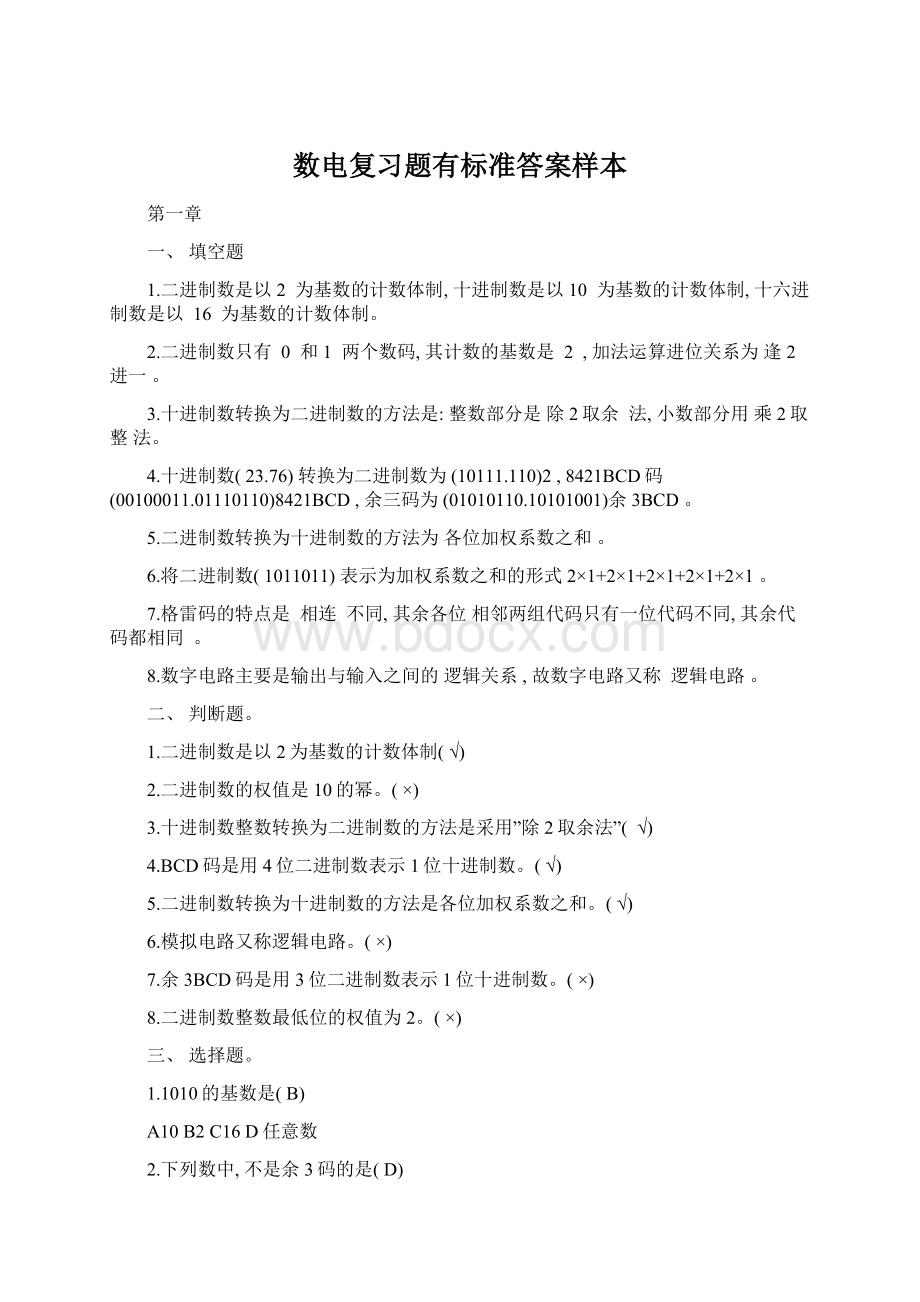

2.二进制数的权值是10的幂。

(×

)

3.十进制数整数转换为二进制数的方法是采用”除2取余法”(√)

4.BCD码是用4位二进制数表示1位十进制数。

(√)

5.二进制数转换为十进制数的方法是各位加权系数之和。

6.模拟电路又称逻辑电路。

7.余3BCD码是用3位二进制数表示1位十进制数。

8.二进制数整数最低位的权值为2。

三、选择题。

1.1010的基数是(B)

A10B2C16D任意数

2.下列数中,不是余3码的是(D)

A1011B1010C0110D0000

3.二进制数最低位的权值是(B)

A0B1C2D4

4.十进制数的权值是(A)

A10的幂B2的幂C16的幂D8的幂

5.二进制数的权值为(B)

A10的幂B2的幂C16的幂D8的幂

6.在二进制计数系统中每个变量的取值为(A)

A0和1B0—7C0—10D0—16

7.十进制计数系统包含(B)

A六个数字B十个数字C十六个数字D三十二个数字

8.(0101)8421BCD对应的十进制数为(B)

A8561B8975C7AD37971

第二章

一、填空题。

1.逻辑变量和逻辑函数只有0,1两种取值,它们仅代表两种相反的逻辑状态。

2.描述逻辑函数值与对应变量取值关系的表格叫真值表。

3.基本逻辑关系有三种,它们是与,或,非。

4.常见的复合逻辑运算有与非,或非,与或非,异或,同或。

5.与或逻辑函数的标准表示式是最小项表示式。

6.逻辑函数Y=AB’+(A’B)’的反函数是Y=(A+B)(A+B),对偶式是Y=(A+B)(A+B)。

7.摩根定律的两种形式是互为对偶式。

8.最简与或式的标准是逻辑式中的与项最少;

每个乘积项中的变量最少。

9.逻辑函数常见的化简方法有代数法和卡诺图法。

10、逻辑函数中任意二个最小项之积为0。

1.逻辑函数的标准与或式又称最小项表示式,它是惟一的。

2.列逻辑函数真值表时,若变量在表中的位置变化,就能够列出不同的真值表。

3.无论变量如何取值,几个最小项之和都是零,则这几个最小项须是无关项。

4.卡诺图化简逻辑函数的本质就是合并相邻最小项。

1.逻辑函数Y=AB的反函数是(D)

AY’=A’BBY’=AB’CY=(AB)’DA,B,C都是

2..逻辑函数Y1=AB和Y2=A⊙B满足(D)

AY1与Y2互为反函数BY1与Y2互为对偶式

CY1与Y2相等DY1和Y2既互反也对偶

3.n个变量最小项的个数共有(C)

A2nBn乘以nC2的n次方D2的n次方减1

4.使逻辑函数Y=(A+BC’)’(A+B)为1的变量取值是(C)

A001B101C011D111

5.函数Y1=AB+BC+AC与Y2=A’B’+B’C’+A’C’(D)

A互为对偶式B互为反函数C相等DA,B,C都不对

第四章

1、组合逻辑电路的特点是输出状态只于输入信号有关,与电路原有状态无关,其基本单元电路是门电路。

2、编码器按功能的不同分为三种:

二进制编码器、二-十进制编码器、优先编码器。

3、译码器按功能的不同分为三种:

二进制译码器、二-十进制译码器、显示译码器。

4、输入3位二进制代码的二进制译码器应有8个输入端,共输出8个最小项。

5、8选1数据选择器在所有输入数据都为1时,其输出标准与或表示式共有

8个最小项。

6、全加器有三个输入端,它们分别为被加数,加数和相邻低位进数位;

输出端有两个,分别为本位和、进位数。

7、数值比较器的功能是用以比较二组二进制数的大小或相等。

8、在组合逻辑电路中,消除竞争冒险现象的主要方法有:

加选通脉冲、

加封锁脉冲、 输出端接滤波电容 、 修改设计增加冗余项 。

二、判断题(正确的题在括号内填”√”,错误的题填”×

”)

1、门电路是最简单的组合逻辑电路。

(√)

2、组合逻辑电路全部由门电路组成。

(√)

3、数据选择器用以将一个输入数据分配到多个指定输出端上的电路。

(×

)

4、显示译码器CC14547既可用以驱动半导体数码显示器,也可用以驱动液晶显示器。

5、数值比较器是用于比较两组二进制数大小或相等的电路。

6、加法器是用于对两组二进制数进行比较的电路。

7、优先编码器只对多个输入编码信号中优先权最高的信号进行编码。

三、选择题(将正确的答案填入括号内)

1、二—十制编码器的输入信号应有(D)

A、2个B、4个C、8个D、10个

2、输入为n位二进制代码的译码器输出端个数为(C)

A、n2个B、2n个C、2n个D、n个

3、8位串行进位加法器由(A)

A、8个全加器组成B、8个半加器组成

C、4个全加器和4个半加器组成D、16个全加器组成

4、从多个输入数据中选择其中一个输出的电路是(B)

A、数据分配器B、数据选择器C、数值比较器D、编码器

5、能对二进制数进行比较的是(C)

6输出低电平有效的二—十进制译码器输出Y5’=0时它的输入代码为(A)A.0101B、0011C、1001D、0111

第五章自我检测题

一,填空题

1.触发器具有_两个_稳定状态,其输出状态由触发器的___输入信号__和__原有_状态组成。

2.基本RS触发器有_置0_,_置1__,_保持三种可使用的功能。

对于有与非门组成的基本RS触发器,在RD’=1.SD’=0时,触发器保持原状态;

在RD’=1,SD’=1时,触发器_置0_;

在RD’=0时.SD’=1时,触发器_;

不允许RD=0,SD’=0存在,排除这种情况出现的约束条件是__R+S_=1_____.

3.由或非门组成的基本RS触发器在RD=0,SD=1时,触发器___置1___;

在RD=1.SD=0时,触发器_置0__;

在RD=0,SD=0时,触发器保持原状态;

不允许RD=1,SD=1存在,排除这种情况出现的约束条件是_RDSD_=0.

4.边沿JK触发器具有_置0_,_置1_,_保持_,_计数_功能,其特性方程为_Q=JQ+KQ_.对于具有异步置0端RD’和置1端SD’的TTL边沿JK触发器,在RD’=1,SD’=1,要使QN+1=(QN)’时,要求J为_高电平_.K为_高电平_;

如要求QN+1=QN时,则要求J为_低电平_.K为_低电平_;

如要求QN+1=1时,要求J为_高电平_,K为_低电平_;

如要求QN+1=0时,要求J为_低电平_,K为_高电平.

5.维持阻塞D触发器具有_置0_和_置1_功能,其特性方程为_Q=D_.如将输入D和输出Q’相连后,则D触发器处于_计数_状态.

6.特性表用以表示触发器的__次态_和_输入信号_与_现态_之间的关系。

二,判断题

1.一个触发器可保存1位二进制。

(√)

2.由与非门组成的基本RS触发器可用RD’和SD’端输入的信号直接进行置0或置1.(√)

3.上升沿触发器在时钟脉冲CP=1期间,输出状态随信号变化。

4.同步RS触发器在CP=1期间,输出状态随输入R.S端的信号变化。

5.上升沿JK触发器原状态为1,欲使其状态为0时,则在时钟脉冲CP上升沿到来前置J=,K=1.(√ )

6.同步JK触发器在时钟脉冲CP=1期间,J。

K输入信号发生变化时,对输出Q的状态不会有影响。

(×

)

7.边沿JK触发器在时钟CP=1期间,J.K输入信号发生变化时,输出Q的状态随之变化。

(×

)

8.维持阻塞D触发器在输入D=1时,输入时钟脉冲CP上升沿后,触发器只能翻到1状态。

(√)

三,选择题

1,有与非门组成的基本ES触发器在输入RD,和SD’同时由0变1后,触发器的输出状态为(D)

A,0状态 B,1状态 C,状态不变 D,状态不定

2有与非门组成的同步RS触发器在CP=1时,输入R和S信号同时由1变为0时,输出状态为 (D)

A,0状态 B,1状态 C状态不变 D状态不确定

3维持阻塞D触发器在时钟脉冲CP上升沿到来前D=1,而在CP上升沿以后D变为0,则触发器状态为(B)

A,0状态B,1状态C状态不变D状态不确定

4下降触出发的边沿JK触发器在时钟脉冲CP下降沿到来前J=1,K=0,而在CP下降沿到来后变为J=0,K=1,则触发器状态为(B)

A,0状态 B,1状态 C状态不变 D状态不确定

5,4个边沿JK触发器组成的二进制计数器最多能计 (B)

A,0至7个数B,0至15个数C,0至9个数D,0至16个数

6,下降触发器边沿JK触发器CT74LS112的RD’=1,SD’=1,且J=1,K=1时,如时钟脉冲CP输入频率为110KHZ的方波,则Q端输出脉冲的频率为(B)

A,110KHZB,55KHZC,50KHZD,220KHZ

7要将下降沿边沿JK触发器CT74LS112输出Q置为高电平1时,输入为(D)

A,J=1,K=1,RD’=1,SD’=1,输入CP正跃变

B,J=1,K=0,RD’=0,SD’=1,输入CP负跃变

C,J=1,K=1,RD’=1,SD’=1,输入CP负跃变

D,J=1,K=0,RD’=1,SD’=1,输入