段数码显示译码器设计Word文件下载.doc

《段数码显示译码器设计Word文件下载.doc》由会员分享,可在线阅读,更多相关《段数码显示译码器设计Word文件下载.doc(6页珍藏版)》请在冰豆网上搜索。

实验项目名称

7段数码显示译码器设计

指导教师

一、实验目的:

学习7段数码显示译码器设计;

学习VerilogHDL的多层次设计方法。

二、实验内容:

1、实验原理:

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

2、实验步骤:

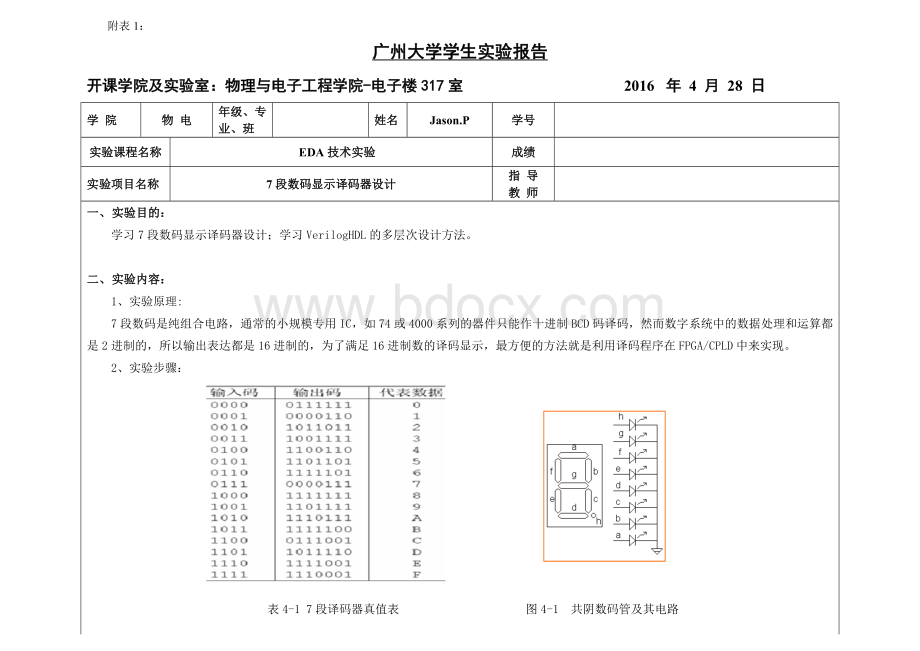

表4-17段译码器真值表图4-1共阴数码管及其电路

(1)首先按7段译码器真值表,完成7段BCD码译码器的设计。

作为7段BCD码译码器,输出信号LED7S的7位分别接如图4-1数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段:

g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;

接有高电平的段发亮,于是数码管显示“5”。

(2)设计该译码器,在QuartusII上对其进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形(提示:

用输入总线的方式给出输入信号仿真数据)。

引脚锁定及硬件测试。

建议选实验电路模式6,用数码8显示译码输出,键8/7/6/5四位控制输入,硬件验证译码器的工作性能。

图4-27段译码器仿真波形

(3)将设计加入4位二进制计数器,经上面设计的16进制7段译码器显示。

图4-3计数器和译码器连接电路原理图

三、实验HDL描述:

计数器:

moduleadder(CLK,RST,EN,LOAD,COUT,DOUT,DATA);

inputCLK,EN,RST,LOAD;

input[3:

0]DATA;

output[3:

0]DOUT;

outputCOUT;

reg[3:

0]Q1;

regCOUT;

assignDOUT=Q1;

always@(posedgeCLKornegedgeRST)//CLK上升沿、RST下降沿触发

begin

if(!

RST)Q1<

=0;

//RST为低电平时,Q1为0

elseif(EN)begin//EN为高电平时,执行下步

LOAD)Q1<

=DATA;

//LOAD为低电平时Q1=DATA

elseif(Q1<

15)Q1<

=Q1+1;

//Q1<

15,计数加1

elseQ1<

=4'

b0000;

end//Q1为其他值,计数置0

end

always@(Q1)

if(Q1==4'

hf)COUT=1'

b1;

elseCOUT=1'

b0;

//Q1为15,COUT=1,否则为0

endmodule

16进制7段译码器:

moduleDECL7S(A,LED7S);

input[3:

0]A;

output[6:

0]LED7S;

reg[6:

always@(A)

case(A)

4'

b0000:

LED7S<

=7'

B0111111;

b0001:

B0000110;

b0010:

B1011011;

b0011:

B1001111;

b0100:

B1100110;

b0101:

B1101101;

b0110:

B1111101;

b0111:

B0000111;

b1000:

B1111111;

b1001:

B1101111;

b1010:

B1110111;

b1011:

B1111100;

b1100:

B0111001;

b1110:

B1111001;

b1111:

B1110001;

default:

endcase

四、仿真结果:

7段数码显示译码器仿真测试结果

A为输入的数,LED7S输出对应的译码结果(与7段译码器真值表一致)

计数器仿真测试结果

含异步清零和同步时钟使能的加法计数器,CLK为上升沿时,DOUT计数(EN=LOAD=RST=1);

EN为低电平时DOUT保持当前数值(LOAD=RST=1);

EN为高电平且CLK为上升沿时触发DOUT计数(LOAD=RST=1)。

LOAD为低电平且CLK为上升沿时,DOUT置为DATA值(EN=RST=1)。

RST为低电平时,DOUT置为0,与CLK是否为上升沿无关。

DOUT值计满15时COUT置1,DOUT为其他值时COUT为0。

组合电路(计数器+译码器)仿真测试结果

计数器和译码器连接的电路,led的译码输出和真值表相符合。

en为低电平且clock为上升沿时led保持,en为高电平且clock为上升沿时led显示的数字加一。

load为低电平且clock为上升沿时,led显示data的数值。

rst为低电平时,led显示数字0,与clock上升沿时间无关。

Led显示到数字15时cout为1,led显示其他数值时,cout为0。

五、引脚锁定:

六、硬件测试结果:

模式6:

en(键8控制)为低电平,保持显示数字3计数满15(显示为F)LED-D8(cout)亮rst(键7控制)为低电平,清零

七、实验心得:

通过本次实验,对QuartusII有了进一步的学习和认识,对Verilog也有了深入了解。

学会了7段数码显示译码器的Verilog硬件设计,学习了VHDL的CASE语句应用及多层次设计方法。

实验中,要对每一个功能模块做时序仿真,检验是否符合设计需求,最后综合起来做仿真测试,确认无误后再下载到目标机上进行硬件测试。

做实验时要耐心、认真,遇到问题争取自己解决,这样才能锻炼自己,提升自己。

说明:

各学院(实验中心)可根据实验课程的具体需要和要求自行设计和确定实验报告的内容要求和栏目,但表头格式按照“实验项目名称”栏以上部分统一。