微机原理与接口技术(楼顺天第二版)第六章习题解答Word格式.doc

《微机原理与接口技术(楼顺天第二版)第六章习题解答Word格式.doc》由会员分享,可在线阅读,更多相关《微机原理与接口技术(楼顺天第二版)第六章习题解答Word格式.doc(7页珍藏版)》请在冰豆网上搜索。

6.3答:

在选择存储器芯片时应注意是否与微处理器的总线周期时序匹配。

作为一种保守的估计,在存储器芯片的手册中可以查得最小读出周期tcyc(R)(ReadCycleTime)和最小写周期tcyc(W)(WriteCycleTime)。

如果根据计算,微处理器对存储器的读写周期都比存储器芯片手册中的最小读写周期大,那么我们认为该存储器芯片是符合要求的,否则要另选速度更高的存储器芯片。

8086CPU对存储器的读写周期需要4个时钟周期(一个基本的总线周期)。

因此,作为一种保守的工程估计,存储器芯片的最小读出时间应满足如下表达式:

tcyc(R)<4T-tda-tD-T

其中:

T为8086微处理器的时钟周期;

tda为8086微处理器的地址总线延时时间;

tD为各种因素引起的总线附加延时。

这里的tD应该认为是总线长度、附加逻辑电路、总线驱动器等引起的延时时间总和。

同理,存储器芯片的最小写入时间应满足如下表达式:

tcyc(W)<4T-tda―tD―T

6.4答:

全地址译码、部分地址译码和线选。

全地址译码方式下CPU地址总线的所有地址均参与存储单元的地址译码,存储单元地址唯一;

部分地址译码方式和线选方式下CPU地址总线的有一些地址信号没有参与译码,则取0或取1均可,所以存储器的存储单元地址不唯一,有重复。

6.5答:

数据总线的低8位接偶存储体,高8位接奇存储体;

地址总线的A19~A1同时对奇偶存储体寻址,地址总线的A0只与偶地址存储体连接,与奇地址存储体连接。

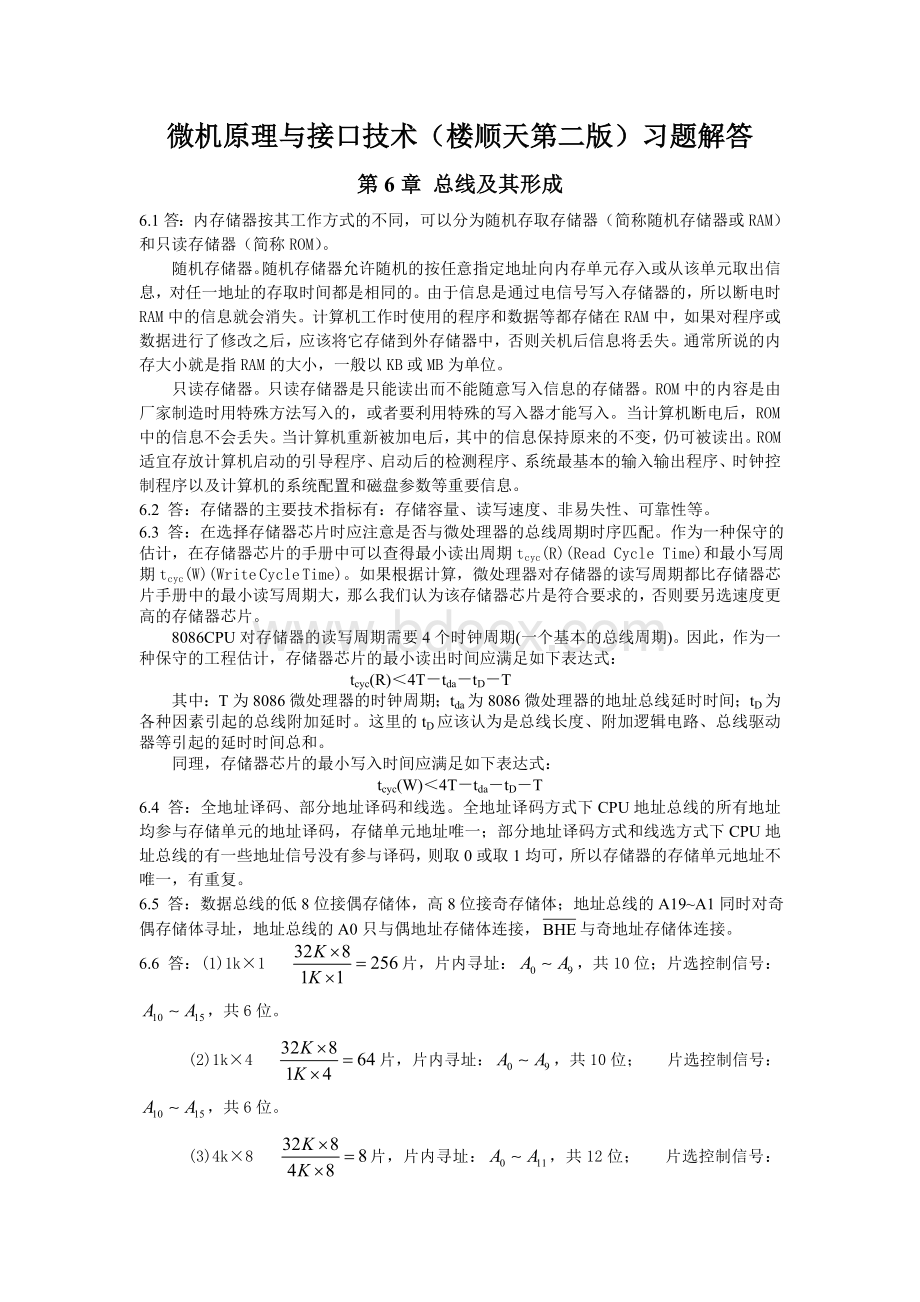

6.6答:

(1)1k×

1片,片内寻址:

,共10位;

片选控制信号:

,共6位。

(2)1k×

4片,片内寻址:

片选控制信号:

(3)4k×

8片,片内寻址:

,共12位;

,共4位。

(4)16k×

4片,片内寻址:

,共14位;

,共2位。

6.7答:

,共10位。

,共8位。

6.8答:

32K==8000H,所以,最高地址为:

4000H+8000H-1=BFFFH,则,可用的最高地址为0BFFFH.

6.9答:

7FFFH-4000H+1=4000H==16KB,内存容量为16KB。

6.10答:

因为6264的片容量为8KB。

RAM存储区域的总容量为03FFFH-00000H+1=4000H=16KB,故需要2片6264芯片。

连接图如图6.10所示。

图6.10与8088系统总线的连接图

检测程序段:

MOVAX,0000H

MOVDS,AX

MOVSI,0

MOVCX,16*1024

MOVAL,55H

CMPL:

MOV[SI],AL

MOVBL,[SI]

CMPBL,AL

JNEERROR

INCSI

LOOPCMPL

MOVDL,0EEH

JMPNEXT

ERROR:

MOVDL,01H

NEXT:

…

6.11答:

EPROM芯片的编程有两种方式:

标准编程和快速编程。

在标准编程方式下,每给出一个编程负脉冲就写入一个字节的数据。

Vpp上加编程电压,地址线、数据线上给出要编程单元的地址及其数据,并使=0,=1。

上述信号稳定后,在端加上宽度为50ms±

5ms的负脉冲,就可将数据逐一写入。

写入一个单元后将变低,可以对刚写入的数据读出进行检验。

快速编程使用100的编程脉冲依次写完所有要编程的单元,然后从头开始检验每个写入的字节。

若写的不正确,则重写此单元。

写完再检验,不正确可重写。

EEPROM编程时不需要加高电压,也不需要专门的擦除过程。

并口线EEPROM操作与SRAM相似,写入时间约5ms。

串行EEPROM写操作按时序进行,分为字节写方式和页写方式。

6.12答:

8088最大方式系统与存储器读写操作有关的信号线有:

地址总线,数据总线:

,控制信号:

。

根据题目已知条件和74LS138译码器的功能,设计的板内数据总线驱动电路如图6.12(a)所示,板内存储器电路的连接电路图如图6.12(b)所示。

图6.12(a)板内数据总线驱动电路

图6.12(b)板内存储器电路的连接图

6.13答:

Intel2764的片容量为8KB,而题目给出的地址共32KB,说明有4个地址区重叠,即采用部分地址译码时,有2条高位地址线不参加译码(即不参加译码)。

地址译码电路及2764与总线的连接如图6.13所示。

图6.13地址译码电路及2764与总线的连接

6.14答:

2K×

8的Intel6116SRAM芯片有11个地址引脚,8个数据引脚,现形成4KB的存储器,则需要两块6116的芯片进行字节扩展。

2000H~3FFFH有8KB,所以必定有地址重叠,应该采用部分地址译码方式。

根据地址范围,A15~A13必为001,A12与A11使用一个进行片选译码。

在图中A11没有参与译码,当A15~A11为00100或00101时会选中上面的6116芯片,所以上面6116芯片的地址范围为:

2000H~2FFFH;

当A15~A11为00110或00111时会选中下面的6116芯片,所以下面6116芯片的地址范围为:

3000H~3FFFH。

6.15答:

(1)00000H~01FFFH为8KB,03000H~03FFFH为4KB,所以需要6个4K×

4的ROM芯片,共3组。

(2)

6.16答:

(1)70000H~7BFFFH有0C000H字节,即48KB,根据题图,给出的SRAM芯片为16K×

8。

所以需要3片存储芯片;

(2)3个芯片的地址范围分别为:

70000H~73FFFH,74000H~~77FFFH,78000H~7BFFFH;

(3)

6.17答:

程序如下:

STARTADDR=2000H

CHECKNUM=9000H

CODESEGMENT

ASSUMECS:

CODE

START:

MOVAX,0;

将数据段段地址寄存器DS设为0000H

MOVDS,AX

MOVBX,STARTADDR

MOVCX,CHECKNUM

MOVDX,0;

用DX来计出错内存单元的个数

MOVSI,1000H;

用SI进行出错字节单元地址存储寻址

XH:

MOVAL,55H

MOV[BX],AL;

写入

CMP[BX],AL;

读出,比较

JNZERROR

MOVAL,0AAH

MOV[BX],AL

CMP[BX],AL

JNZERROR

JMPRIGHT

INCDX;

出错字节单元数增1

MOV[SI],BX;

将出错字节单元的地址存入1000H开始的缓冲区

INCSI

INCSI

RIGHT:

INCBX

LOOPXH

HLT

CODEENDS

ENDSTART

6.18答:

73FFFH-70000H+1=4000H=16K。

ntel6264的片容量为8KB,RAM存储区总容量为16KB,故需要2片6264。

8086最小方式系统与存储器读写操作有关的信号线有:

此SRAM电路与8086系统总线的连接图如图6.18所示。

图6.18SRAM电路与8086系统总线的连接图

6.19答:

28C16的引脚功能:

lVCC,GND:

电源和地

l:

11位地址线,可寻址2KB地址空间

8位数据线

写允许,低电平有效。

输出允许,低电平有效。

片选信号,低电平有效。

根据所学知识,28C16与8088系统的连接图如图6.19所示。

图6.1928C16与8088系统的连接图