哈工大数字电子技术基础习题册答案67章Word下载.docx

《哈工大数字电子技术基础习题册答案67章Word下载.docx》由会员分享,可在线阅读,更多相关《哈工大数字电子技术基础习题册答案67章Word下载.docx(14页珍藏版)》请在冰豆网上搜索。

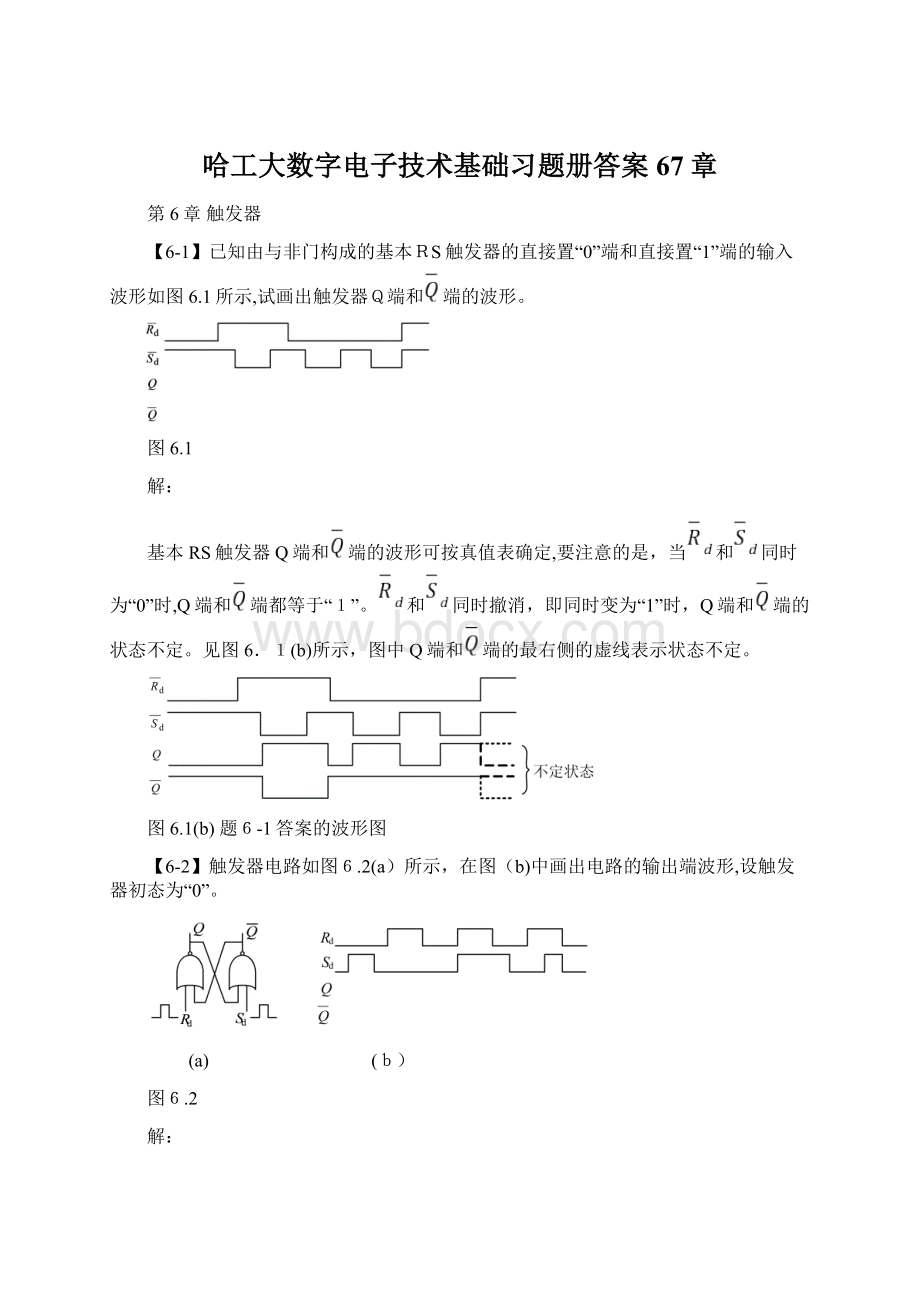

【6-4】分析图6.4所示电路,列出真值表,写出特性方程,说明其逻辑功能。

图6.4

1.真值表(CP=0时,保持;

CP=1时,如下表)

2.特性方程Qn+1=Dn

3.该电路为锁存器(时钟型D触发器)。

CP=0时,不接收D的数据;

CP=1时,把数据锁存,但该电路有空翻。

【6-5】试画出在图6.5所示输入波形的作用下,上升和下降边沿JK触发器的输出波形。

设触发器的初态为“0”。

图6.5

解:

见图6.5(b)所示。

图6.5(b)

【6-6】试画出图P6.6(a)所示电路,在图6.6(b)给定输入下的Q端波形,设触发器初态为“0”。

(a) (b)

图6.6

见图6.6(b)所示。

图6.6(b)

【6-7】根据特性方程,外加与非门将D触发器转换为JK触发器,应如何实现?

若反过来将JK触发器转换为D触发器,应如何实现?

J-K触发器特性方程

D触发器特性方程

D触发器转换为J-K触发器 如图6.7(a)所示。

J-K触发器转换为D触发器, 如图6.7(b)所示。

(a) (b)

图6.7

【6-8】电路如图6.8(a)所示,触发器为维持阻塞型D触发器,各触发器初态均为“0”。

1.在图(b)中画出CP作用下的Q0Q1和Z的波形;

2.分析Z与CP的关系。

(a) (b)

图6.8

1、CP作用下的输出Q0Q1和Z的波形如下图;

2、Z对CP三分频。

【6-9】电路如图6.9(a)所示,试在图(b)中画出给定输入波形作用下的输出波形,各触发器的初态均为“0”;

根据输出波形,说明该电路具有什么功能?

(a)

(b)

图6.9

输出波形图见图6.9(c)

图6.9(c)

【6-10】电路如图6.10所示,试在图(b)中画出给定输入波形作用下输出端Q0和Q1的波形,设各触发器的初态均为“0”。

(a) (b)

图6.10

输出波形图见图6.10(c)

图6.10(c)

【6-11】电路如图6.11所示,试在图(b)中画出给定输入波形作用下输出端Q0 和Q1波形,各触发器的初态均为“0”。

(a) (b)

图6.11

见图6.11(b)所示。

该电路A输入每出现一次下降沿,Q1端就输出一个宽度等于时钟周期的脉冲。

图6.11(b)

第7章时序逻辑电路

【7-1】已知时序逻辑电路如图7.1所示,假设触发器的初始状态均为0。

(1)写出电路的状态方程和输出方程。

(2)分别列出X=0和X=1两种情况下的状态转换表,说明其逻辑功能。

(3)画出X=1时,在CP脉冲作用下的Q1、Q2和输出Z的波形。

图7.1

1.电路的状态方程和输出方程

2.分别列出X=0和X=1两种情况下的状态转换表,见题表7.1所示。

逻辑功能为

当X=0时,为2位二进制减法计数器;

当X=1时,为3进制减法计数器。

3.X=1时,在CP脉冲作用下的Q1、Q2和输出Z的波形如图7.1(b)所示。

题表7.1

X=0

X=1

Q2Q1

Q2 Q1

00

0 0

11

1 0

1 0

01

0 1

00

0 0

图7.1(b)

【7-2】电路如图7.2所示,假设初始状态QaQbQc=000。

(1)写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2)试分析该电路构成的是几进制的计数器。

图7.2

1.写出驱动方程

2.写出状态方程

3.列出状态转换表见题表7.2,状态转换图如图7.2(b)所示。

4.由FFa、FFb和FFc构成的是六进制的计数器。

【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q或)填入下表

触发方式

计数器类型

加法计数器

减法计数器

上升沿触发

由( )端引出进位

由()端引出借位

下降沿触发

由()端引出进位

由( )端引出借位

题表7-3

【7-4】电路如图7.4(a)所示,假设初始状态Q2Q1Q0=000。

1.试分析由FF1和FF0构成的是几进制计数器;

2. 说明整个电路为几进制计数器。

列出状态转换表,画出完整的状态转换图和CP

作用下的波形图。

(a) (b)

图7.4

1、由FF1和FF0构成的是三进制加法计数器(过程从略)

2、整个电路为六进制计数器。

状态转换表(略),完整的状态转换图

和CP作用下的波形图如下图。

【7-5】某移位寄存器型计数器的状态转换表如表7.5所示。

请在图7.5中完成该计数器的逻辑图,可以增加必要的门电路。

要求:

写出求解步骤、画出完整的状态转换图。

(Q3为高位)

表7.6

图7.5

(1)根据状态转换表画次态卡诺图,求出状态方程。

;

;

(2)由状态方程写驱动方程。

;

;

;

【7-6】在图7.6(a)所示电路中,由D触发器构成的六位移位寄存器输出Q6Q5Q4 Q3Q2 Q1的初态为010100,触发器FF的初态为0,串行输入端DSR=0。

请在图7.6(b)中画出A、Q及B的波形。

(a) (b)

图7.6

波形图如图7.6(b)所示。

图7.6(b)

【7-7】分析图7.7所示电路,说明它们是多少进制计数器?

(a) (b)

图7.7

图(a),状态转换顺序[QDQCQBQA]=0→1→2→3→4→5→6→0,是7进制计数器;

图(b),[QDQCQBQA]=6→7→8→9→10→11→12→13→14→15→6,是10进制计数器;

【7-8】分析图7.8所示电路的工作过程

1.画出对应CP的输出QaQdQcQb的波形和状态转换图(采用二进制码的形式、

Qa为高位)。

2.按QaQdQcQb顺序电路给出的是什么编码?

3.按QdQcQbQa顺序电路给出的编码又是什么样的?

图7.8

1 状态转换图为

2按QaQdQcQb顺序电路给出的是5421码。

3.按QdQcQbQa顺序电路给出的编码如下

0000→0010→0100→0110→1000→0001→0011→0101→0111→1001→0000

【7-10】试用2片4位二进制计数器74LS160采用清零法和置数法分别实现31进制加法计数器。

答案略。

【7-9】图7.9为由集成异步计数器74LS90、74LS93构成的电路,试分别说明它

们是多少进制的计数器。

(a) (b)

(c)

图7.9

解:

图(a),状态转换顺序[QDQCQB]=0→1→2→0,是3进制计数器;

图(b),状态转换顺序[QDQCQB]=0→1→2→3→0,是4进制计数器;

图(c),是37进制计数器。

【7-11】图7.12所示为一个可变进制计数器。

其中74LS138为3线/8线译码器,当S1=1且时,进行译码操作,即当A2A1A0从000到111变化时,依次被选中而输出低电平。

74LS153为四选一数据选择器。

试问当MN为各种不同取值时,可组成几种不同进制的计数器?

简述理由。

图7.11

4个JK触发器构成二进制加法计数器,当计数到[Q4Q3Q2Q1]=10000时,74LS138满足使能条件,对[Q3Q2Q1]的状态进行译码,译码器的输出Y经过4选1数据选择器74LS153,在[MN]的控制下,被选中的Y信号,以低电平的形式对计数器清零。

不同的[MN]即可改变图7.11所示电路的计数进制,具体见下表。

MN

进制

0 0

八

0 1

九

1 0

十四

1 1

十五