控制器部分习题解答Word格式.doc

《控制器部分习题解答Word格式.doc》由会员分享,可在线阅读,更多相关《控制器部分习题解答Word格式.doc(10页珍藏版)》请在冰豆网上搜索。

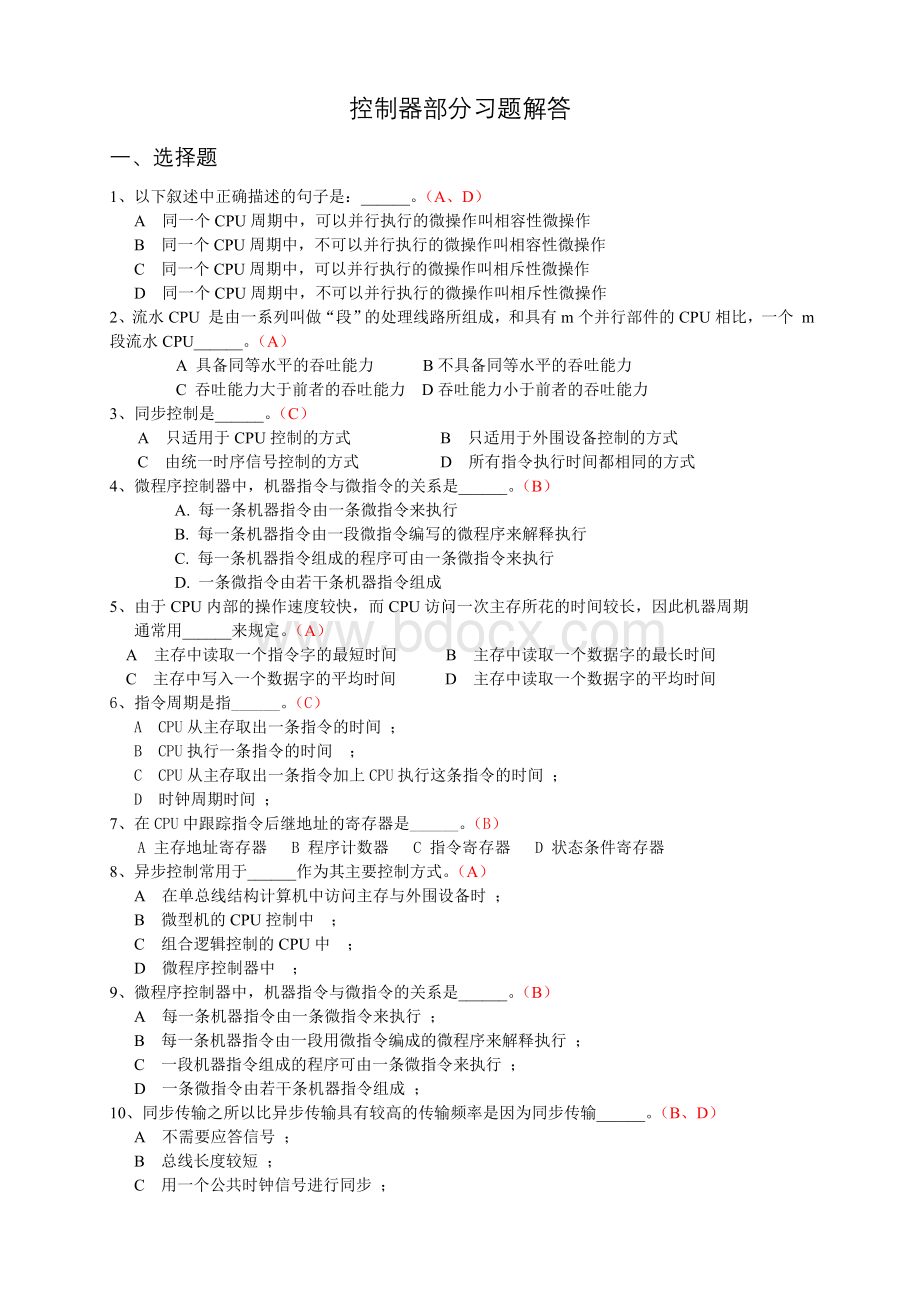

4、微程序控制器中,机器指令与微指令的关系是______。

(B)

A.每一条机器指令由一条微指令来执行

B.每一条机器指令由一段微指令编写的微程序来解释执行

C.每一条机器指令组成的程序可由一条微指令来执行

D.一条微指令由若干条机器指令组成

5、由于CPU内部的操作速度较快,而CPU访问一次主存所花的时间较长,因此机器周期

通常用______来规定。

A主存中读取一个指令字的最短时间B主存中读取一个数据字的最长时间

C主存中写入一个数据字的平均时间D主存中读取一个数据字的平均时间

6、指令周期是指______。

ACPU从主存取出一条指令的时间;

BCPU执行一条指令的时间;

CCPU从主存取出一条指令加上CPU执行这条指令的时间;

D时钟周期时间;

7、在CPU中跟踪指令后继地址的寄存器是______。

A主存地址寄存器B程序计数器C指令寄存器D状态条件寄存器

8、异步控制常用于______作为其主要控制方式。

A在单总线结构计算机中访问主存与外围设备时;

B微型机的CPU控制中;

C组合逻辑控制的CPU中;

D微程序控制器中;

9、微程序控制器中,机器指令与微指令的关系是______。

A每一条机器指令由一条微指令来执行;

B每一条机器指令由一段用微指令编成的微程序来解释执行;

C一段机器指令组成的程序可由一条微指令来执行;

D一条微指令由若干条机器指令组成;

10、同步传输之所以比异步传输具有较高的传输频率是因为同步传输______。

(B、D)

A不需要应答信号;

B总线长度较短;

C用一个公共时钟信号进行同步;

D各部件存取时间较为接近;

11、在某CPU中,设立了一条等待(WAIT)信号线,CPU在存储器周期中T的φ的下降沿采样WAIT线,请在下面的叙述中选出正确描述的句子:

(C、D)

A如WAIT线为高电平,则在T2周期后不进入T3周期,而插入一个TW周期;

BTW周期结束后,不管WAIT线状态如何,一定转入了T3周期;

CTW周期结束后,只要WAIT线为低,则继续插入一个TW周期,直到WAIT线变高,才转入T3周期;

D有了WAIT线,就可使CPU与任何速度的存贮器相连接,保证CPU与存贮器连接时的时序配合;

12、操作控制器的功能是______。

(D)

A.产生时序信号B.从主存取出一条指令C.完成指令操作的译码

D.从主存取出指令,完成指令操作码译码,并产生有关的操作控制信号,以解释执行该指令

13、描述流水CPU基本概念不正确的句子是______。

(ABC)

A.流水CPU是以空间并行性为原理构造的处理器

B.流水CPU一定是RISC机器

C.流水CPU一定是多媒体CPU

D.流水CPU是一种非常经济而实用的时间并行技术

14、带有处理器的设备一般称为______设备。

A.智能化B.交互式C.远程通信D.过程控制

二、填空题

1、微程序设计技术是利用A.______方法设计B.______的一门技术。

具有规整性、可维护性、C.______等一系列优点。

(A.软件B.操作控制C.灵活性)

2、硬布线器的设计方法是:

先画出A.______流程图,再利用B.______写出综合逻辑表达式,然后用C.______等器件实现。

(A.指令周期B.布尔代数C.门电路和触发器)

3、CPU从A.______取出一条指令并执行这条指令的时间和称为B.______。

由于各种指

令的操作功能不同,各种指令的指令周期是C.______。

(A.存储器B.指令周期C.不相同的)

4、当今的CPU芯片除了包括定点运算器和控制器外,还包括A.______,B.______运算器和C.______管理等部件。

(A.CacheB.浮点C.存储)

5、流水CPU是以A.______为原理构造的处理器,是一种非常B.______的并行技术。

目前的C.______微处理器几乎无一例外的使用了流水技术。

(A.时间并行性B.经济而实用C.高性能)

6、CPU中至少有如下六类寄存器,除了A.______寄存器,B.______计数器,C.______寄存器外,还应有通用寄存器,状态条件寄存器,数据缓冲寄存器。

(A.指令B.程序C.地址)

7、硬布线控制器的基本思想是:

某一微操作控制信号是A.______译码输出,B.______信号和

C.______信号的逻辑函数.(A.指令操作码B.时序C.状态条件)

8、CPU周期也称为A.______;

一个CPU周期包含若干个B.______。

任何一条指令的指令周期至少需要C.______个CPU周期。

(A.机器周期B.时钟周期C.2)

9、RISCCPU是克服CISC机器缺点的基础上发展起来的,它具有的三个基本要素是:

(1)一个有限的A.______;

(2)CPU配备大量的B.______;

(3)强调C.______的优化。

(A.简单指令系统B.通用寄存器C.指令流水线)

10、CPU从A______取出一条指令并执行这条指令的时间和称为B______。

由于各种指令的操作功能不同,各种指令的时间和是不同的,但在流水线CPU中要力求做到C______。

(A.存储器B.指令周期C.一致)

11、CPU中,保存当前正在执行的指令的寄存器为A______,保存当前正在执行的指令的地址的寄存器为B______,保存CPU访存地址的寄存器为C______。

(A.指令寄存器IRB.程序计数器PCC.内存地址寄存器AR)

12、并行处理技术已经成为计算机发展的主流。

它可贯穿于信息加工的各个步骤和阶段概括起来,主要有三种形式:

A______并行;

B______并行;

C______并行。

(A.时间B.空间C.时间+空间)

三、应用题

1、(11分)已知某机采用微程序控制方式,其存储器容量为512×

48(位),微程序在整个控制存储器中实现转移,可控制微程序的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式,如图所示:

微命令字段判别测试字段下地址字段

←操作控制→←——————顺序控制————————→

(1)微指令中的三个字段分别应多少位?

(2)画出对应这种微指令格式的微程序控制器逻辑框图。

解:

(1)假设判别测试字段中每一位为一个判别标志,那么由于有4个转移条件,故该字段为4位,(如采用字段译码只需3位),下地址字段为9位,因为控制容量为512单元,微命令字段是(48–4-9)=35位。

(2)对应上述微指令格式的微程序控制器逻辑框图B1.2如下:

其中微地址寄存器对应下地址字段,P字段即为判别测试字段,控制字段即为微命令子段,后两部分组成微指令寄存器。

地址转移逻辑的输入是指令寄存器OP码,各状态条件以及判别测试字段所给的判别标志(某一位为1),其输出修改微地址寄存器的适当位数,从而实现微程序的分支转移。

图B1.2

2、(11分)假设某计算机的运算器框图如图B2.2所示,其中ALU为16位的加法器(高电平工作),SA、SB为16位锁存器,4个通用寄存器由D触发器组成,O端输出,其读写控制如下表所示:

W

WA0

WA1

选择

1

0

0

1

x

x

R0

R1

R2

R3

不写入

写控制读控制

RA0

RA1

R0

R1

R2

R3

不读出

图B2.2

要求:

(1)设计微指令格式。

(2)画出ADD,SUB两条微指令程序流程图。

各字段意义如下:

F1—读RO—R3的选择控制。

F2—写RO—R3的选择控制。

F3—打入SA的控制信号。

F4—打入SB的控制信号。

F5—打开非反向三态门的控制信号LDALU。

F6—打开反向三态门的控制信号LDALU,并使加法器最低位加1。

F7-锁存器SB清零RESET信号。

F8-一段微程序结束,转入取机器指令的控制信号。

R—寄存器读命令

W—寄存器写命令

(2)ADD、SUB两条指令的微程序流程图见图B2.3所示。

图B2.3

3、(11分)图B3.1所示的处理机逻辑框图中,有两条独立的总线和两个独立的存贮器。

已知指令存贮器IM最大容量为16384字(字长18位),数据存贮器DM最大容量是65536字(字长16位)。

各寄存器均有“打入”(Rin)和“送出”(Rout)控制命令,但图中未标出。

图B3.1

设处理机格式为:

171090

OP

X

加法指令可写为“ADDX(R1)”。

其功能是(AC0)+((