CSP芯片规模装配的可靠性Word文档下载推荐.docx

《CSP芯片规模装配的可靠性Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《CSP芯片规模装配的可靠性Word文档下载推荐.docx(9页珍藏版)》请在冰豆网上搜索。

CSP和倒装芯片(flip-chip)包装的用量上的增加是相同的。

估量在2006年达到60亿。

相反,在相同十年里BGA的增加估量是最小的,达到只有15亿的总用量。

对BGA的估量说明也许这些包装只是一个踏步石,工业将更广泛地同意倒装芯片(flipchip)和芯片规模包装(CSP),因为它们更好地满足小型化应用的要求。

什么缘故采纳芯片规模包装(CSP)?

CSP的显现提供裸芯片(baredie)与倒装芯片(flipchip)的性能与小型的优势,具有标准芯片包装的优点。

CSP设计成比芯片模(die)面积或周长大1.2~1.5倍的包装。

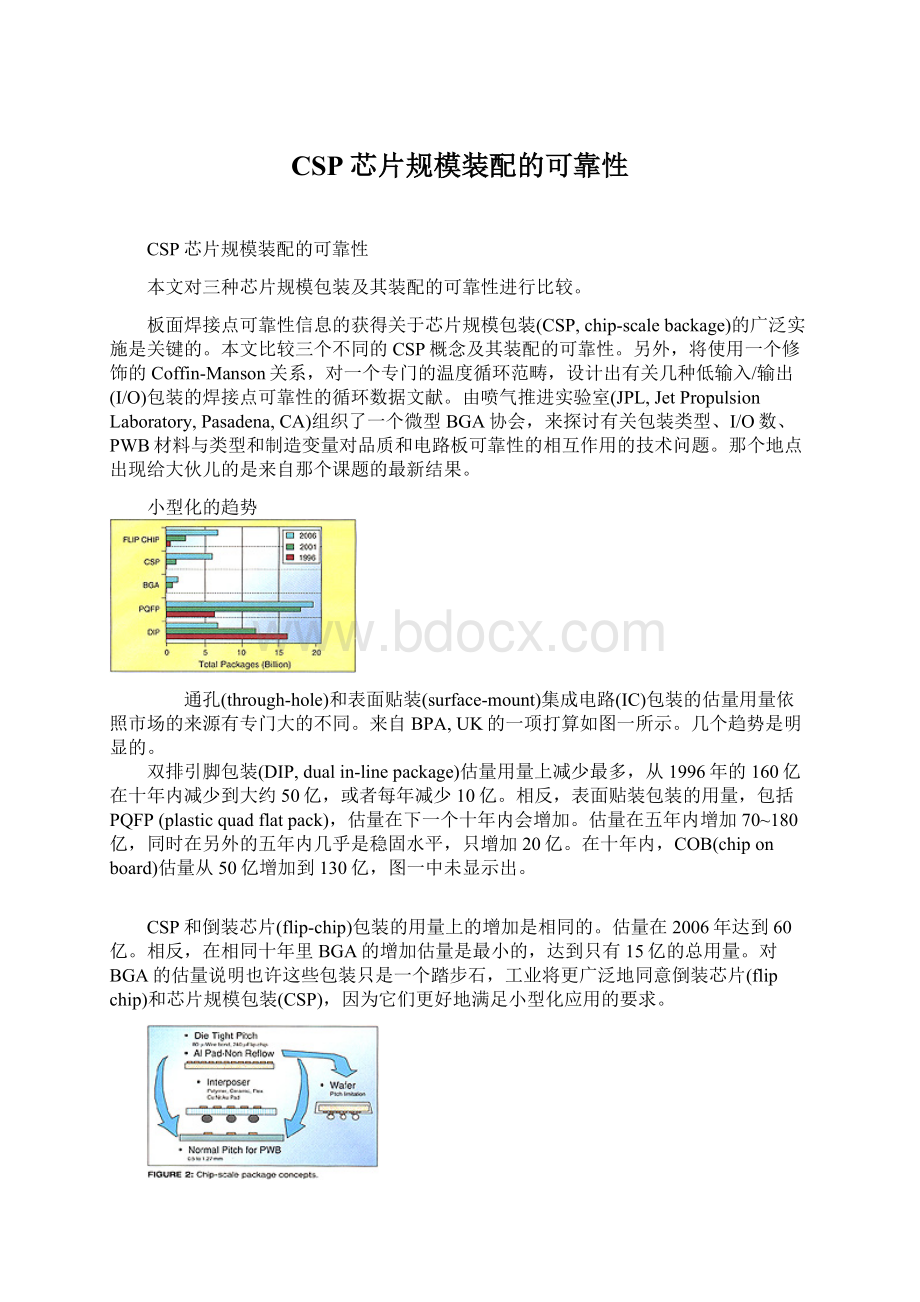

图二说明CSP的两个概念,包括具有1)柔性或刚性内插器和2)圆片级(wafer-level)成型与装配再分布的两种包装。

包装达到如下的目的:

∙为回流焊接装配工艺提供与印刷线路板(PWB)焊盘冶金兼容的锡球和引脚。

∙重新把芯片模(die)紧密的间距分配成在PWB制造规范之内的间距水平。

由于小尺寸,不承诺重大的重新分配;

现在的低成本PWB制造限制了该技术的全面采纳,专门是高输入输出(I/O)数。

∙

∙防止芯片模的物理和阿尔发射线(alpharadiation)损坏,提供散热的载体。

∙使芯片模功能测试容易。

微型BGA的自我对中(Self-Alignment)

如图三所示,用输入输出(I/O)的可扩展性和制造的牢固性,CSP可分类成栅格阵列和引脚型(无引脚型)。

列出了每个类型的要紧优点/缺点。

密间距(finepitch)栅格阵列可接纳更高的引脚数,与BGA类似,它们具有自我对中特性。

对BGA,包装贴装要求的放松差不多广泛地认为与传统的表面贴装包装比较减少了焊接点的缺陷。

阻碍自我对中的要紧因素是熔化的焊锡表面张力,它提供在包装上到焊盘的拉力。

反作用力是包装的重量。

对PBGA,从共晶锡球产生的拉力大于来自陶瓷BGA(CBGA)的部分熔化焊接点或者传统包装的锡膏熔化的力。

因此,PBGA具有更好的自我对中。

BGA锡球分布的对称性进一步承诺对BGA的X和Y和旋转位移。

关于栅格式CSP,熔化的表面张力比BGA小得多,因为它们具有较低的锡球量。

那个较小的表面张力,配合CSP较密的间距,可能阻碍自我对中表现,专门关于重的包装。

CSP可能要求比50-mil间距的BGA更紧的贴装精度。

∙栅格CSP显示有自我对中,然而在最好的偏移限制上存在不和谐:

∙关于46个I/O的栅格CSP,只有25%的偏移是可同意的。

可同意的偏移关于PBGA是62%,关于CBGA是50%。

[Noreika,SurfaceMountInternational(SMI),1997]

∙另一个研究者报告一个80%的偏移。

(Patridge,SMI1997)

∙据说在16,100个焊接点中只有两个锡桥,是由于外来材料,没有来自贴装不准确的缺陷。

该试验是一个定性研究,其中300个46I/O的CSP是手放的,回流;

然后刻画焊点缺陷(Bauer,etal,SMI1997)。

∙在装配有44I/O的CSP包装的200个装配中,只检查到两个焊接点短路(Hunter,atal,CHIPCON1998)。

∙当JPL领导的微型BGA协会装配30个试验载体(每个载体都有四个46I/O的CSP)时,没有观看到缺陷。

∙当八个具有160I/O的CSP有0.2mm的偏移时,没有观看到缺陷。

那个是针对0.45~0.23mm直径的焊盘布局(IMAPS,1997,p.256)。

微电子装配的可靠性

在包装附着中一个要紧的损坏根源是改变系统温度。

当系统没有使用时就关闭电源造成更多的循环。

往常,电子硬件通常长期地保持有点,其结果是相对少的温度循环,引起对由温度循环阻碍的焊接点的关注。

对焊接点的损坏最通常是由下面因素引起的:

∙包装与板之间总的温度膨胀系数(CTE,coefficientofthermalexpansion)不匹配,引起应力。

包装和板也可能在厚度上和表面积上有温度梯度。

∙在元件与PWB焊锡附着之间的局部的CTE不匹配。

减少元件与PWB的CTE不匹配可减少循环损坏,然而理想的条件决定于元件、PWB和焊锡的温度条件。

具有比元件的CTE略微较高的、CTE通过修整的PWB材料可能是理想的,因为,通常,总的CTE不匹配占上风,有热源芯片模的元件比PWB较热。

还有其它方法用来减少对焊接点的损坏。

底部充胶(underfill)的应用是一个常见的技术,广泛用于板上芯片的直截了当附着或者当包装的引脚不牢固时。

其它不太传统的方法目的是要在包装内吸取芯片模(die)与板之间的CTE不匹配,或者外部地通过应力吸取机构,减少焊锡连接上的应力。

这些方法可能引起它们本身专门的损坏,因为最脆弱的连接现在从焊锡转移到附着系统的其它区域。

CSP装配的可靠性

表一分类了三个级别包装的装配可靠性。

它包括对柔性或刚性内插件(interposer)的包装和圆片级包装(wafer-level)的可靠性试验数据。

其失效机制的循环条件方面总结如下。

表一、CSP装配可靠性的数据

包装类型简图

(不按比例)

循环条件

总循环数

失效/样品

I/O数

参考(说明)

-196~160°

C

-65~150°

-55~125°

5.8周期/小时

130

1163

750

1000

无充胶

**500

600

0/3

0/46

0/78

4/78*

1/8

3/8

188

46

40

DiStefano,T.,Fjelstad,J.(1996,April).Chip-scalepackagingmeetsfuturedesignneeds.SolidStateTechnology.

Greathouse,S.(Feb.1997).Chip-scalepackagesolutions-Thepro'

sandcons.ProceedingsofSecondInternationalConferenceonChip-ScalePackaging.CHIPCON'

97.

*4/78rightafter1,000cyclesinlead

Lall,P.(May1998).Assemblylevelreliabilitycharacterizationofchip-scalepackages.48thElectronicComponent&

TechnologyConference.

**InternalTABfailure.

0~100°

(温度冲击)

>

2000

充胶

<

40

无充胶

NA

266

Chanchani,R.,atal.(May1997).Miniball-gridarray(mBGA)assemblyonMCM-Lboards.ProceedingsofElectronicComponentsandTechnologyConference.

-40~125°

~600*

PWB0.6mm

900*

PWB1.6mm

220

Ianzone,R.(Feb.1997).CeramicCSP:

Alowcost,adptiveinterconnect,highdensitytechnology.ProceedingsofSecondInternationalConferenceonChip-ScalePackaging,CHIPCON.

*PrivateCommunication

温度膨胀系数通过吸取的(CTE-absorbed)CSP

表一显示了关于一个CTE不匹配通过开释的包装的温度循环试验结果。

该包装使用象IC内部连接一样的TAB(tape-automated-bond),一个有弹性的内连器和共晶锡球。

那个与TAB内连接的弹性关联的有弹性的内连器减少芯片[CTE2~3ppm(partspermillion)/°

C]与PWB[FR-4的CTE4~15ppm/°

C]之间的温度膨胀差别。

这种包装差不多显示其可靠性和稳固性,无需底部充胶。

在表一中的温度循环/冲击是针对FR-4上的链型包装,是从液态氮温度(-196°

C)到热油(160°

C)温度范畴内进行的。

由于焊接点的低应力状态,没有观看到焊接点的疲劳失效机制,失效转移到具有高不匹配应力水平的TAB内连接的脚跟部分。

当使用柔软的金引脚时,发觉有重要的改善。

在-65°

C~150°

C范畴内循环高达2,000次,金质的没有显示失效。

与在极度低温与高温下装配暴露有关的温度循环屏蔽试验结果是不现实的,因此,它们的失效机制可能对现场失效(fieldfailure)不具代表性。

由于极度高温暴露,一个这种失效是接近玻璃态转化温度(Tg),或者聚合材料开始变软的温度时,FR-4的扩孔和变形。

假如温度变得接近或超过Tg,那么PWB材料显示严峻的损坏。

C到150°

C温度循环范畴内,FR-4电镀通孔(through-hole)发觉有大量的内孔爆裂失效。

表一也包括来自两个用户的最新结果。

失效的循环数比那个包装的供应商提供的少得多。

来自英特尔(Intel)1997年底发表的数据也显示那个包装失效的循环数比来自摩托罗拉1998年五月发表的较高。

前一个研究者被认为是有一个受控的元件包装供应商,而后者的包装来自不同的品排。

极度的CTE不匹配

对一个圆片重新分配(wafer-redistributed)包装的装配的温度循环试验结果在表一中显示。

在那个包装中,一个薄片金属/聚合物重新分配锡球在芯片上的位置,以保证这些与表面贴装脚印兼容。

那个包装类型的高度因为从裸芯片