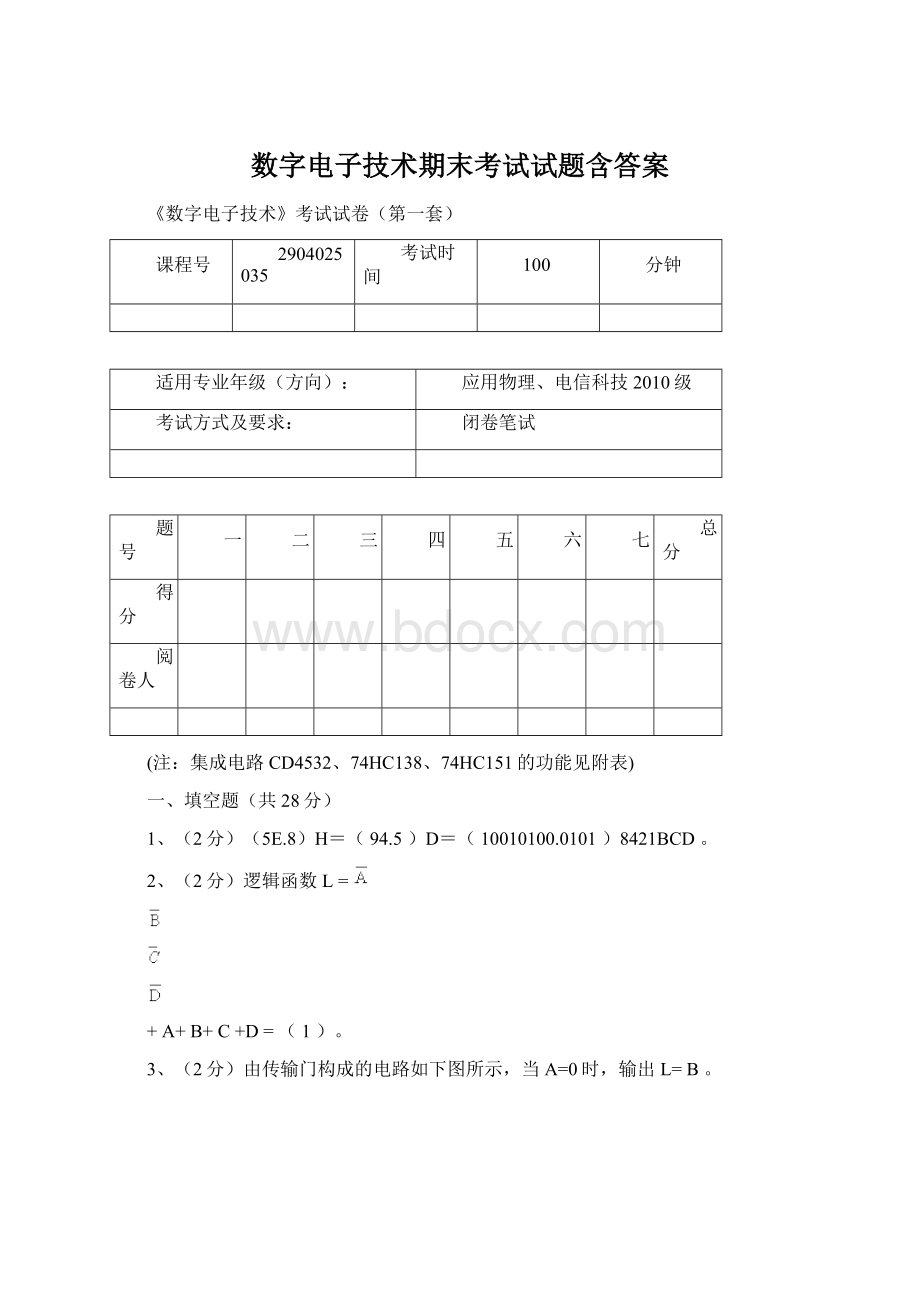

数字电子技术期末考试试题含答案Word文件下载.docx

《数字电子技术期末考试试题含答案Word文件下载.docx》由会员分享,可在线阅读,更多相关《数字电子技术期末考试试题含答案Word文件下载.docx(13页珍藏版)》请在冰豆网上搜索。

一、填空题(共28分)

1、(2分)(5E.8)H=(94.5)D=(10010100.0101)8421BCD。

2、(2分)逻辑函数L=

+A+B+C+D=

(1)。

3、(2分)由传输门构成的电路如下图所示,当A=0时,输出L=B。

4、(2分)三态门可能输出的三种状态是低电平、高电平和高阻态_。

5、(3分)A/D转换器一般要经过_采样__、保持、量化和__编码__这4个步骤,A/D转换器的转换速度主要取决于转换类型。

对双积分型A/D转换器、并行比较型A/D转换器和逐次比较型A/D转换器的相对速度进行比较,转换速度最快的是

_并行比较型A/D转换器__。

6、(2分)集成优先编码器CD4532(功能表见后)正常接电源和地,且待编码信号输入端I0=I2=I6=I7=1,输入使能端EI=1,其余输入端为0,其输出Y2Y1Y0为111。

7、(3分)集成数据选择器74HC151构成的电路如下图所示,则其输出

Y=

。

不需化简)

8、(3分)某PLA电路如下图所示,其输出逻辑函数表达式X=

9、(2分)某单极性输出的8位D/A转换器正常工作,当输入数字量为(10101010)B时,其输出电压为3.4V,当输入数字量为(10101100)B时,其输出电压为3.44V。

10、(2分)一个存储容量为4K×

4的存储器有214个存储单元,若用该存储器构成32K×

8的存储系统,则需16片4K×

4的存储器。

11、(3分)对于JK触发器,当

时,

=1,当

=

,当

二、用公式法将下列逻辑函数化简为最简与或式(12分)

F=AB(C+D)+B(

+

)+

2分

=ABC+ABD+B

+B

=ABC+ABD+B

=B(AC+

+AD+

)2分

=B(A+

=AB+B

+B

三、用卡诺图法将下列逻辑函数化简为最简与或式(10分)

L(A,B,C,D)=∑m(0,1,3,5,7,9)+∑d(10~15)

解:

CD

AB

00

01

11

10

1

X

6分

4分

四、(16分)在举重比赛中有A、B、C三名裁判,A为主裁判,B、C为副裁判。

当两名或两名以上裁判(且必须包括A在内)认为运动员上举杠铃合格时,按动电钮可发出裁决合格信号(即输出Z为1)。

请设计该三输入的组合逻辑电路。

要求:

(1)列出真值表;

(2)写出逻辑函数的最简与或式;

(3)用与非门实现该电路,画出电路图;

(4)用3线8线译码器74HC138实现该电路,画出电路图。

74HC138的符号

解:

(1)真值表见表1,设输入为A、B、C,输出为F

(2)逻辑函数的最简与或式;

(3)用与非门实现

用与非门实现该电路的逻辑图如图(a)所示。

(4)用74HC138实现

A、B、C从A2、A1、A0输入,令

用74HC138实现该电路的逻辑图如图(b)所示。

表1真值表

ABC

F

000

001

010

011

100

101

110

111

图(a)图(b)

五、(20分)分析下图所示时序电路,写出其驱动方程、状态方程和输出方程,画出其状态转换表、状态转换图,检查电路能否自启动,并说明电路实现的逻辑功能。

解:

驱动方程:

状态方程:

输出方程:

状态表:

/Z

X=0

X=1

00

00/0

01/0

01

10/0

10

11/0

11

00/1

状态图:

自启动能力:

具有自启动能力。

逻辑功能:

X=0时,电路处于维持状态;

X=1时,电路为四进制加法计数器。

六、(10分)使用4位同步二进制加计数器74LVC161构成模值为10的计数器,要求画出接线图和状态转换图。

注:

D3、Q3为高位,D0、Q0为低位。

N=10,N<

16,所以只需一片74LVC161。

方法一:

反馈清零法,计数状态为0000-1009;

方法二:

反馈置数法,计数状态为0000-1009;

方法一方法二

状态转换图:

方法一

方法二

七、(10分)请绘制由555定时器构成的施密特触发器的电路图。

若输入Ui的波形如下图所示,又知VCC=15V,5脚不外加控制电压。

求正向閾值电压VT+,负向閾值电压VT-,并画出该电路输出Uo的波形。

555定时器的符号

555定时器构成的施密特触发器的电路及输出Uo的波形如下图。

附表

附表1:

集成优先编码器CD4532功能表

输入

输出

EII7I6I5I4I3I2I1I0

Y2Y1Y0GSEO

L╳╳╳╳╳╳╳╳

HLLLLLLLL

HH╳╳╳╳╳╳╳

HLH╳╳╳╳╳╳

HLLH╳╳╳╳╳

HLLLH╳╳╳╳

HLLLLH╳╳╳

HLLLLLH╳╳

HLLLLLLH╳

HLLLLLLLH

LLLLL

LLLLH

HHHHL

HHLHL

HLHHL

HLLHL

LHHHL

LHLHL

LLHHL

LLLHL

附表1:

集成8选1数据选择器74HC151的功能表

使能

选择

S2S1S0

Y

H

╳╳╳

LH

L

LLL

D0

LLH

D1

LHL

D2

LHH

D3

HLL

D4

HLH

D5

HHL

D6

HHH

D7

附表2集成3线8线译码器74HC138的功能表

附表3集成同步四位二进制加计数器74LVC161的功能表

输入

输出

清零

预置

时钟

预置数据输入

Q3

Q2

Q1

Q0

进位

CEP

CET

CP

D3

D2

D1

D0

TC

×

↑

D3*

D2*

D1*

D0*

#

保持

计数

DN*表示CP脉冲上升沿之前瞬间DN的电平,#表示只有当CET为高电平且计数器状态为HHHH时输出为高电平,其余均为低电平。

附表4555定时器的功能表

阈值输入(6脚)

触发输入(2脚)

复位(4脚)

输出(3脚)

放电管T

导通

<

截止

>

不变

5脚悬空(或经电容接地)时

(注:

专业文档是经验性极强的领域,无法思考和涵盖全面,素材和资料部分来自网络,供参考。

可复制、编制,期待你的好评与关注)