PCIE基础知识Word格式.docx

《PCIE基础知识Word格式.docx》由会员分享,可在线阅读,更多相关《PCIE基础知识Word格式.docx(11页珍藏版)》请在冰豆网上搜索。

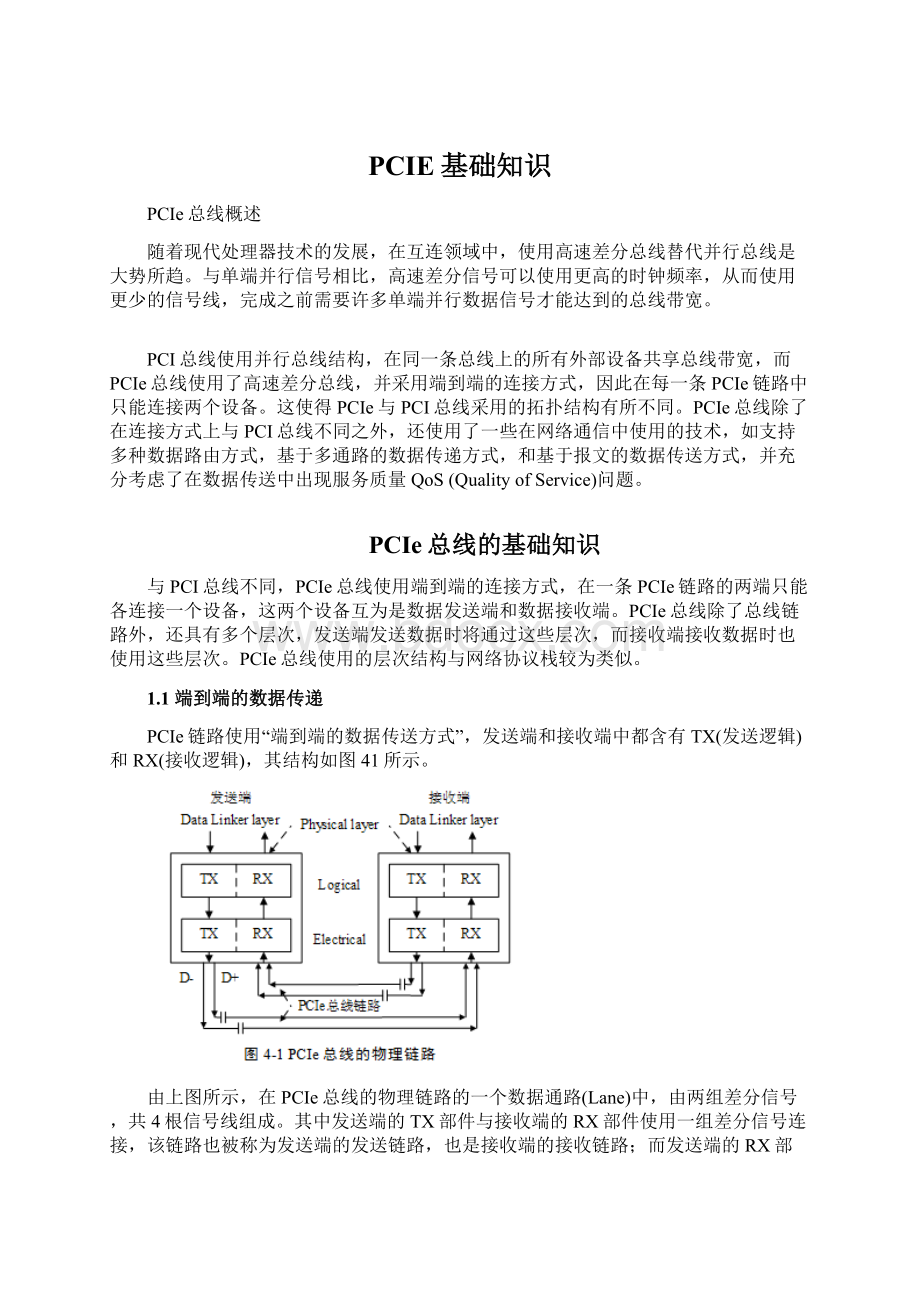

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;

而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC耦合电容。

PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。

因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。

因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(ElectroMagneticInterference)。

由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。

这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。

当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;

二是差分信号的布线相对严格一些。

PCIe链路可以由多条Lane组成,目前PCIe链路可以支持1、2、4、8、12、16和32个Lane,即×

1、×

2、×

4、×

8、×

12、×

16和×

32宽度的PCIe链路。

每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

第1个PCIe总线规范为V1.0,之后依次为V1.0a,V1.1,V2.0和V2.1。

目前PCIe总线的最新规范为V2.1,而V3.0正在开发过程中,预计在20XX年发布。

不同的PCIe总线规范所定义的总线频率和链路编码方式并不相同,如表41所示。

表41PCIe总线规范与总线频率和编码的关系

PCIe总线规范

总线频率[1]

单Lane的峰值带宽

编码方式

1.x

1.25GHz

2.5GT/s

8/10b编码

2.x

2.5GHz

5GT/s

3.0

4GHz

8GT/s

128/130b编码

如上表所示,不同的PCIe总线规范使用的总线频率并不相同,其使用的数据编码方式也不相同。

PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10bit中含有8bit的有效数据;

而V3.0规范使用128/130b编码方式,即在PCIe链路上的130bit中含有128bit的有效数据。

由上表所示,V3.0规范使用的总线频率虽然只有4GHz,但是其有效带宽是V2.x的两倍。

下文将以V2.x规范为例,说明不同宽度PCIe链路所能提供的峰值带宽,如表42所示。

表42PCIe总线的峰值带宽

PCIe总线的数据位宽

×

1

2

4

8

12

16

32

峰值带宽(GT/s)

5

10

20

40

60

80

160

由上表所示,×

32的PCIe链路可以提供160GT/s的链路带宽,远高于PCI/PCI-X总线所能提供的峰值带宽。

而即将推出的PCIeV3.0规范使用4GHz的总线频率,将进一步提高PCIe链路的峰值带宽。

在PCIe总线中,使用GT(Gigatransfer)计算PCIe链路的峰值带宽。

GT是在PCIe链路上传递的峰值带宽,其计算公式为总线频率×

数据位宽×

2。

在PCIe总线中,影响有效带宽的因素有很多,因而其有效带宽较难计算。

尽管如此,PCIe总线提供的有效带宽还是远高于PCI总线。

PCIe总线也有其弱点,其中最突出的问题是传送延时。

PCIe链路使用串行方式进行数据传送,然而在芯片内部,数据总线仍然是并行的,因此PCIe链路接口需要进行串并转换,这种串并转换将产生较大的延时。

除此之外PCIe总线的数据报文需要经过事务层、数据链路层和物理层,这些数据报文在穿越这些层次时,也将带来延时。

在基于PCIe总线的设备中,×

1的PCIe链路最为常见,而×

12的PCIe链路极少出现,×

4和×

8的PCIe设备也不多见。

Intel通常在ICH中集成了多个×

1的PCIe链路用来连接低速外设,而在MCH中集成了一个×

16的PCIe链路用于连接显卡控制器。

而PowerPC处理器通常能够支持×

2和×

1的PCIe链路。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含有时钟恢复模块CDR(ClockDataRecovery),CDR将从接收报文中提取接收时钟,从而进行同步数据传递。

值得注意的是,在一个PCIe设备中除了需要从报文中提取时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参考时钟,这个信号对的描述见下文。

1.2PCIe总线使用的信号

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。

其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用Vaux供电。

在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如StickyRegister,此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复时间。

因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

PCIe链路的最大宽度为×

32,但是在实际应用中,×

32的链路宽度极少使用。

在一个处理器系统中,一般提供×

16的PCIe插槽,并使用PETp0~15、PETn0~15和PERp0~15、PER--]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]]n0~15共64根信号线组成32对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号用于接收链路。

除此之外PCIe总线还使用了下列辅助信号。

1PERST#信号

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。

PCIe设备使用该信号复位内部逻辑。

当该信号有效时,PCIe设备将进行复位操作。

PCIe总线定义了多种复位方式,其中ColdReset和WarmReset这两种复位方式的实现与该信号有关,详见第1.5节。

2REFCLK+和REFCLK-信号

在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-In卡与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe插槽。

PCIe设备与PCIe插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号,如图42所示。

其中100Mhz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

PCIe插槽需要使用参考时钟,其频率范围为100MHz±

300ppm。

处理器系统需要为每一个PCIe插槽、MCH、ICH和Switch提供参考时钟。

而且要求在一个处理器系统中,时钟驱动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。

通常信号的传播速度接近光速,约为6英寸/ns,由此可见,不同PCIe插槽间REFCLK+和REFCLK-信号的传送延时差约为2.5ns。

当PCIe设备作为Add-In卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个参考时钟在100MHz±

300ppm范围内即可。

内置的PCIe设备与Add-In卡在处理REFCLK+和REFCLK-信号时使用的方法类似,但是PCIe设备可以使用独立的参考时钟,而不使用REFCLK+和REFCLK-信号。

在PCIe设备配置空间的LinkControlRegister中,含有一个“CommonClockConfiguration”位。

当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;

如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。

在PCIe设备中,“CommonClockConfiguration”位的缺省值为0,此时PCIe设备使用的参考时钟与对端设备没有任何联系,PCIe链路两端设备使用的参考时钟可以异步设置。

这个异步时钟设置方法对于使用PCIe链路进行远程连接时尤为重要。

在一个处理器系统中,如果使用PCIe链路进行机箱到机箱间的互连,因为参考时钟可以异步设置,机箱到机箱之间进行数据传送时仅需要差分信号线即可,而不需要参考时钟,从而极大降低了连接难度。

3WAKE#信号

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源Vcc。

在PCIe总线中,WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。

值得注意的是产生该信号的硬件逻辑必须使用辅助电源Vaux供电。

WAKE#是一个OpenDrain信号,一个处理器的所有PCIe设备可以将WAKE#信号进行线与后,统一发送给处理器系统的电源控制器。

当某个PCIe设备需要被唤醒时,该设备首先置WAKE#信号有效,然后在经过一段延时之后,处理器系统开始为该设备提供主电源Vcc,并使用PERST#信号对该设备进行复位操作。

此时WAKE#信号需要始终保持为低,当主电源Vcc上电完成之后,PERST#信号也将置为无效并结束复位,WAKE#信号也将随之置为无效,结束整个唤醒过程。

PCIe设备除了可以使用WAKE#信号实现唤醒功能外,还可以使用Beacon信号