Verilog期末实验报告波形发生器Word文档下载推荐.docx

《Verilog期末实验报告波形发生器Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《Verilog期末实验报告波形发生器Word文档下载推荐.docx(12页珍藏版)》请在冰豆网上搜索。

000

171

001

200

010

011

100

29

101

110

111

01

10

33

67

11

50

150

133

表1ROM存储器

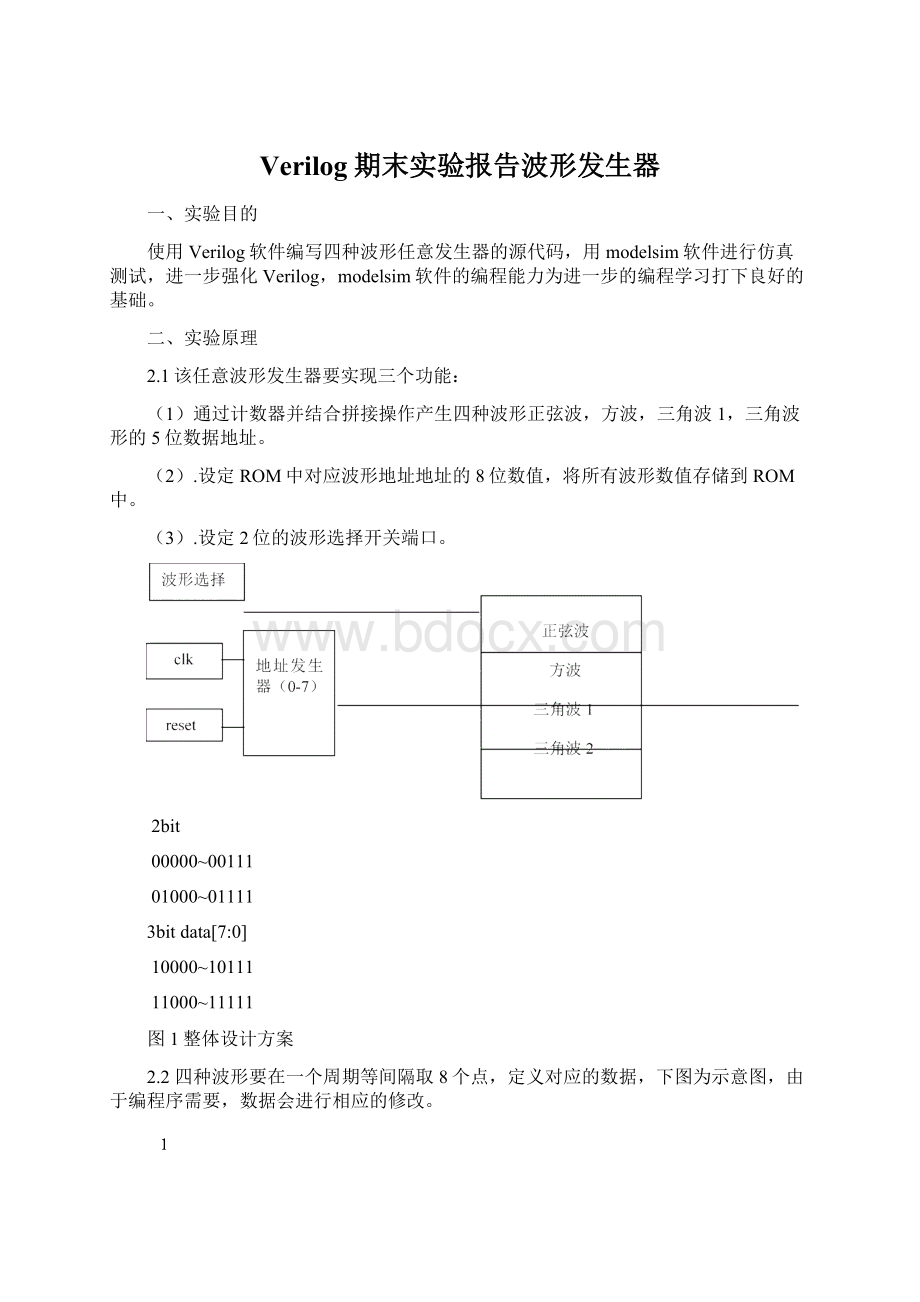

三、实验容

3.1任意波形发生器verilog程序代码:

modulewave(data,clk,add1,reset);

//顶层模块端口定义

output[7:

0]data;

inputclk,reset;

input[1:

0]addr1;

Wire[1:

wireclk,reset;

//输入输出变量定义

ADDR4(addr,clk,addr1,reset);

//地址发生器模块调用

rom1(addr,data);

//ROM存储器模块调用

endmodule

moduleADDR(addr,clk,addr1,reset);

output[4:

0]addr;

reg[2:

0]addr2;

wire[1:

reg[4:

initialaddr2=3'

b000;

//定义计数初值

always(posedgeclkorposedgereset)//每当有clk,或reset信号开启程序

begin

if(reset)

addr2<

=0;

//同步复位

addr<

end

elseif(addr2>

=7)//addr2计数至7时,addr2复位

else

=addr2+1;

//addr2由0至7计数

={addr1,addr2};

//addr1与addr2地址拼接为addr的最终地址

modulerom(addr,data);

//数据存储器模块

input[4:

0]data;

function[6:

0]romout;

//定义函数,存储32个波形取样点地址的数据

wire[7:

case(addr)//根据不同地址,得到不同数据。

0:

romout=171;

1:

romout=200;

2:

3:

romout=100;

4:

romout=29;

5:

romout=0;

6:

7:

8:

9:

10:

11:

12:

13:

14:

15:

16:

17:

18:

romout=33;

19:

romout=67;

20:

21:

22:

23:

24:

25:

romout=50;

26:

27:

romout=150;

28:

29:

romout=133;

30:

31:

default:

romout=8'

hxx;

endcase

endfunction

assigndata=romout(addr);

3.2verilog在quartus软件仿真截图

将代码输入后,建立波形文件,定义输入输出端口后进行仿真。

3.2.1正弦波示意图:

将两位波形选择端设置为00,得出正弦波示意图2

图2

3.2.2.方波示意图:

将两位波形选择端设置为01,得出方波示意图3

图3

3.2.3三角波1示意图:

将两位波形选择端设置为10,得出三角波1示意图4

图4

3.2.4.三角波2示意图:

将两位波形选择端设置为11,得出三角波2示意图5

图5

3.2.5结论:

由上面的四个波形截图可知,在一个周期,通过不同的波形选择端控制,该程序实现了基本的任意波形产生的功能,产生了正确的波形数据,说明代码编写正确。

3.3modelsim任意波形发生器测试程序仿真

3.3.1任意波形发生器测试程序代码。

`timescale1ns/1ns

`include"

wave.v"

modulewave_tp;

//测试模块的名字

regreset,clk;

reg[1:

//测试输入信号addr1定义为reg型

//测试输出信号data定义为wire型

parameterdely=100;

wavefourwave(data,clk,reset,addr1);

//调用测试对象

always#(dely/2)clk=~clk;

initial

reset=1;

clk=0;

addr1=0;

#(dely*200)reset=0;

//延迟200dely后先进行复位

#(dely*200)addr1=2'

b00;

//延迟200dely后测试出正弦波

b01;

//延迟200dely后测试出方波

b10;

//延迟200dely后测试出三角波1

b11;

//延迟200dely后测试出三角波2

#(dely*200)$finish;

//

endmodule

3.3.2modelsim测试程序仿真截图

将测试程序代码与源程序代码一起输入后进行编译,显示波形如下:

3.3.2.1

正弦波测试图6:

将波形输出格式设为模拟形式,可以看出正弦波的测试图

图6

3.3.2.2

方波测试图7:

将波形输出格式设为离散输出形式,可以看出方波的测试图7

图7

3.2.2.3

三角波1测试图8:

将波形输出格式设为模拟形式,可以看出三角波1的测试图8

图8

3.2.2.4

三角波2测试图9:

将波形输出格式设为模拟形式,可以看出三角波2的测试图9

图9

3.3.3.总结

由上面的四个测试波形截图可知,在一个周期,通过不同的波形选择端控制,该程序实现了基本的任意波形产生的功能,产生了正确的实验波形,说明代码编写正确。

四、实验总结

4.1遇到的问题和对应的解决措施:

(1)编程过程中没有注意端口定义过程,没有正确理解wire与reg类型的区别。

导致出错(解决办法:

输出端口应设为可变的wire类型)。

(2)一开始拼接操作用错了地方,用在了ROM部,导致错误。

(解决办法:

应用在加法计数操作后)。

(3)波形数据初值有负数,无确显示数字。

将波形数据平移至x轴以上即可显示正确的波形数据)

(4)一开始我是用拼接操作,有错误,无确显示波形数据(解决办法:

通过case语句输入波形选择addr1端口,成功显示了波形)。

4.2收获:

通过这次期末实验,虽然花了较多时间,遇到了许多的难题,但让我进一步认识了Verilog语言的使用,详细了解了整个程序的设计和仿真过程,独立思考并通过很多的调试,摸索和优化实验程序,最终完成实验,锻炼了我设计verilog程序能力,十分感春平老师的指导和其他同学的帮助。

本课程综合性较强,在实验中涉及了本学期多个知识点:

①always语句;

②initial语句;

③if—else语句;

④case语句;

⑤传递函数assign;

⑥function说明语句,但都属于我们能掌握的基础容,很好地促进了我们进一步学习的激情和自信心。