整理数电实验手册1Word格式文档下载.docx

《整理数电实验手册1Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《整理数电实验手册1Word格式文档下载.docx(32页珍藏版)》请在冰豆网上搜索。

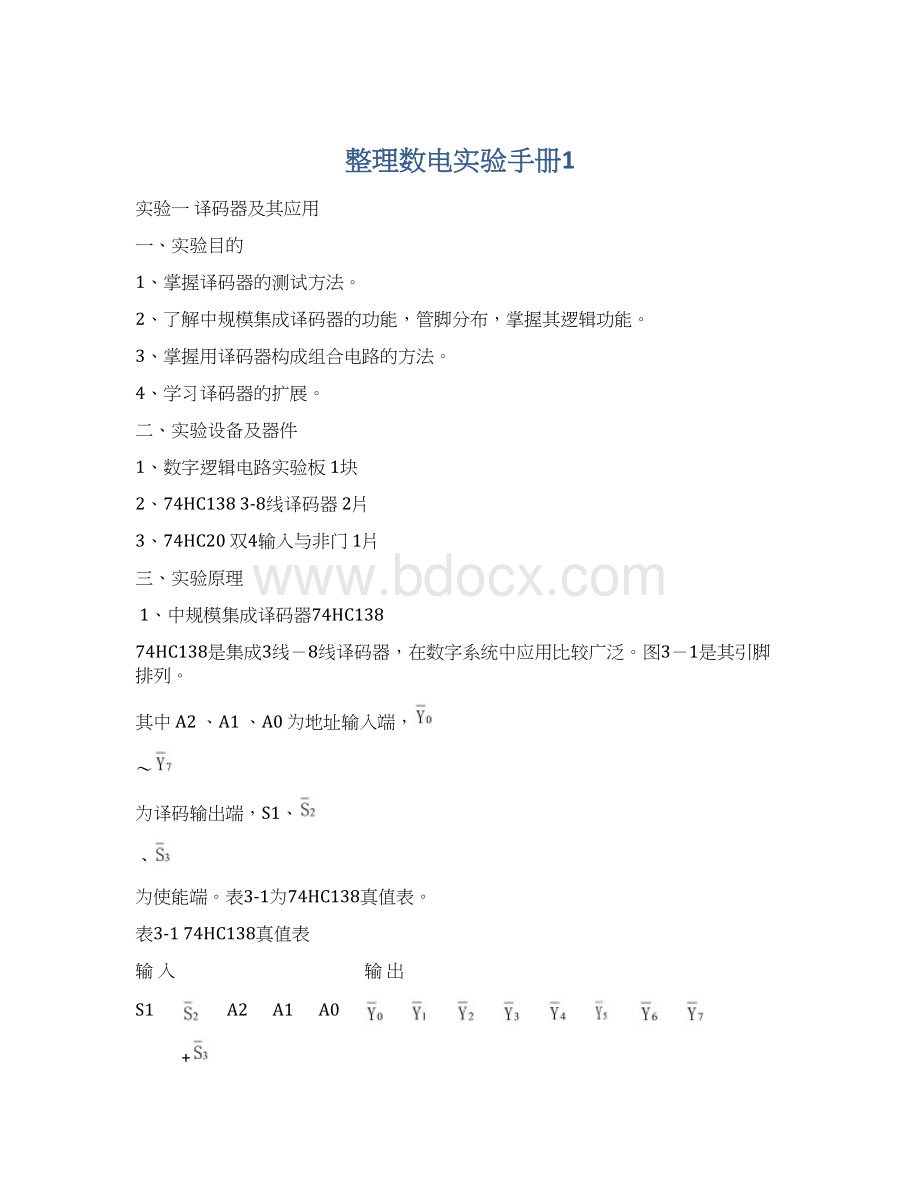

表3-1为74HC138真值表。

表3-174HC138真值表

输入

输出

S1

+

A2

A1

A0

1

×

74HC138

图3-174HC138引脚

74HC138工作原理为:

当S1=1,S2+S3=0时,电路完成译码功能,输出低电平有效。

其中:

2、译码器应用

因为74HC138三-八线译码器的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项,因此可以利用八条输出线组合构成三变量的任意组合电路。

四、实验内容

1、译码器74HC138逻辑功能测试

(1)控制端功能测试

测试电路如图3-2所示。

按表3-2所示条件输入开关状态。

观察并记录译码器输出状态。

LED指示灯亮为0,灯不亮为1。

3-274HC138控制端功能测试

S1

A2A1A0

1╳╳

╳╳╳

110

101

111

╳╳╳

图3-274HC138逻辑功能测试电路

(2)逻辑功能测试

将译码器使能端S1、

及地址端A2、A1、A0分别接至逻辑电平开关输出口,八个输出端

依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按表3-3逐项测试74HC138的逻辑功能。

表3-374HC138逻辑功能测试

2、用74HC138实现逻辑函数

Y=AB+BC+CA

如果设A2=A,A1=B,A0=C,则函数Y的逻辑图如3-3所示。

用74HC138和74HC20各一块在实验箱上连接图3-3线路。

并将测试结果记录表3-4中。

A

B

C

Y

表3-4函数功能测试

图3-3用74HC138组成函数Y

3、用两个3线-8线译码器构成4线-16线译码器。

利用使能端能方便地将两个3/8译码器组合成一个4/16译码器,如图3-4所示。

图3-4用两片74HC138组合成4/16译码器

五、实验注意事项

1、注意集成电路输入控制端和输出控制端的信号。

2、74HC138集成块搭接中注意输出信号的处理。

六、实验报告要求

1、整理有关实验数据,总结利用MSI器件设计组合逻辑电路的方法。

2、写出用两片3线-8线译码器74HC138组成4线-16线译码器的设计过程。

实验二加法器

1、掌握半加器、全加器的工作原理及逻辑功能。

2、掌握集成加法器的应用。

2、74HC2831片

3、74HC041片

4、74HC001片

5、74HC861片

1、半加器

不考虑低位进位,只本位相加,称半加。

实现半加的电路,为半加器。

2、全加器

考虑低位进位的加法称为全加。

实现全加的电路,为全加器。

3、多位加法器

(1)串行多位加法

(2)并行多位加法

四、实验内容与步骤

1、用门电路实现一位全加器。

参照图5-1搭接电路,并测试其功能记录结果在表5-1中。

表5-1全加器真值表

Ci-1AiBi

SiCi+1

000

001

010

011

100

图5-1小规模集成电路设计的全加器

2、用数据选择器实现全加器。

参照图5-2搭接电路,并观察电路的功能。

图5-2用74HC138设计的全加器

3用集成加法器74HC283实现代码转换电路。

要求:

设计一个四位全加器电路,能够完成8421码到余三码的转换。

74HC283的引脚图如图5-4所示,按图5-5搭接电路,并将观察输出记录结果于表5-2。

图5-474HC283的引脚排列图5-58421码转换成余三码电路

表5-2

DCBA

Y3Y2Y1Y0

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

五、实验注意事项

注意74HC153控制端的信号。

1、写出用门电路实现全加器的设计过程,并记录实验结果。

2、写出用数据选择器实现全加器的设计过程,并记录实验结果。

3、写出用译码器实现全加器的设计过程,并记录实验过程。

4、写出用用集成加法器74HC283实现代码转换电路的设计过程,并记录实验结果。

实验三计数器逻辑功能测试及应用

1、熟悉中规模集成电路计数器74HC90的逻辑功能,使用方法及应用。

2、掌握构成任意进制计数器的方法。

1、数字逻辑电路实验板

2、74HC161同步加法二进制计数器1片。

3、74HC00二输入四与非门1片。

三、实验原理

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

1、集成计数器74HC161

集成计数器74HC90是四位二进制计数器,其管脚排列如图7-1,功能表如表7-1。

图7-174HC161管脚排列

2.利用集成计数器芯片可方便地构成任意(N)进制计数器方法:

1)反馈归零法:

是利用计数器清零端的清零作用,截取计数过程中的某一个中间状态控制清零端,使计数器由此状态返回到零重新开始计数。

把模数大的计数器改成模数小的计数器。

其关键是清零信号的选择与芯片的清零方式有关,异步清零方式以N作为清零信号或反馈识别码,其有效循环状态为0~N-1;

同步清零方式以N-1作为反馈识别码,其有效循环状态为0~N-1。

还要注意清零端的有效电平,以确定用与门还是与非门来引导。

2)反馈置数法:

是利用具有置数功能的计数器,截取从Nb到Na之间的N个有效状态构成N进制计数器。

其方法是当计数器的状态循环到Na时,由Na构成的反馈信号提供置数指令,由于事先将并行置数数据输入端置成了Nb的状态,所以置数指令到来时,计数器输出端被置成Nb,再来计数脉冲,计数器在Nb基础上继续计数直至Na,又进行新一轮置数、计数,其关键是反馈识别码的确定与芯片的置数方式有关。

异步置数方式以Na=Nb+N作为反馈识别码,其有效循环状态为Nb~Na;

同步置数方式以Na=Nb+N-1作为反馈识别码,其有效循环状态为Nb~Na。

还要注意置数端的有效电平,以确定用与门还是与非门来引导。

1、测试74HC161的逻辑功能,用数码显示管显示。

并记录结果于表7-2(完)

表7-2

计数脉冲

CP

计数逻辑状态

十进制数

Q3Q2Q1Q0

2

3

4

5

大纲要求

(二)环境影响经济损益分析的步骤6

第五章 环境影响评价与安全预评价

分类具体内容应编写的环境影响评价文件

7

8

2.规划环境影响报告书的审查内容

A.环境影响报告表

9

(1)建设项目概况。

3)迁移。

10

(一)环境影响评价的概念

2)按发布权限分。

环境标准按发布权限可分为国家环境标准、地方环境标准和行业环境标准。

11

2、74HC161芯片构成十六进制计数器

3、用反馈归零法将74HC161构成一个十进制计数器。

参考图7-2接电路,并画出状态转换图。

图7-2

4、利用74HC161构成一个二十四进制的计数器,并用数码显示管显示。

五、实验注意事项

1、集成块功能端有效的状态。

2、实现其他进制计数器的时候注意中断状态和反馈线的处理。

按要求完成上述内容,并总结计数器设计的方法及多级计数器级连有哪些规律?

实验四寄存器功能测试及应用

1、熟悉寄存器的电路结构和工作原理。

2、掌握集成移位寄存器74HC194的逻辑功能和使用方法。

2、