课设二循环彩灯的电路设计讲解文档格式.docx

《课设二循环彩灯的电路设计讲解文档格式.docx》由会员分享,可在线阅读,更多相关《课设二循环彩灯的电路设计讲解文档格式.docx(15页珍藏版)》请在冰豆网上搜索。

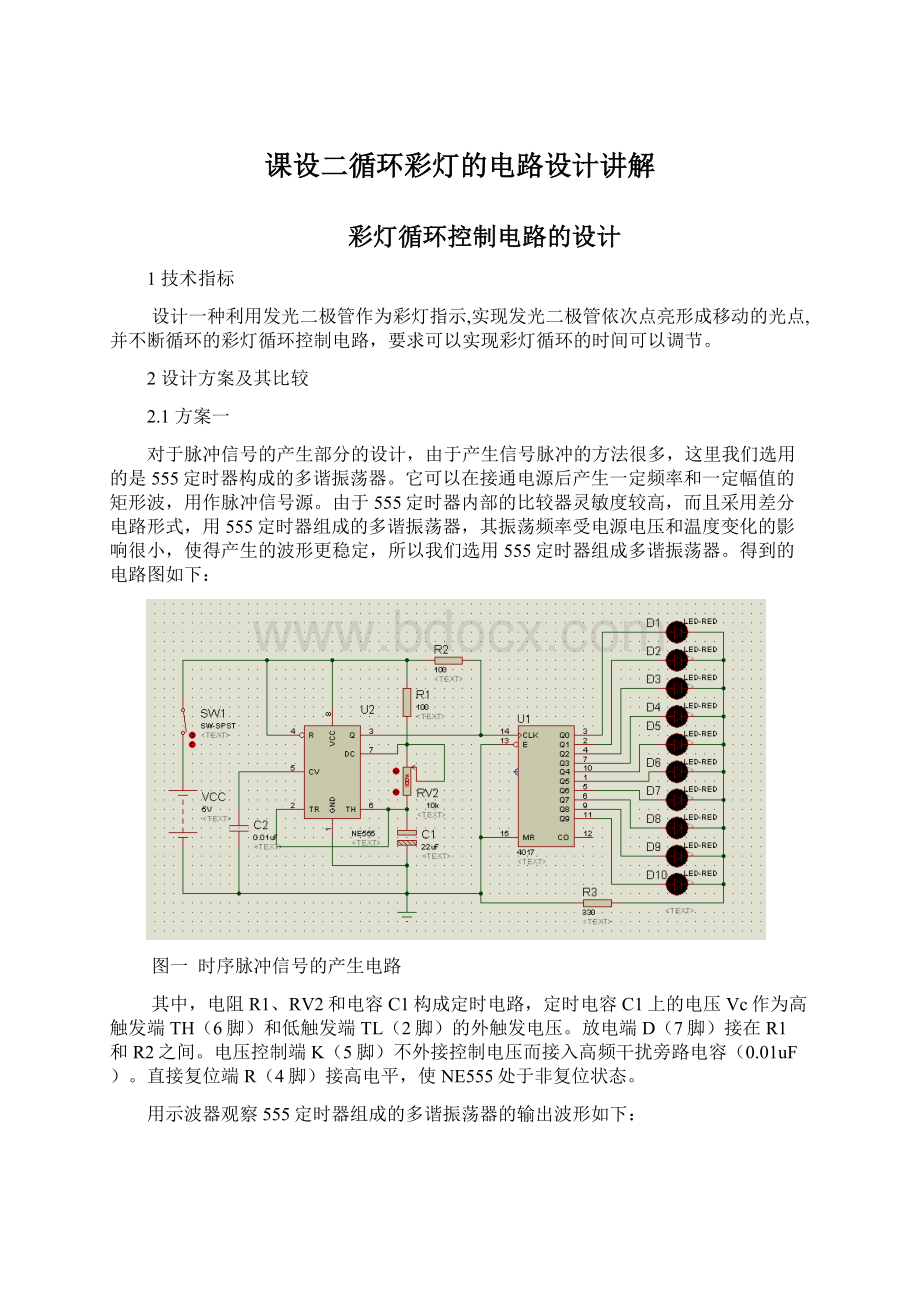

将时序脉冲产生电路中555芯片的3号输出管脚接到CD4017的时钟信号输入端(14脚),得到总的电路图如下:

图四方案一总的电路仿真图

2.2方案二

74LS161是常用的四位二进制可预置的同步加法计数器,可以灵活的运用在各种数字电路中,实现分频器等很多重要的功能,合理应用计数器的清零功能和置数功能,一片74LS161可以组成16进制以下的任意进制分频器。

74LS138为3线-8线译码器,当一个选通端(E1)为高电平,另两个选通端(E2)和(E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。

方案二电路工作原理:

该电路的左边是以555芯片为核心构成的一个多谐振荡电路,借助该电路产生驱动后续芯片的脉冲,该部分电路产生的脉冲周期可以通过改变滑动变阻器RV1的阻值来改变脉冲频率,接下来的电路是以74LS161芯片为核心构成的四位二进制计数器。

计数器在计数脉冲的作用下,Q0到Q3的输出从“0000”到“1111”依次变化。

将74LS161的Q0、Q1、Q2输出端分别连接到74LS138的地址端A、B、C,在Q0、Q1、Q2的输出从“000”到“111”的过程中,通过译码器之后,输出端Y0-Y7依次输出低电平,再经过反相器,驱动对应的二极管发光。

方案二的总体电路图如下:

图五方案二总的电路仿真图

2.3方案三

在第二种方案的基础上,改用74LS193作为计数器,74LS193是同步四位二进制可逆计数器,它具有双时钟输入,并具有异步清零和异步置数等功能,能实现加计数和减计数,相对于74LS161来说,它的功能更齐全。

74LS193的特点是有两个时钟脉冲(计数脉冲)输入端CPU和CPD。

在RD=0、LD=1的条件下,作加计数时,令CPD=1,计数脉冲从CPU输入;

作减计数时,令CPU=1,计数脉冲从CPD输入。

此外,74LS193还具有异步清零和异步预置数的功能。

当清零信号RD=1时,不管时钟脉冲的状态如何,计数器的输出将被直接置零;

当RD=0,LD=0时,不管时钟脉冲的状态如何,将立即把预置数数据输入端A、B、C、D的状态置入计数器的QA、QB、QC、QD端,称为异步预置数。

将74LS193的Q0、Q1、Q2输出端分别连接到3线-8线译码器74LS138的地址输入端A、B、C,同理,在74LS193的输出端Q0、Q1、Q2从“000”到“111”的过程中,通过译码器之后,输出端Y0-Y7依次输出低电平,再经过反相器,驱动对应的发光二极管D0-D7发光。

限流电阻R2的阻值应适宜,太小容易烧坏二极管,太大了二极管不亮或很暗。

方案三的总体电路图如下:

图六方案三总的电路仿真图

2.4方案比较

方案一:

实现该方案只需要两个芯片,并且CD4017是5位Johnson计数器,具有10个译码输出端,因而兼备了计数器和译码器的功能,电路整体来说比方案二、方案三简单,连线也不复杂,而且还能实现十个彩灯的循环,而方案二、方案三最多能实现八个灯的循环,因此方案一更具优势。

从经济角度看,实现该电路很廉价,主要用到了常见的NE555定时器和CD4017,计时精确度高、温度稳定度佳,且价格便宜,此外,由于该方案设计思路明了,功能分区域实现,故在电路板上较容易实现。

方案二:

该方案相对于方案一来说,该方案多用到了一个芯片,用74LS161计数器和74LS138译码器来共同实现CD4017的功能,因此无论是从经济角度看还是从连线的难易度来看,都不如方案一好。

方案三:

该方案相对于方案二来说,是用四位二进制可逆计数器74LS193替换了74LS161,虽说它能实现加减计数,功能更齐全,但由于具有双时钟输入,接线相对来说要复杂,也容易出错,检查电路错误时需要查一下各管脚的功能和连接方式,因而没有方案二实现方便,更没有方案一简单、易实现。

通过比较以上三种方案,可以看出,第一种方案是比较好实现的,按照方案一不仅可以达到课程设计所要达到的要求,而且方案一实现起来非常简单,电路容易理解,实验容易进行,能够减小实验的成本,此外方案一中电路所需要的接线少,简化了电路,降低了接线的难度,只需要查一下各管脚的功能,就能明确接线方案,十分方便。

因此,综合多方面因素,选取方案一来实现最恰当。

3实现方案

3.1原理图

在实现的时候对方案一进行了修正,将两个1.4K的电阻串联后接到7脚,RV2的阻值改为100K,电容C1的值改为10uF,故最终的实现方案电路图如下:

图七最终的实现方案电路仿真图

3.2实验原理

我们用555定时器组成的多谐振荡器实现脉冲信号的产生。

图八555定时器构成多谐振荡电路

接通电源后,电容C1被充电,当定时电容C1上的电压Uc上升到2/3Vcc时,使Uo为低电平,同时555定时器内部的放电三极管T导通,此时电容C1通过和三极管放电,Uc下降,。

当Uc下降到1/3Vcc时,Uo翻转为高电平。

电容C1放电所需时间为:

放电时间

(1)

当放电结束时,三极管T截止,Vcc通过R1、R2及电容C1充电,Uc由1/3Vcc上升到2/3Vcc所需时间为

充电时间

(2)

当Uc上升到2/3Vcc时,电路又翻转为低电平。

如此周而复始,于是,在电路的输出端就得到一个周期性的矩形波。

多谐振荡器无外部信号输入,却能输出矩形波,其实质是将直流形式的电能变为矩形波形式的电能。

矩形波的振荡周期:

(3)

电路的振荡频率:

(4)

输出波形占空比:

(5)

555定时器构成多谐振荡电路的工作波形如下:

图九工作波形

彩灯控制电路的实现主要应用了集成芯片CD4017实现数列循环,控制彩灯的亮灭。

芯片CD4017本身具有计数及译码功能,因此这部分只需按照其功能表来接电路就可以实现要求数列输出,并控制彩灯。

将具有计数及译码功能的芯片CD4017MR、CP1置零,使其工作在正常计数状态,接通电源、脉冲源。

在前九个脉冲中,第n个上升沿脉冲输入时,对应Qn为高电平,其余为低电平,使得Dn二极管发光。

第十个上升沿到达时,Q9对应高电平,即D0至D8灯全部熄灭。

再下一个脉冲上升沿到达,继续上述循环。

3.3元件清单

NE555定时器和CD4017,直流可调稳压电源一台、万用表一块、面包板一块、元器件若干、剪刀、镊子等必备工具

3.4元件介绍

3.4.1555定时器

图十LF353管脚图

管脚解释:

1脚接地端GND2脚触发点

3脚输出4脚复位端

5脚基准电压6脚门限(阈值)

7脚放电端8脚电源电压Vcc

工作参数:

供应电压4.5-18V

供应电流10-15ma

输出电流225mA(max)

上升/下降时间100ns

下表给出了555定时器的功能表:

表1555定时器的功能表

输入

输出

阈值输入

触发输入

复位

放电管

x

导通

<

Vcc

1

截止

>

不变

3.4.2CD4017

芯片CD4017引脚图如下:

Q0-Q9:

计数脉冲输出端

8脚VSS:

地

12脚CO:

进位脉冲输出

13脚INH:

禁止端

14脚CP:

时钟输入端

15脚CR:

清除端

16脚VDD:

正电源

图十一CD4017管脚图

表2给出了CD4017的功能表:

表2CD4017功能表

输入

CP0

CP1

MR

Q0-Q9

CO

清零

每十个时钟输入周期,CO信号完成一次进位,由1变为0

↑

计数

↓

保持

CD4017的工作条件:

电源电压范围:

3V-15V

输入电压范围:

0V-VDD

工作温度范围:

M类:

55℃-125℃

E类:

40℃-85℃

极限值:

电源电压:

-0.5V-18V

输入电压:

-0.5V-VDD十0.5V

输入电流:

±

10mA

贮存温度:

-65℃-150℃

3.4.374ls161

74LS161是常用的四位二进制可预置的同步加法计数器,管脚图如下:

图十二74ls161管脚图

1脚清零/MR2脚时钟CP

3-6脚四个数据输入端P0~P38脚接地端

7脚、10脚使能端CEP、CET9脚置数端PE

11-14脚数据输出端Q0~Q315脚进位输出端TC

16脚正电源

表3给出了74LS161的功能表:

表374LS161功能表

CP

P

T

D3

D2

D1

D0

Q3

Q2

Q1

Q0

X

X

d

c

b

a

保持(C=0)

3.4.474ls138

74LS138为3线-8线译码器,其管脚图如下:

图十三74ls138管脚图

1-3脚:

A0-A2,地址输入端

4、5脚:

、,选通端(低电平有效)

6脚:

STA(E1),选通端

7、9-15脚:

,输出端(低电平有效)

8脚:

GND,接地

16脚:

VCC,正电源

表4给出了74LS138的功能表:

表474LS138功能表

STA

B

C

A2

A1

A0

×

H