VHDL语言快速入门必读Word下载.doc

《VHDL语言快速入门必读Word下载.doc》由会员分享,可在线阅读,更多相关《VHDL语言快速入门必读Word下载.doc(3页珍藏版)》请在冰豆网上搜索。

日本电子工业振兴协会开发的UDL/I语言。

6.VHDL语言中包含的库的种类有哪些?

库:

是经编译后的数据的集合,它存放包集合定义,实体定义,构造体定义,和配置定义。

库的种类:

1.IEEE库,2.STD库,3.面向ASIC的库,4.WORK库,5.用户定义库

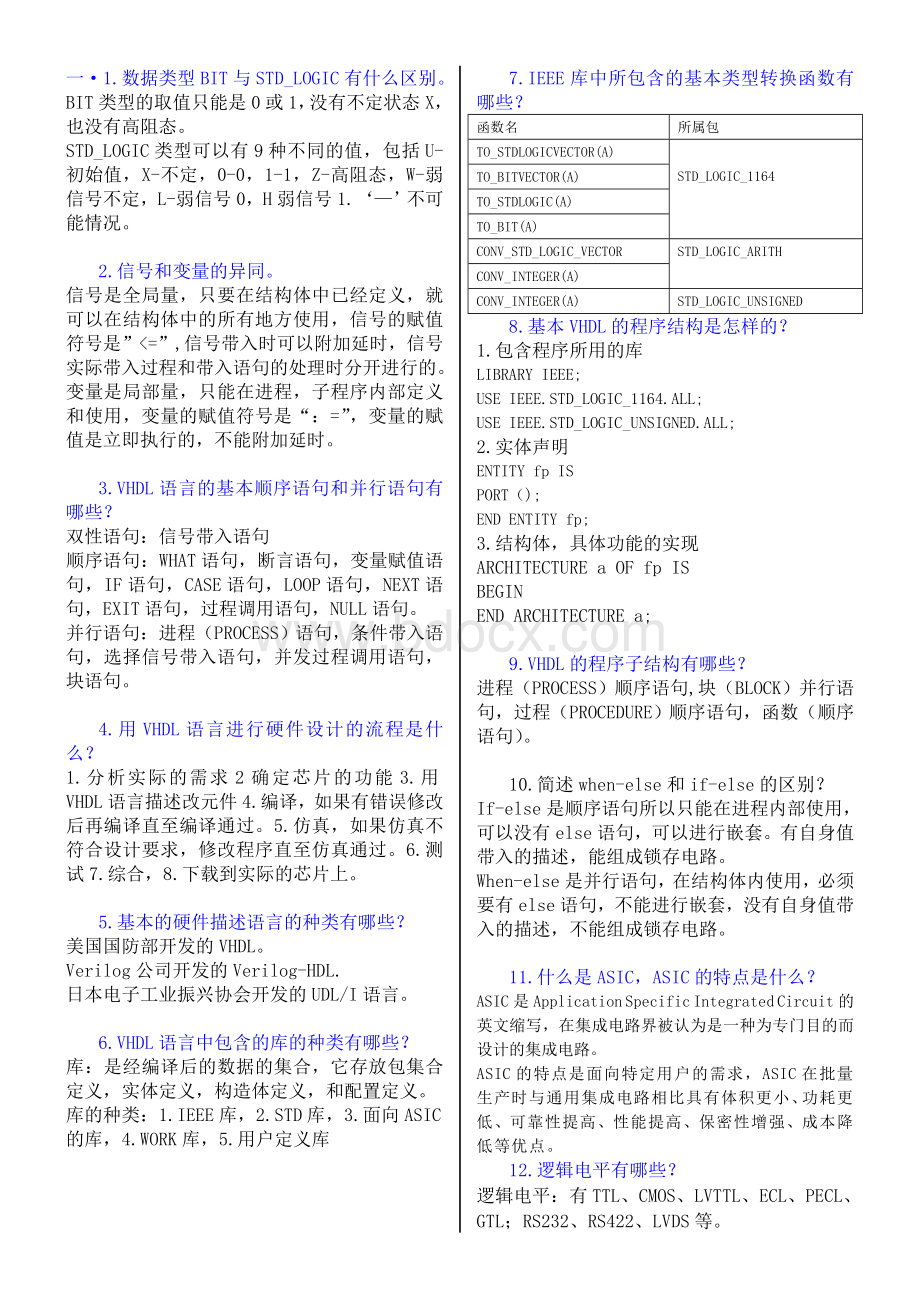

7.IEEE库中所包含的基本类型转换函数有哪些?

函数名

所属包

TO_STDLOGICVECTOR(A)

STD_LOGIC_1164

TO_BITVECTOR(A)

TO_STDLOGIC(A)

TO_BIT(A)

CONV_STD_LOGIC_VECTOR

STD_LOGIC_ARITH

CONV_INTEGER(A)

STD_LOGIC_UNSIGNED

8.基本VHDL的程序结构是怎样的?

1.包含程序所用的库

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

2.实体声明

ENTITYfpIS

PORT();

ENDENTITYfp;

3.结构体,具体功能的实现

ARCHITECTUREaOFfpIS

BEGIN

ENDARCHITECTUREa;

9.VHDL的程序子结构有哪些?

进程(PROCESS)顺序语句,块(BLOCK)并行语句,过程(PROCEDURE)顺序语句,函数(顺序语句)。

10.简述when-else和if-else的区别?

If-else是顺序语句所以只能在进程内部使用,可以没有else语句,可以进行嵌套。

有自身值带入的描述,能组成锁存电路。

When-else是并行语句,在结构体内使用,必须要有else语句,不能进行嵌套,没有自身值带入的描述,不能组成锁存电路。

11.什么是ASIC,ASIC的特点是什么?

ASIC是ApplicationSpecificIntegratedCircuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

12.逻辑电平有哪些?

逻辑电平:

有TTL、CMOS、LVTTL、ECL、PECL、GTL;

RS232、RS422、LVDS等。

·

其中TTL和CMOS的逻辑电平按典型电压可分为四类:

5V系列(5VTTL和5VCMOS)、3.3V系列,2.5V系列和1.8V系列。

5VTTL和5VCMOS逻辑电平是通用的逻辑电平。

13.TTL电平和CMOS电平可以互联吗?

数字电路中TTL电平是个电压范围,规定输出高电平>

2.4V,输出低电平<

0.4V。

在室温下,一般输出高电平是3.5V,输出低电平是0.2V。

CMOS电平在不同的电路中是0v-5v或者0v-12v。

所以可以用CMOS电平驱动TTL电平器件,但是TTL电平驱动CMOS电平器件时须加上拉电阻。

二·

用VHDL语言描述给定电路,或写出给定电路的功能或输出。

三.程序改错。

四.注释程序。

五.程序同功能语句替换。

六.元件例化连接器件。

程序例子:

IF语句:

(1)IF(sel=’0’)THEN

y<

=’1’;

ENDIF;

(2)IF(sel=’0’)THEN

y<

=’0’;

ELSE

(3)IF(sel=”00”)THEN

=”01”;

ELSIF(sel=”01”)THEN

=”10”

……

=”11;

CASE语句:

CASEselIS

WHEN“00”=>

y<

=”00”;

WHEN“01”=>

=”10”;

WHEN“11”=>

=”11”;

ENDCASE;

FOR语句:

FORiIN0TO7LOOP

tmp:

=tmpXORa(i);

ENDLOOP;

WHILE语句:

WHILE(i<

8)LOOP

tmp:

i:

=i+1;

WHEN-ELSE语句(类似if-else):

q<

=i0WHENsel=”00”ELSE

i1WHENsel=”01”ELSE

i2WHENsel=”10”ELSE

i3WHENsel=”11”ELSE

‘X’;

WITH-SELECT语句:

(类似CASE语句)

WITHselSELECT

=i0WHEN“00”,

i1WHEN“01”,

i2WHEN“10”,

i3WHEN“11”,

‘X’WHENOTHERS;

分频器

PORT(clk:

INSTD_LOGIC;

fp1024,fp512,fp64,fp4,fp1:

OUTSTD_LOGIC);

SIGNALbuf:

STD_LOGIC_VECTOR(9DOWNTO0);

fp1<

=buf(9);

fp4<

=buf(7);

fp64<

=buf(3);

fp512<

=buf(0);

fp1024<

=clk;

PROCESS(clk)IS

IF(clk'

EVENTANDclk='

1'

)THEN

IF(buf="

1111111111"

)THENLIBRARYIEEE;

报时电路

ENTITYbsIS

PORT(min,sin:

INSTD_LOGIC_VECTOR(7DOWNTO0);

clk,bs512,bs1024:

bsout:

ENDENTITYbs;

ARCHITECTUREaOFbsIS

IF(min="

01011001"

CASEsinIS

WHEN"

01010000"

=>

bsout<

=bs512;

01010010"

01010100"

01010110"

01011000"

=bs1024;

WHENOTHERS=>

='

0'

;

ENDCASE;

ENDIF;

ENDIF;

ENDPROCESS;

buf<

="

0000000000"

ELSE

=buf+'

元件例化

ENTITYcount60IS

PORT(clkin,en,res:

bs0,bs1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

cyout:

ENDENTITYcount60;

ARCHITECTUREcountOFcount60IS

COMPONENTcount10IS

PORT(clk,enable,reset:

b0:

cy:

ENDCOMPONENT;

SIGNALcount4:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALclk1,cy1:

STD_LOGIC;

bs1<

=count4;

cyout<

=cy1;

u0:

count10 PORTMAP(clk=>

clkin,cy=>

clk1,reset=>

res,enable=>

en,b0=>

bs0);

PROCESS(clk1,res,en)IS

IF(res='

count4<

0000"

ELSIF(clk1'

EVENTANDclk1='

IF(en)='

THEN

IF(count4="

0110"

count4<

cy1<

ELSE

=count4+'

ENDIF;

ENDIF;

ENDARCHITECTURE