计算机组成原理模拟题二_精品文档Word格式文档下载.doc

《计算机组成原理模拟题二_精品文档Word格式文档下载.doc》由会员分享,可在线阅读,更多相关《计算机组成原理模拟题二_精品文档Word格式文档下载.doc(8页珍藏版)》请在冰豆网上搜索。

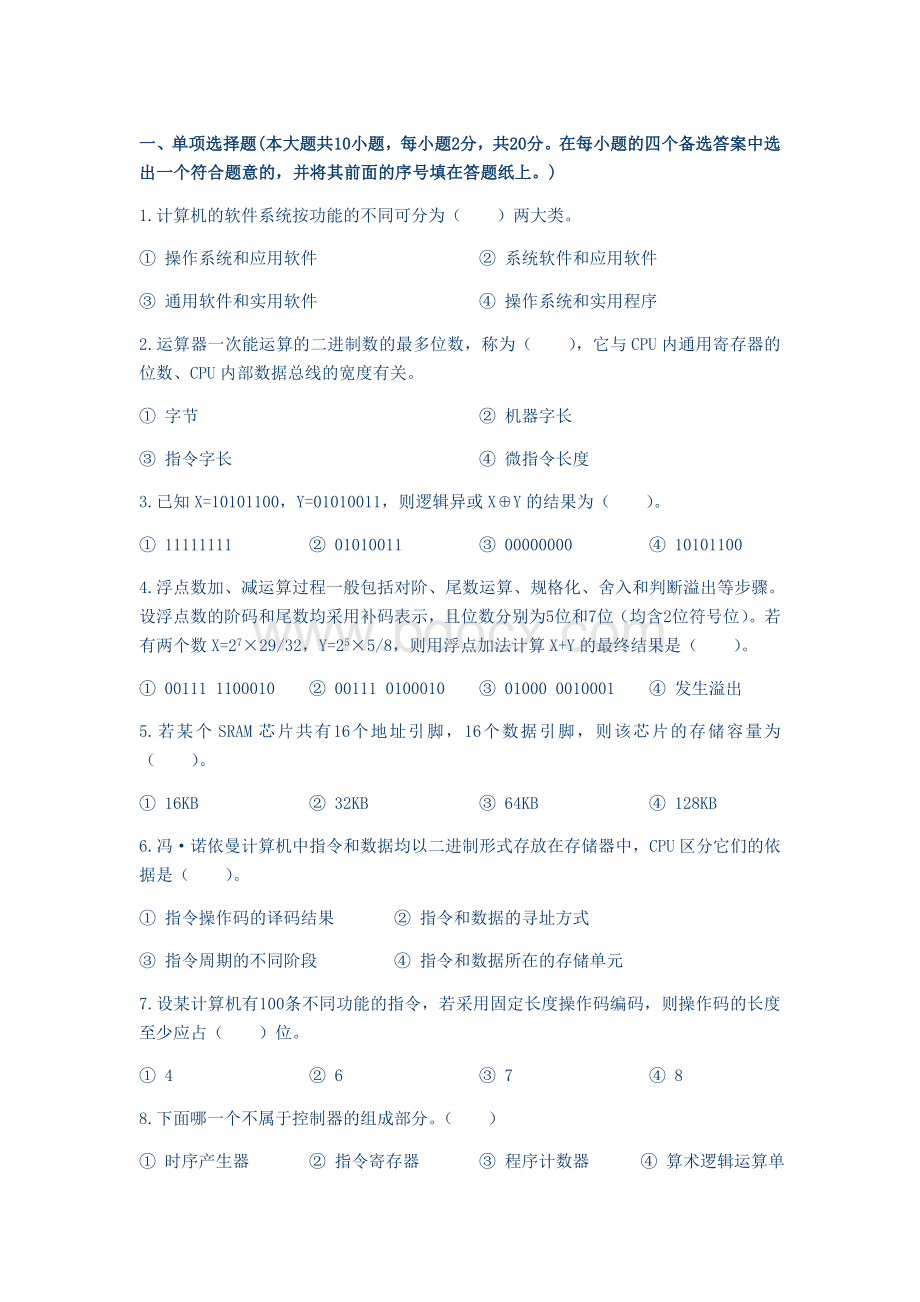

若有两个数X=27×

29/32,Y=25×

5/8,则用浮点加法计算X+Y的最终结果是()。

①001111100010②001110100010③010000010001④发生溢出

5.若某个SRAM芯片共有16个地址引脚,16个数据引脚,则该芯片的存储容量为()。

①16KB②32KB③64KB④128KB

6.冯·

诺依曼计算机中指令和数据均以二进制形式存放在存储器中,CPU区分它们的依据是()。

①指令操作码的译码结果②指令和数据的寻址方式

③指令周期的不同阶段④指令和数据所在的存储单元

7.设某计算机有100条不同功能的指令,若采用固定长度操作码编码,则操作码的长度至少应占()位。

①4②6③7④8

8.下面哪一个不属于控制器的组成部分。

()

①时序产生器②指令寄存器③程序计数器④算术逻辑运算单元

9.保存当前正在执行指令的指令代码的寄存器为()。

①程序计数器PC②指令寄存器IR③地址寄存器AR④数据缓冲器DR

10.双总线结构计算机中采用的双总线是指()。

①系统总线和存储总线②内部总线和外部总线

③机内总线和机外总线④串行总线和并行总线

二、填空题(本大题共10小题。

每小题2分,共20分。

把答案填在答题纸上。

1.用一台40MHz处理机执行标准测试程序,若程序在处理机上运行所获得的有效CPI为1.55CPI,则相应的MIPS速率为MIPS。

2.若11011010,则,。

3.存储器按存储介质的不同可分为半导体存储器、和两种。

4.设主存储器容量为256字,字长为32位,模块数m=4,用交叉方式进行组织。

主存储器的存储周期T=200ns,数据总线宽度为32位,总线传送周期τ=50ns。

若按地址顺序连续读取4个字,则交叉存储器的带宽为Mb/s。

5.某指令系统共分三类,即二地址指令、一地址指令和零地址指令,各类指令为定长(16

位),地址字段均占6位,除二地址指令的操作码为4位外,其余二类指令的操作码采用

扩展方式构成,现已设计出一地址指令300条,则二地址指令最多能设计出条。

6.若操作数在寄存器中,为寻址方式;

若操作数在指令中,为寻址方式。

7.CPU的四个基本功能包括指令控制、、和数据加工。

8.已知某处理机的微指令格式中操作控制字段由5个分离的控制字段组成,这5个字段分别占用3、2、4、3、2位,如果微命令的编码采用编码表示法,则该微指令最多能表示个微命令。

9.在三种集中式总线仲裁方式中,方式对电路的故障最敏感,方式的响应速度最快。

10.在输入/输出系统的四种典型数据传送控制方式中,程序查询方式和主要由CPU执行程序来完成I/O操作,而DMA方式和主要由专用硬件来完成I/O操作。

三、计算题(本大题共2小题,每小题8分,共16分)

1.已知x=0.10011,y=-0.11010,写出[x]补和[y]补,用变形补码计算x+y,同时指出结果是否发生溢出。

2.已知x=-1010011001,y=10101,用原码阵列除法器计算x÷

y。

(要求写出完整的计算过程)

四、简单应用题(本大题共3小题,每小题10分,共30分)

1.某32位计算机系统采用半导体存储器,其地址码是32位,若使用4M×

8位的DRAM芯片组成64MB主存,并采用内存条的形式,问:

(1)若每个内存条为4M×

32位,共需要多少内存条?

(2)每个内存条内共有多少片DRAM芯片?

(3)主存需要多少DRAM芯片?

2.设有一台计算机,其指令长度为16位,有一类RS型指令的格式如下:

其中,OP为操作码,占6位;

R为寄存器编号,占2位,可访问4个不同的通用寄存器;

MOD为寻址方式,占2位,与形式地址A一起决定源操作数,规定如下:

MOD=00,为立即寻址,A为立即数;

MOD=01,为相对寻址,A为位移量;

MOD=10,为变址寻址,A为位移量。

如下图所示,假定要执行的指令为加法指令,存放在1000H单元中,形式地址A的编码为02H,其中H表示十六进制数。

该指令执行前存储器和寄存器的存储情况如下图所示,假定此加法指令的两个源操作数中一个来自于形式地址A或者主存,另一个来自于目的寄存器R0,并且加法的结果一定存放在目的寄存器R0中。

在以下几种情况下,该指令执行后,R0和PC的内容为多少?

(1)若MOD=00,(R0)=;

(2)若MOD=01,(R0)=;

(3)若MOD=10,(R0)=;

(PC)=。

3.在一个计算机系统中假设采用DMA控制器进行输入输出操作,假定DMA的启动操作需要1000个时钟周期,DMA完成时处理中断需要500个时钟周期。

硬盘的传输速率为2MB/s并采用DMA。

如果平均传输的数据长度为4KB,问在硬盘工作时50MHz的处理器将用多少时间比率进行输入输出操作,忽略DMA申请使用总线的影响。

五、综合应用题(本大题共1小题,共14分)

某计算机字长16位,采用16位定长指令字结构,部分数据通路结构如下图所示,图中所有控制信号为1时表示有效、为0时表示无效,例如控制信号MDRinE为1表示允许数据从DB打入MDR,MDRin为1表示允许数据从内总线打入MDR。

假设MAR的输出一直处于使能状态。

加法指令“ADD(R1),R0”的功能为(R0)+((R1))→(R1),即将R0中的数据与R1的内容所指主存单元的数据相加,并将结果送入R1的内容所指主存单元中保存。

下表给出了上述指令取指和译码阶段每个节拍(时钟周期)的功能和有效控制信号,请按表中描述方式用表格列出指令执行阶段每个节拍的功能和有效控制信号。

参考答案

模拟试题一

二、填空题(本大题共10小题,每小题2分,共20分。

1.25.8

2.10110100;

11101101

3.磁表面存储器;

光盘存储器(位置可互换)

4.366

5.11

6.寄存器(或寄存器直接);

立即

7.操作控制;

时间控制(位置可互换)

8.35

9.链式查询;

独立请求

10.程序中断方式;

通道方式

1.

2.

故得商q=011111

余数r=001110

所以[x÷

y]原=111111

[余数]原=101110(0.5分)

即x÷

y=-11111,余数=-01110(0.5分)

1.

(1)(4分)

(2)(4分)

(3)(2分)

2.

(1)(R0)=0102H;

(3分)

(2)(R0)=1300H;

(3)(R0)=3100H;

(2分)

(PC)=1001H。

3.每次DMA传输占用的时间为:

4KB/2MB=0.002秒(4分)

所以如果磁盘不断进行传输,需要的时钟周期数为:

(1000+500)/0.002=750000时钟周期(4分)

占用的CPU时间比率为:

750000/(50×

1000000)=1.5%(2分)

答案一:

答案二:

答案三: