数字逻辑复习题库含答案大学期末复习资料Word文档下载推荐.doc

《数字逻辑复习题库含答案大学期末复习资料Word文档下载推荐.doc》由会员分享,可在线阅读,更多相关《数字逻辑复习题库含答案大学期末复习资料Word文档下载推荐.doc(18页珍藏版)》请在冰豆网上搜索。

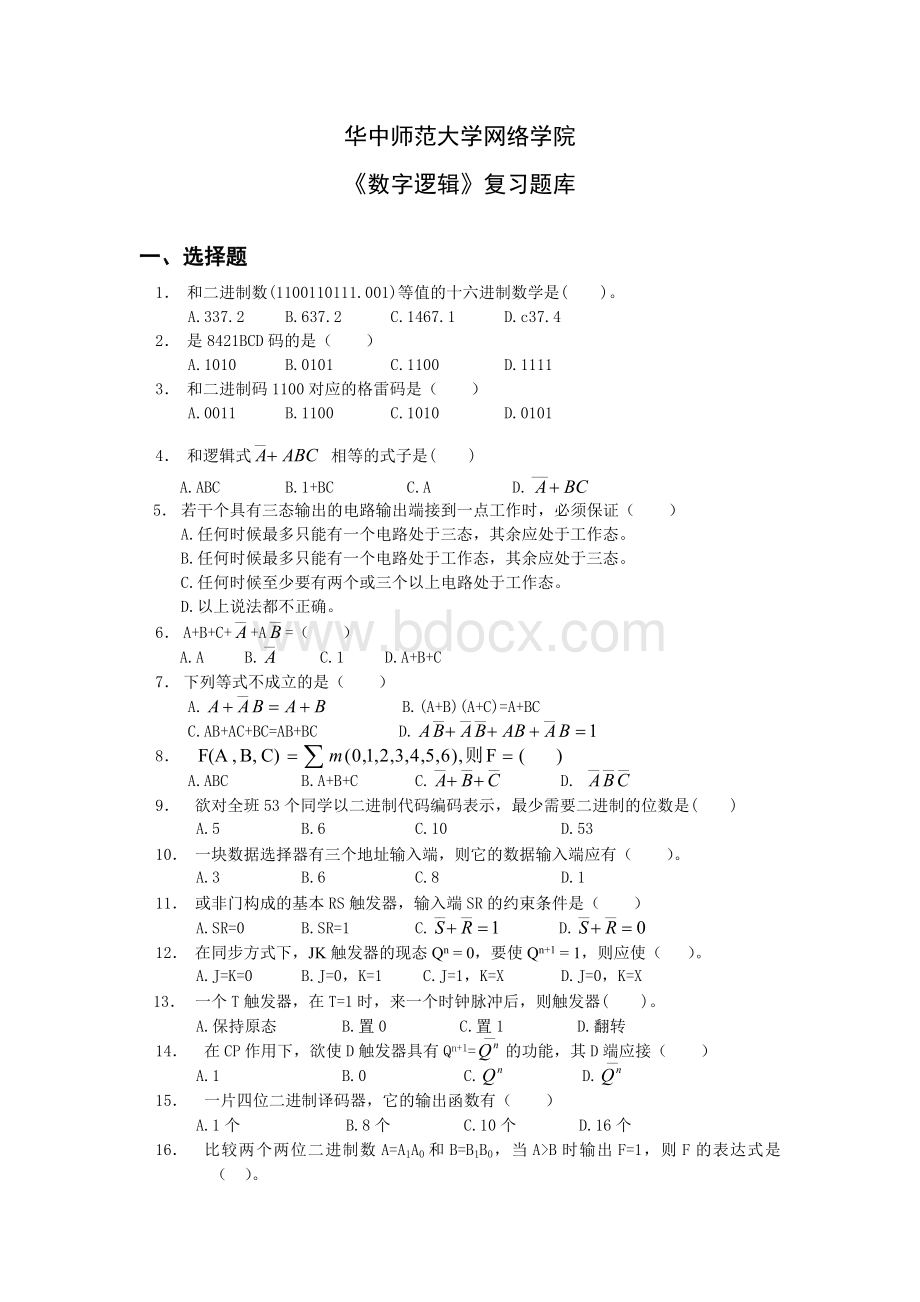

D.以上说法都不正确。

6.A+B+C++A=()

A.AB.C.1D.A+B+C

7.下列等式不成立的是()

A.B.(A+B)(A+C)=A+BC

C.AB+AC+BC=AB+BCD.

8.

A.ABCB.A+B+CC.D.

9.欲对全班53个同学以二进制代码编码表示,最少需要二进制的位数是()

A.5B.6C.10D.53

10.一块数据选择器有三个地址输入端,则它的数据输入端应有()。

A.3B.6C.8D.1

11.或非门构成的基本RS触发器,输入端SR的约束条件是()

A.SR=0B.SR=1C.D.

12.在同步方式下,JK触发器的现态Qn=0,要使Qn+1=1,则应使()。

A.J=K=0B.J=0,K=1C.J=1,K=XD.J=0,K=X

13.一个T触发器,在T=1时,来一个时钟脉冲后,则触发器()。

A.保持原态B.置0C.置1D.翻转

14.在CP作用下,欲使D触发器具有Qn+1=的功能,其D端应接()

A.1B.0C.D.

15.一片四位二进制译码器,它的输出函数有()

A.1个B.8个C.10个D.16个

16.比较两个两位二进制数A=A1A0和B=B1B0,当A>

B时输出F=1,则F的表达式是()。

A.B.

C.D.

17.相同计数模的异步计数器和同步计数器相比,一般情况下()

A.驱动方程简单B.使用触发器的个数少

C.工作速度快D.以上说法都不对

18.测得某逻辑门输入A、B和输出F的波形如下图,则F(A,B)的表达式是()

A.F=ABB.F=A+BC.D.

19.Moore和Mealy型时序电路的本质区别是()

A.没有输入变量B.当时的输出只和当时电路的状态有关,和当时的输入无关

C.没有输出变量D.当时的输出只和当时的输入有关,和当时的电路状态无关

20.n级触发器构成的环形计数器,其有效循环的状态数为()

A.n个B.2n个C.2n-1个D.2n个

21.ROM电路由地址译码器和存储体构成,若译码器有十个地址输入线,则最多可有()个字。

A.10B.102C.210D.104

22.74LS160十进制计数器它含有的触发器的个数是()

A.1个B.2个C.4个D.6个

23.组合型PLA是由()构成

A.与门阵列和或门阵列B.一个计数器C.一个或阵列D.一个寄存器

24.TTL与非门的多余脚悬空等效于()。

A.1B.0C.VccD.Vee

25.设计一个8421码加1计数器,至少需要()触发器

A.3个B.4个C.6个D.10个

26.以下哪一条不是消除竟争冒险的措施()

A.接入滤波电路B.利用触发器C.加入选通脉冲D.修改逻辑设计

27.主从触发器的触发方式是()

A.CP=1B.CP上升沿C.CP下降沿D.分两次处理

28.下列说法中,()不是逻辑函数的表示方法。

A.真值表和逻辑表达式

B.卡诺图和逻辑图

C.波形图和状态图

29.已知某触发器的特性所示(触发器的输入用A、B……表示)。

请选择与具有相同功能的逻辑表达式是()。

A.

B.

C.

AB

Qn+1

说明

00

Qn

保持

01

置0

10

1

置1

11

翻转

30.用ROM实现四位二进制码到四位循环码的转换,要求存储器的容量为()。

A.8B.16C.32D.64

31.下列信号中,()是数字信号。

A.交流电压B.开关状态C.交通灯状态D.无线电载波

32.余3码10001000对应2421码为()

A.01010101B.10000101C.10111011D.11101011

33.若逻辑函数,则F和G相与的结果为()

A.B.1C.D.0

34.为实现D触发器转换为T触发器,图所示的虚线框内应是()

A.或非门B.与非门C.异或门D.同或门

35.完全确定原始状态表中的五个状态A、B、C、D、E,若有等效对A和B,B和D,C和E,则最简状态表中只含()个状态

A.2B.3C.1D.4

36.下列触发器中,没法约束条件的是()

A.时钟触发器B.基本触发器

C.主从触发器D.边沿D触发器

37.组合逻辑电路输出与输入的关系可用()描述

A.真值表B.状态表C.状态图D.逻辑表达式

38.实现两个4位二进制数相乘的组合电路,其输入输出端个数应为()

A.4入4出B.8入8出C.8入4出D.8入5出

39.组合逻辑电路中的险象是由于()引起的

A.电路未达到最简B.电路有多个输出

C.电路中的时延D.逻辑门类型不同

40.设计一个五位二进制码的奇偶位发生器,需要()个异或门

A.2B.3C.4D.5

41.下列触发器中,()不可作为同步时序逻辑电路的存储元件。

A.基本R-S触发器B.D触发器

C.J-K触发器D.T触发器

42.构造一个模10同步计数器,需要()触发器

A.3个B.4个C.5个D.10个

43.实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的()

A.状态数目更多B.状态数目更少

C.触发器更多D.触发器一定更少

44.同步时序电路设计中,状态编码采用相邻编码法的目的是()

A.减少电路中的触发器B.提高电路速度

C.提高电路可靠性D.减少电路中的逻辑门

45.脉冲异步时序逻辑电路的输入信号可以是()

A.模拟信号B.电平信号

C.脉冲信号D.时钟脉冲信号

46.电平异步时序逻辑电路不允许两个或两个以上输入信号()

A.同时为0B.同时为1

C.同时改变D.同时出现

47.脉冲异步时序逻辑电路中的存储元件可以采用()

A.时钟控制RS触发器B.D触发器

C.基本RS触发器D.JK触发器

48.八路数据选择器应有()个选择控制器

A.2B.3C.6D.8

49.移位寄存器T1194工作在并行数据输入方式时,MAMB取值为()

A.00B.01C.10D.11

50.半导体存储器()的内容在掉电后会丢失

A.MROMB.RAMC.EPROMD.E2PROM

51.EPROM是指()

A.随机读写存储器B.只读存储器

C.可擦可编程只读存储器D.电可擦可编程只读存储器

52.用PLA进行逻辑设计时,应将逻辑函数表达式变换成()

A.异或表达式B.与非表达式

C.最简“与—或”表达式D.标准“或—与”表达式

53.补码1.1000的真值为()

A.+1.1000B.-1.1000C.-0.1000D.-0.0001

54.下列哪个函数与逻辑函数F=A⊙B不等()

A.B.

C.D.

55.PROM、PLA、和PAL三种可编程器件中,()是不能编程的

A.PROM的或门阵列B.PAL的与门阵列

C.PLA的与门阵列和或门阵列D.PROM的与门阵列

56.下列中规模通用集成电路中,()属于组合逻辑电路

A.4位计数器T4193B.4位并行加法器T693

C.4位寄存器T1194D.4位数据选择器T580

57.数字系统