合肥工业大学计算机组成原理实验报告汇编.docx

《合肥工业大学计算机组成原理实验报告汇编.docx》由会员分享,可在线阅读,更多相关《合肥工业大学计算机组成原理实验报告汇编.docx(48页珍藏版)》请在冰豆网上搜索。

合肥工业大学计算机组成原理实验报告汇编

实验一存储器实验

1、实验目的

了解静态随机存取存贮器的工作原理;掌握读写存贮器的方法。

二、实验原理

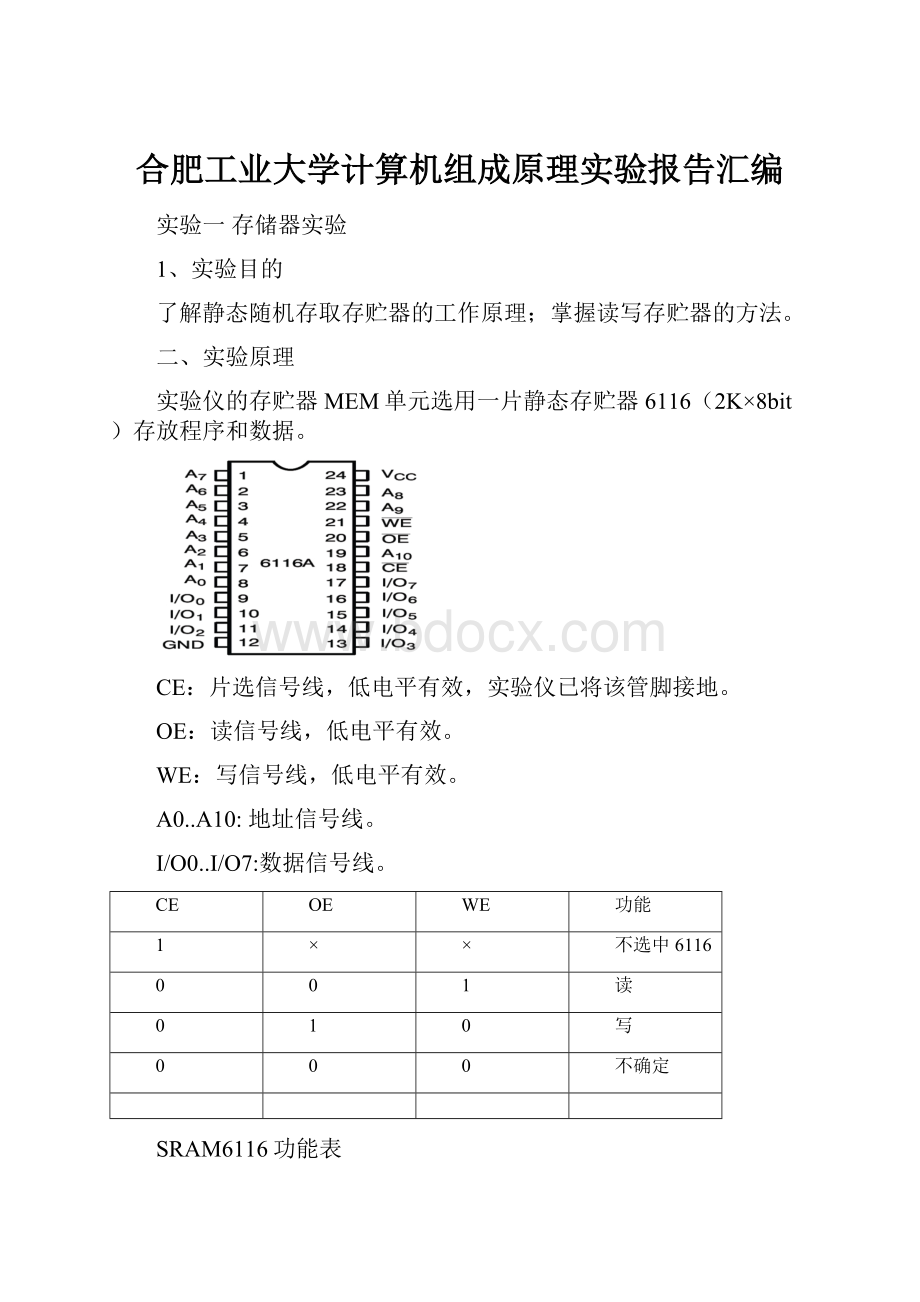

实验仪的存贮器MEM单元选用一片静态存贮器6116(2K×8bit)存放程序和数据。

CE:

片选信号线,低电平有效,实验仪已将该管脚接地。

OE:

读信号线,低电平有效。

WE:

写信号线,低电平有效。

A0..A10:

地址信号线。

I/O0..I/O7:

数据信号线。

CE

OE

WE

功能

1

×

×

不选中6116

0

0

1

读

0

1

0

写

0

0

0

不确定

SRAM6116功能表

存贮器挂在CPU的总线上,CPU通过读写控制逻辑,控制MEM的读写。

实验中的读写控制逻辑如下图:

读写控制逻辑

M_nI/O用来选择对MEM还是I/O读写,M_nI/O=1,选择存贮器MEM;M_nI/O=0,选择I/O设备。

nRD=0为读操作;nWR=0为写操作。

对MEM、I/O的写脉冲宽度与T2一致;读脉冲宽度与T2+T3一致,T2、T3由CON单元提供。

存贮器实验原理图

存贮器数据信号线与数据总线DBus相连;地址信号线与地址总线ABus相连,6116的高三位地址A10..A8接地,所以其实际容量为256字节。

数据总线DBus、地址总线ABus、控制总线CBus与扩展区单元相连,扩展区单元的数码管、发光二极管上显示对应的数据。

IN单元通过一片74HC245(三态门),连接到内部数据总线iDBus上,分时提供地址、数据。

MAR由锁存器(74HC574,锁存写入的地址数据)、三态门(74HC245、控制锁存器中的地址数据是否输出到地址总线上)、8个发光二极管(显示锁存器中的地址数据)组成。

T2、T3由CON单元提供,按一次CON单元的uSTEP键,时序单元发出T1信号;按一次uSTEP键,时序单元发出T2信号;按一次uSTEP键,时序单元发出T3信号;再按一次uSTEP键,时序单元又发出T1信号,……

按一次STEP键,相当于按了三次uSTEP键,依次发出T1、T2、T3信号。

其余信号由开关区单元的拨动开关模拟给出,其中M_nI/O应为高(即对MEM读写操作)电平有效,nRD、nWR、wMAR、nMAROE、IN单元的nCS、nRD都是低电平有效。

三、实验结果及分析

四、思考题

1.本实验系统中所使用的存储芯片6116的容量有多大?

系统中实际可访问的空间是多大?

2K*8位、256*8位

2.本实验系统中存储器的读写控制信号如何得到的?

它们各自在什么时候有效?

通过手拨动开关来获得控制信号,OE:

读信号线,低电平有效。

WE:

写信号线,低电平有效。

实验二系统总线和具有基本输入输出功能的总线接口实验

一、实验目的

理解总线的概念及其特性;掌握控制总线的功能和应用。

二、实验内容

由于存储器和输入、输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。

在该实验平台中,外部总线分为数据总线、地址总线、和控制总线,分别为外设提供上述信号。

外部总线和CPU内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。

地址总线可以为外部设备提供地址信号和片选信号。

由地址总线的高位进行译码,系统的I/O地址译码原理见下图(在地址总线单元)。

由于使用A6、A7进行译码,I/O地址空间被分为四个区,如表所示:

I/O地址译码原理图

A07A06

片选

地址范围

00

IO_nCE0

00-3F

01

IO_nCE1

40-7F

10

IO_nCE2

80-BF

11

IO_nCE3

C0-FF

I/O地址空间分配

CPU通过读写控制逻辑,控制MEM和I/O设备的读写。

实验中的读写控制逻辑如下图:

读写控制逻辑

M_nIO用来选择对MEM还是I/O读写,M_nIO=1,选择存贮器MEM;M_nIO=0,选择I/O设备。

nRD=0为读操作;nWR=0为写操作。

对MEM、I/O的写脉冲宽度与T2一致;读脉冲宽度与T2+T3一致,T2、T3由CON单元提供。

在理解读写控制逻辑的基础上我们设计一个总线传输的实验。

实验所用总线传输实验框图如下图所示,它将几种不同的设备挂至总线上,有存贮器、输入设备、输出设备、寄存器。

这些设备都需要有三态输出控制,按照传输要求恰当有序的控制它们,就可实现总线信息传输。

总线传输实验框图

一、读写控制逻辑实验

1、连线说明:

CBus单元:

M_nIO、nRD、nWR、nINTA(JP42)

——

开关区单元:

K15..K12(JP92)

CBus单元:

nM_RD、nM_WR、nIO_RD、nIO_WR(JP50)

——

扩展区单元:

JP67

注意:

nINTA(K12)置“1”,使中断响应信号不干扰读写存贮器。

2、打开实验仪电源,按CON单元的nRST按键,复位实验仪

3、如果EXEC键上方指示灯点亮,表示实验仪在运行状态;否则,按一次EXEC键,使EXEC键上方指示灯点亮

4、对MEM进行读操作(M_nIO=1、nRD=0、nWR=1),按CON单元的uSTEP键,在T2、T3时刻,扩展区单元JP67对应的DS159指示灯熄灭,DS160-DS162指示灯点亮,表示nM_RD读信号在T2、T3时刻有效

5、对MEM进行写操作(M_nIO=1、nRD=1、nWR=0),按CON单元的uSTEP键,在T2时刻,扩展区单元JP67对应的DS160指示灯熄灭,DS159、DS161、DS162指示灯点亮,表示nM_WR写信号在T2时刻有效

6、对I/O进行读操作(M_nIO=0、nRD=0、nWR=1),按CON单元的uSTEP键,在T2、T3时刻,扩展区单元JP67对应的DS161指示灯熄灭,DS159、DS160、DS162指示灯点亮,表示nIO_RD读信号在T2、T3时刻有效

7、对I/O进行写操作(M_nIO=0、nRD=1、nWR=0),按CON单元的uSTEP键,在T2时刻,扩展区单元JP67对应的DS162指示灯熄灭,DS159-DS161指示灯点亮,表示nIO_WR写信号在T2时刻有效

二、基本输入输出功能的总线接口实验。

1、根据挂在总线上的几个基本部件,设计一个简单的流程:

①输入设备将一个数打入R0寄存器。

②输入设备将另一个数打入地址寄存器。

③将R0寄存器中的数写入到当前地址的存储器中。

④将当前地址的存储器中的数通过OUT单元用LED数码管显示。

2、连线说明:

CBus单元:

M_nIO、nRD、nWR、nINTA(JP42)

——

开关区单元:

K5..K12(JP92)

ALU单元:

rR0、wR0

——

开关区单元:

K9、K8

ALU单元:

IN0..IN7(JP22)

——

iDBus单元:

JP37

MAR单元:

nMAROE、wMAR(JP13)

——

开关区单元:

K11、K10(JP94)

MAR单元:

D0..D7(JP14)

——

iDBus单元:

iD0..iD7(JP38)

存贮器MEM单元:

A0..A7(JP72)

——

ABus单元:

A00..A07(JP56)

存贮器MEM单元:

D0..D7(JP73)

——

DBus单元:

D0..D7(JP53)

存贮器MEM单元:

M_nRD、M_nWR(JP71)

——

CBus单元:

nM_RD、nM_WR(JP44)

IN单元:

IN0..IN7(JP101)

——

DBus单元:

D0..D7(JP52)

IN单元:

nRD

——

CBus单元:

nIO_RD(JP49)

IN单元:

nCS

——

扩展区单元:

GND

OUT单元:

nWR(JP68)

——

CBus单元:

nIO_WR(JP48)

OUT单元:

nCS

——

扩展区单元:

GND

OUT单元:

JP69

——

DBus单元:

D0..D7(JP54)

OUT单元:

JP70

——

扩展区单元:

JP65

注意:

nINTA(K12)置“1”,使中断响应信号不干扰读写存贮器。

3、具体操作步骤图示如下:

在星研软件的工具条中选择“简单模型机实验”,打开简单模型机实验的数据通路图。

(1)拨动开关区单元开关:

M_nIO=1、nRD=1、nWR=1、nINTA=1、rR0=1、wR0=1、wMAR=1;nMAROE=0(允许地址寄存器MAR输出到地址总线)

(2)打开实验仪电源

(3)通过输入设备(IN单元)将数据55H写入R0寄存器

将IN单元置01010101,wR0=0,允许写寄存器R0,M_nIO=0、nRD=0、nWR=1,点击星研软件“单节拍运行”按扭(运行一个机器周期),观察通路图,T2、T3时刻IN单元输出数据,在T3的下降沿IN单元输出的数据写入R0。

wR0=1,结束写R0操作

(4)读R0中数据写入存贮器MEM的15H单元

将IN单元置00010101,wMAR=0,允许写MAR,M_nIO=0、nRD=0、nWR=1,点击星研软件“单节拍运行”按扭(运行一个机器周期),观察通路图,在T3的下降沿IN单元输出的数据写入地址寄存器MAR。

wMAR=1,结束写MAR操作。

rR0=0,允许读寄存器R0;M_nIO=1、nRD=1、nWR=0,允许写存贮器;点击星研软件“单节拍运行”按扭(运行一个机器周期),观察通路图,在T2的时刻完成对存贮器的写入操作。

rR0=1,M_nIO=1、nRD=1、nWR=1,结束写MEM操作。

(5)将当前地址的存贮器中数据读出,写入R0寄存器中。

将IN单元置00010101,wMAR=0,允许写MAR,M_nIO=0、nRD=0、nWR=1,点击星研软件“单节拍运行”按扭(运行一个机器周期),观察通路图,在T3的下降沿IN单元输出的数据写入地址寄存器MAR。

wMAR=1,结束写MAR操作。

wR0=0,允许写寄存器R0;M_nIO=1、nRD=0、nWR=1,允许读存贮器;点击星研软件“单节拍运行”按扭(运行一个机器周期),观察通路图,T2、T3时刻MEM单元输出数据,在T3的下降沿MEM单元输出的数据写入R0。

wR0=1,M_nIO=1、nRD=1、nWR=1,结束写R0操作。

(6)读R0寄存器,数据写入OUT单元,用数码管显示数据。

rR0=0,允许读寄存器R0;M_nIO=0、nRD=1、nWR=0,允许写I/O设备;点击星研软件“单节拍运行”按扭(运行一个机器周期),观察通路图,在T2的下降沿,R0寄存器输出的数据写入OUT单元。

rR0=1、M_nIO=1、nRD=1、nWR=1,结束本次操作。

三、实验结果及分析

本次实验由于是2人完成,由我的学号作为地址,将另一个人的学号输出。

四、思考题

1.本实验系统中外设的读写控制信号如何得到的?

对外设的读、写控制信号能不能同时发出?

对存储器呢?

本实验系统中外设的读写控制信号是拨开关得到的,对外设的读、写控制信号不能同时发出,对存储器的读、写控制信号也不能同时发出。

2.总线上的部件输出数据时为什么要加三态门?

三态门是一种扩展逻辑功能的输出级,也是一种控制开关。

主要是用于总线的连接,因为总线只允许同时只有一个使用者。

通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。

如器件没有选通的话它就处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

实验三具有中断控制功能的总线接口实验

具有DMA控制功能的总线接口实验

一、实验目的

DMA控制信号线的功能和应用;掌握在系统总线上设计DMA控制信号线的方法。

二、实验内容

直接存贮器传送DMA是指将外设的数据不经过CPU直接送入存贮器,或者,从存贮器不经过CPU直接送往外围设备。

一次DMA传送只需要执行一个DMA周期,能够满足一些高速外设数据传输的需要。

现在流行的ARM类CPU,内部集成有多个DMA控制器,允许SD卡、USB、CAN、串口、AD、DA等与存贮器之间通过DMA方式传输数据,可以大大减少占用CPU的时间。

DMA控制器(简称DMAC)传输数据时,需要占用总线,总线的控制权需要在CPU和DMAC之间切换,这就需要控制总线提供相应的信号,实现这种切换,避免总线竞争。

外设需要DMA传输时,向DMAC提出请求,DMAC通过控制总线HOLD信号向CPU提出DMA请求;CPU在当前总线周期结束时,响应DMA请求:

释放总线控制权,发出有效HLDA信号给DMAC;DMAC接受总线控制权,开始DMA传输,传送完毕后,撤销HOLD信号,释放总线控制权;CPU收回总线控制权,同时使HLDA信号失效。

实验原理图

如上图所示,CPU在每个机器周期的T3时刻结束时锁存DMA请求HOLD,如果有DMA请求,生成有效的HLDA信号,

(1)锁住CPU时钟信号,使T1、T2、T3均无效,冻住CPU

(2)释放控制总线、数据总线、地址总线,外部总线都处于高阻状态;DMAC接受总线控制权,等DMA传输完毕,撤消HOLD信号;CPU在每个时钟周期,检查HOLD信号,监测到无效的HOLD的信号后,

(1)CPU输出时钟信号,使CPU可以继续工作

(2)收回控制总线、数据总线、地址总线控制权。

在本实验中,检查U36(74HC245,CPU内外数据总线缓冲器)、U37(74HC245,CPU内外地址总线缓冲器)的OE脚,判断CPU是否失去数据总线、地址总线的控制权;通过检查CBus单元的nIO_RD、nIO_WR、nM_RD、nM_WR信号,检查CPU对控制总线的控制权。

三、实验结果及分析

四、思考题

1.CPU响应中断的条件是什么?

答:

1、有中断源发出的中断请求;

2、中断总允许位EA=1,即CPU开中断;

3、申请中断的中断源的中断允许位为1,即中断没有被屏蔽;

4、无同级或更高级中断正在被服务;

5、当前的指令周期已经结束

2.中断源的中断向量地址是通过数据线还是地址线送给CPU?

答:

数据线

3.CPU响应DMA请求后,其地址线、数据线和控制线引脚出现什么状态?

答:

高阻态

实验四基本运算器实验

一、实验目的

了解运算器的组成结构;掌握运算器的工作原理。

二、实验内容

运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要处理的数据存于暂存器A和暂存器B,三个部件同时接受来自A和B的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM),控制信号S3..S0、CN_I决定哪个部件工作、对操作数进行何种运算,S3..S0通过多路选择开关选择这个部件的结果作为ALU的输出;如果运算影响进位标志FC、零标志FZ、正负标志位FS,在T3状态的下降沿,结果分别锁存到FC、FZ、FS;I是中断允许标志位。

ALU中所有模块集成在一片CPLD中。

逻辑运算部件由逻辑门构成,较为简单,后一节有专门的算术运算部件设计实验,在此对这两个部件不再赘述。

移位运算采用的是8×8位桶形移位器,这样,可以使所有的移位操作都可以一次完成。

下图是一个4×4位桶形移位器

所有的输入通过交叉开关与所有的输出端相连。

如右移2位,第2条对角线(右移2)上的2个交叉开关接通,即第3位(in[3])右移至第1位(out[1]),第2位(in[2])移至第0位(out[0])。

又如右环移1位,第3条对角线(右移1)和第7条对角线(左3,3=4-1)同时有效,即可方便地实现右环移。

逻辑左移/右移只须把没连接的输出位同时充以“0”即可实现;算术右移也只须把没连接的输出位用符号位填充即可。

运算器部件由一片CPLD实现。

ALU的输出通过三态门连到CPU内部数据总线(iDBus)上,另外还有指示灯标明进位标志FC、零标志FZ、正负标志FS。

请注意:

图中T1、T2、T3、nRST已与CON单元相连,其它信号都来自于ALU单元的排针上。

实验仪所有单元的T1、T2、T3、nRST已与控制台(CON)单元的T1、T2、T3、nRst连接,nRst提供复位信号;T1、T2、T3是一个微指令周期的三个节拍,高电平有效,瞬间只有一个信号有效,初始状态T1、T2、T3都是低电平。

wA(允许写暂存器A)、wB(允许写暂存器B)、rALU(允许ALU结果输出到内部数据总线(iDBus)上),都是低电平有效。

暂存器A和暂存器B的数据能在LED灯上实时显示,原理如下图:

进位标志FC、零标志FZ、正负标志FS、内部数据总线iD7…iD0的显示原理与此类似;B、寄存器R0-3、堆栈寄存器SP、标志寄存器PSW(含FC、FZ、FS、I)共用R_0..R_7八个发光二极管,通过Select按键选择,按键上方的发光二极管指示R_0..R_7显示那个寄存器的值。

ALU功能表

运算类型

S3S2S1S0

CN_I

功能

逻辑运算

0000

0

F=A(直通)

0000

1

F=B(直通)

0001

X

F=A+B(或)

(FZ)

0010

X

F=A*B(与)

(FZ)

0011

X

F=A^B(异或)

(FZ)

0100

X

F=/A(取反)

(FZ)

移位运算

0101

0

F=A不带进位循环右移B(取低3位)位

(FZ)

1

F=A算术右移一位

(FZ)

0110

0

F=A逻辑右移一位

(FZ)

1

F=A带进位循环右移一位

(FC,FZ)

0111

0

F=A逻辑左移一位

(FZ)

1

F=A带进位循环左移一位

(FC,FZ)

算术运算

1000

0

F=A+B

(FC,FZ,FS)

1

F=A+B+FC

(FC,FZ,FS)

1001

0

F=A-B

(FC,FZ,FS)

1

F=A-B-FC

(FC,FZ,FS)

1010

0

F=A+1

(FZ)

1

F=NEGA(取补)

(FZ)

1011

X

F=A-1

(FZ)

其它

1100

X

置FC=CN_I

(FC)

1101

X

置I=CN_I

(I)

1110

(保留)

1111

(保留)

S3、S2、S1、S0、CN_I为控制信号,FC-进位标志,FZ-零标志,FS-正负标志,I-中断允许标志;表中功能栏内的FC、FZ、FS表示当前运算会影响到该标志。

*表中‘X’表示任意值,下同

1、连线说明:

ALU单元:

S0..S3(JP18)

——

开关区单元:

K20..K23(JP89)

ALU单元:

wA、wB、rALU、CN_I(JP19)

——

标题:

上海发出通知为大学生就业—鼓励自主创业,灵活就业2004年3月17日开关区单元:

K15..K12(JP92)

就算你买手工艺品来送给朋友也是一份意义非凡的绝佳礼品哦。

而这一份礼物于在工艺品店买的现成的礼品相比,就有价值意义,虽然它的成本比较低但它毕竟它是你花心血花时间去完成的。

就像现在最流行的针织围巾,为何会如此深得人心,更有人称它为温暖牌绝大部分多是因为这个原因哦。

而且还可以锻炼你的动手能力,不仅实用还有很大的装饰功用哦。

ALU单元:

ALU_D0..ALU_D7(JP25)

3、消费“多样化”——

扩展区单元:

JP62

木质、石质、骨质、琉璃、藏银……一颗颗、一粒粒、一片片,都浓缩了自然之美,展现着千种风情、万种诱惑,与中国结艺的朴实形成了鲜明的对比,代表着欧洲贵族风格的饰品成了他们最大的主题。

ALU单元:

IN0..IN7(JP22)

1、现代文化对大学生饰品消费的影响——

开关区单元:

K0..K7(JP97)

2、打开实验仪电源,按CON单元的nRST按键,将ALU的A、B、FC、FZ、FS、I清零;如果EXEC键上方指示灯不亮,请按一次EXEC键,点亮指示灯,表示实验仪在运行状态。

3、给暂存器A赋初值

(1)拨动开关区单元的K7..K0开关,形成二进制数01011000(或其它值);指示灯亮,表示该位是‘1’,灭为‘0’。

2、传统文化对大学生饰品消费的影响

(2)拨动开关区单元K15(wA)、K14(wB)、K13(rALU)、K12(CN_I)开关,赋wA=0(允许写A)、wB=1(禁止写B)、rALU=1(不允许ALU输出)、CN_I=0,按CON单元的STEP按键一次,产生一个T1的下降沿,将二进制数01011000写入暂存器A中,ALU单元的A_7…A_0LED上显示A中的值

4、给暂存器B赋初值

4、“体验化”消费

(1)拨动开关区单元的K7..K0开关,形成二进制数10101011(或其它值)。

(2)赋wA=1(禁止写A)、wB=0(允许写B)、rALU=1(不允许ALU输出)、CN_I=0,按CON单元的STEP按键一次,产生一个T2的下降沿,将二进制数10101011写入暂存器B中,ALU单元的R_7…R_0LED上显示B中的值

(六)DIY手工艺品的“创作交流性”5、赋wA=1(禁止写A)、wB=1(禁止写B)、rALU(K10)=0,按uSTEP键,进入T3节拍,

节拍

十几年的学校教育让我们大学生掌握了足够的科学文化知识,深韵的文化底子为我们创业奠定了一定的基础。

特别是在大学期间,我们学到的不单单是书本知识,假期的打工经验也帮了大忙。

DS169

DS168

营销调研课题T1、T2、T3无效

(T1=0、T2=0、T3=0)

0

0

T1

(T1=1、T2=0、T3=0)

0

1

T2

(T1=0、T2=1、T3=0)

1

0

T3

(T1=0、T2=0、T3=1)

1

1

说明:

1-亮;0-灭

当rALU(K13)=0,如果S3S2S1S0的值是0000时,T2、T3节拍时,允许ALU结果输出;S3S2S1S0的值是其它数值,T3节拍时,允许ALU结果输出,显示于扩展区的二位数码管、DS94..DS101的LED上。

6、根据后边的“运算结果表”,改变K20(S0)、K21(S1)、K22(S2)、K23(S3)、K12(CN_I)的值,观察并记录运算器的输出。

例如:

S0=0,S1=0,S2=0,S3=0,ALU的D7_D0=58H;FC、FZ、FS、I不变。

注意:

只有按CON单元的STEP按键一次,产生一个T3的下降沿,ALU才将标志位FC、FZ、FS、I写入标志寄存器PSW中,才能在ALU单元的FZ、FC、FS、I指示灯上看到结果。

如果实验仪、PC联机操作,则可通过软件中的数据通路图来观测实验结果,方法是:

打开软件,在星研软件的工具条中选择“运算器实验”,打开运算器实验的数据通路图。

进行上面的手动操作,点击工具条上单节拍或单周期命令图标,数据通路图会反映当前运算器所做的操作。

数据通路图

重复上述操作,并完成下表。

然后改变A、B、CN_I的值,验证FC、FZ