EDA交通灯课程设计论文.docx

《EDA交通灯课程设计论文.docx》由会员分享,可在线阅读,更多相关《EDA交通灯课程设计论文.docx(12页珍藏版)》请在冰豆网上搜索。

EDA交通灯课程设计论文

计算机硬件设计实训

报告

题目:

具有四种信号灯的交通灯控制器

班级

学号

姓名

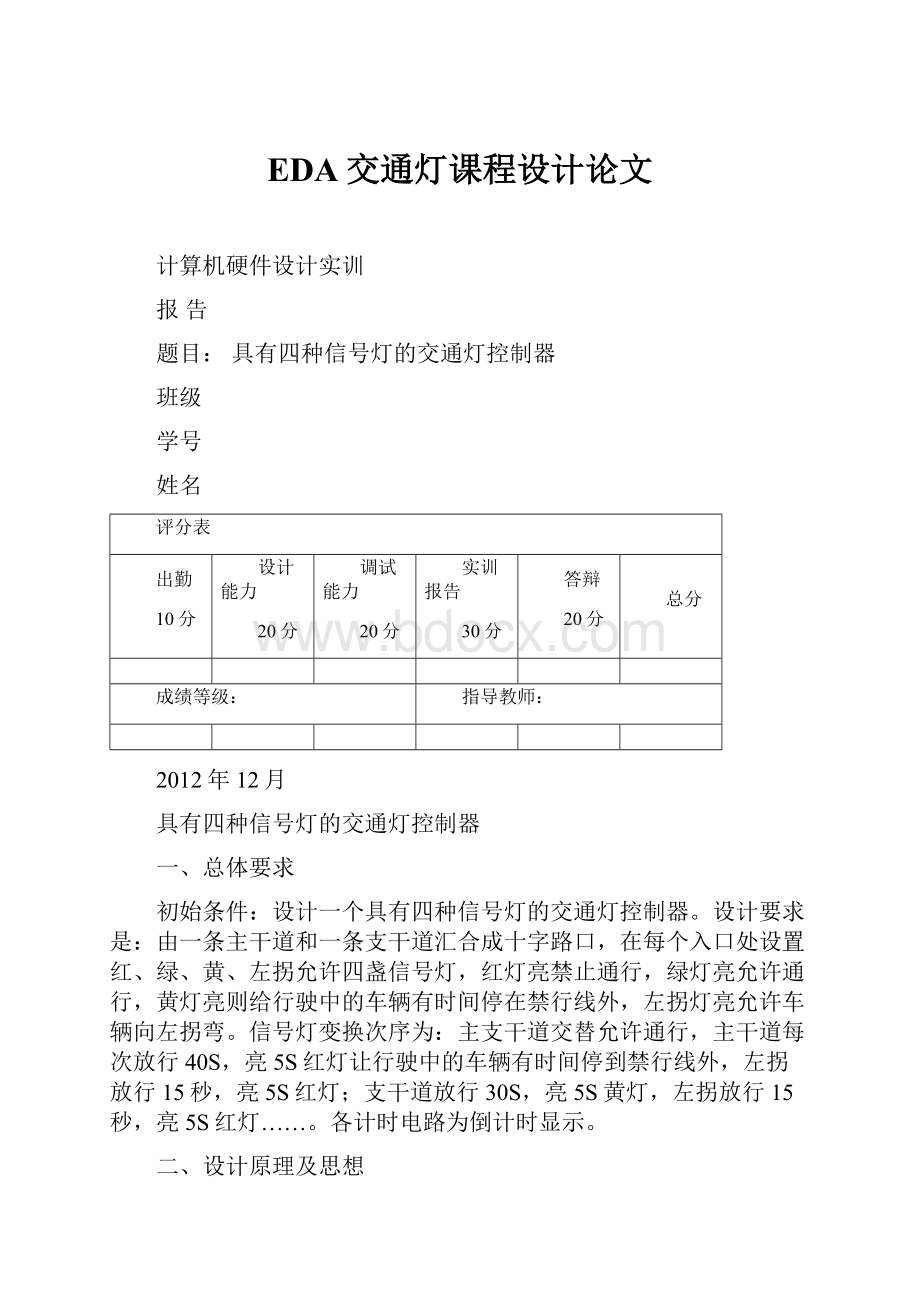

评分表

出勤

10分

设计能力

20分

调试能力

20分

实训报告

30分

答辩

20分

总分

成绩等级:

指导教师:

2012年12月

具有四种信号灯的交通灯控制器

一、总体要求

初始条件:

设计一个具有四种信号灯的交通灯控制器。

设计要求是:

由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄、左拐允许四盏信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外,左拐灯亮允许车辆向左拐弯。

信号灯变换次序为:

主支干道交替允许通行,主干道每次放行40S,亮5S红灯让行驶中的车辆有时间停到禁行线外,左拐放行15秒,亮5S红灯;支干道放行30S,亮5S黄灯,左拐放行15秒,亮5S红灯……。

各计时电路为倒计时显示。

二、设计原理及思想

根据设计要求和系统所具有的功能,并参考相关的文献资料,经行方案设计,可以画出如下图所示的交通信号灯控制器的系统框图。

图1、具有四种信号灯的交通灯控制器系统框图

由交通灯控制器系统框图(图1)可知,该系统由4个子模块组成。

其中包括:

(1)定时模块;

(2)主控电路模块;

(3)译码驱动电路模块;

(4)扫描显示模块。

以上四个电路可以分为两大模块,即:

主控电路及计时(定时)模块和扫描显示译码模块。

三、单元模块设计与仿真

1、主控电路及计时(定时)模块

控制模块根据外部输入信号和计时模块产生的输出信号,产生系统的状态机,控制其他部分协调工作。

计时模块用来设定主干道和支干道计时器的初值,并为扫描显示译码模块提供倒计时时间。

控制及计时模块采用状态机进行设计,可以定义出8种状态,分别为S0:

主干道绿灯,支干道红灯且禁止通行;S1:

主干道黄灯亮,支干道红灯禁止通行;S2:

左拐灯亮,允许左行,支干道红灯,禁止通行;S3:

主干道黄灯,停车;支干道红灯,禁止通行;S4:

主干道红灯,支干道绿灯。

S5:

主干道红灯,支干道黄灯S6:

主干道红灯,支干道左拐灯亮,允许左拐S7:

主干道红灯,支干道黄灯。

其仿真波形如下:

图2、主控电路及计时(定时)模块仿真图

2、扫描显示译码模块

扫描显示译码模块可以根据控制信号,驱动交通信号灯以及倒计时数码管的显示,其中数码管的显示采用动态扫描显示。

本模块采用数码显示管来完成。

数码显示管是计数器等电路的最好选择。

数码管可以用TTL或者CMOS集成电路直接驱动完成。

仿真波形如下:

图3、扫描显示译码模块仿真图

3、顶层文件的编写

将以上各个单元模块仿真成功后,再进行顶层文件的编写。

根据以上设计思路,可以得到如下的顶层文件原理图

图4、具有四种信号灯的交通灯控制器的顶层原理图

系统输入信号:

clk:

1kHz的时钟信号;

en:

系统使能信号

系统输出信号:

lampa1:

主干道红灯信号

lampa2:

主干道黄灯信号

lampa3:

主干道绿灯信号

lampa4:

主干道左拐信号

lampb1:

主干道红灯信号

lampb2:

主干道黄灯信号

lampb3:

主干道绿灯信号

lampb4:

主干道左拐信号

acounth,acountl:

主干道计时输出

bcounth,bcountl:

支干道计时输出

仿真波形如下:

图5、具有四种信号灯的交通灯控制器的顶层文件仿真图

(1)

图6、具有四种信号灯的交通灯控制器的顶层文件仿真图

(2)

四、结果及分析

通过仿真可以看到:

当主干道绿灯,支干道红灯时,主干道倒计时高位置数0100,低位置数0101;支干道高位置数0101,低位置数0000;

当主干道黄灯,支干道红灯时,主干道黄灯倒计时置数0101;支干道继续刚才的减计数;

当主干道红灯,支干道绿灯时,主干道倒计时高位置数0011,低位置数0000;支干道高位置数0010,低位置数0101;

当主干道红灯,支干道黄灯时,支干道黄灯倒计时置数0101;主干道继续刚才的减计数。

在S4状态结束后,自动跳回到S0状态,继续判断支干道是否有车行驶,若有车行驶,则跳转到S1状态,给高、低位置数,继续进行减计时。

系统根据COUNT的变化自动在各状态下跳变,当count为45时,跳变到S2状态;当count为50时,跳变到S3状态;当count为75时,跳变到S4状态;当count为80时,若支干道没有车跳变到S0状态,有车则跳变到S1状态。

五、调试过程中遇到的问题及解决方法

设计过程中参考课本后面的附带的设计程序,发现了书中的一些小瑕疵,在老师的帮助下,加以修改,最终完成了主控电路模块的仿真。

错误:

修改后:

六、收获与体会

本设计采用了VHDL硬件描述语言文本输入方式,在确立总体预期实现功能的前提下,分层次进行设计。

实现了具有四种信号灯的交通灯控制器,以及时间的倒计时显示,指挥行人和车辆安全通行。

程序中所用到的数据均可以根据实际情况进行设置,修改灵活方便。

通过此次设计,我对于VHDL硬件描述语言有了更深入地了解,也在原来所学的理论基础上得到了进一步地应用。

但由于经验上的不足,有些地方还需要做进一步地改善。

七、附件:

程序清单

1.主控电路及计时(定时)模块

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYtrafficIS

PORT

(

clk,en:

INSTD_LOGIC;

lampa1,lampa2,lampa3,lampa4,lampb1,lampb2,lampb3,lampb4:

OUTSTD_LOGIC;

acounth,acount1,bcounth,bcount1:

OUTSTD_LOGIC_VECTOR(3DOWNTO0)

);

ENDtraffic;

ARCHITECTUREoneOFtrafficIS

signaltempa,tempb:

std_logic;

signalcounta,countb:

std_logic_vector(2downto0);

signalnuma,numb,ared,ayellow,agreen,aleft,bred,byellow,bgreen,bleft:

std_logic_vector(7downto0);

BEGIN

com1:

process(en)

begin

if(en='0')then

ared<="01010101";ayellow<="00000101";agreen<="01000000";aleft<="00010101";

bred<="01100101";byellow<="00000101";bgreen<="00110000";bleft<="00010101";

endif;

endprocesscom1;

acounth<=numa(7DOWNTO4);acount1<=numa(3downto0);

bcounth<=numa(7downto4);bcount1<=numb(3downto0);

com2:

process(clk,en,tempa,numa)

begin

if(en='1')then

if(tempa='0')then

tempa<='1';

casecountais

when"000"=>numa<=agreen;lampa1<='0';lampa2<='0';lampa3<='1';lampa4<='0';counta<="001";

when"001"=>numa<=ayellow;lampa1<='0';lampa2<='1';lampa3<='0';lampa4<='0';counta<="010";

when"010"=>numa<=aleft;lampa1<='0';lampa2<='0';lampa3<='0';lampa4<='1';counta<="011";

when"011"=>numa<=ayellow;lampa1<='0';lampa2<='1';lampa3<='0';lampa4<='0';counta<="100";

when"100"=>numa<=ared;lampa1<='1';lampa2<='0';lampa3<='0';lampa4<='0';counta<="000";

whenothers=>lampa1<='1';lampa2<='0';lampa3<='0';lampa4<='0';

endcase;

elsif(numa>1)then

if(numa(3downto0)="0000")then

numa(3downto0)<="1001";numa(7downto4)<=numa(7downto4)-1;

else

numa(3downto0)<=numa(3downto0)-1;

if(numa="00000010")thentempa<='0';endif;

endif;

else

lampa1<='1';lampa2<='0';lampa3<='0';lampa4<='0';counta<="000";tempa<='0';

endif;

endif;

endprocesscom2;

com3:

process(clk,en,tempb,numb)

begin

if(en='1')then

if(tempb='0')then

tempb<='1';

casecountbis

when"000"=>numb<=bgreen;lampb1<='1';lampb2<='0';lampb3<='0';lampb4<='0';countb<="001";

when"001"=>numb<=byellow;lampb1<='0';lampb2<='0';lampb3<='1';lampb4<='0';countb<="010";

when"010"=>numb<=bleft;lampb1<='0';lampb2<='1';lampb3<='0';lampb4<='0';countb<="011";

when"011"=>numb<=byellow;lampb1<='0';lampb2<='0';lampb3<='0';lampb4<='1';countb<="100";

when"100"=>numb<=bred;lampb1<='0';lampb2<='1';lampb3<='0';lampb4<='0';countb<="000";

whenothers=>lampb1<='1';lampb2<='0';lampb3<='0';lampb4<='0';

endcase;

elsif(numb>1)then

if(numb(3downto0)="0000")then

numb(3downto0)<="1001";numb(7downto4)<=numb(7downto4)-1;

else

numb(3downto0)<=numb(3downto0)-1;

if(numb="00000010")thentempb<='0';

endif;

endif;

else

lampb1<='1';lampb2<='0';lampb3<='0';lampb4<='0';countb<="000";tempb<='0';

endif;

endif;

endprocesscom3;

ENDone;

2.扫描显示译码模块

libraryieee;

useieee.std_logic_1164.all;

entityledis

port(DD:

instd_logic_vector(3downto0);

a,b,c,d,e,f,g:

outstd_logic);

endled;

architectureoneofledis

begin

process(DD)

variablett:

std_logic_vector(6downto0);

begin

caseDDis

when"0000"=>tt:

="0000001";

when"0001"=>tt:

="1001111";

when"0010"=>tt:

="0010010";

when"0011"=>tt:

="0000110";

when"0100"=>tt:

="1001100";

when"0101"=>tt:

="0100100";

when"0110"=>tt:

="0100000";

when"0111"=>tt:

="0001111";

when"1000"=>tt:

="0000000";

when"1001"=>tt:

="0001100";

whenothers=>null;

endcase;

a<=tt(6);b<=tt(5);c<=tt(4);d<=tt(3);e<=tt

(2);f<=tt

(1);g<=tt(0);

endprocess;

endone;