数字电子钟.docx

《数字电子钟.docx》由会员分享,可在线阅读,更多相关《数字电子钟.docx(8页珍藏版)》请在冰豆网上搜索。

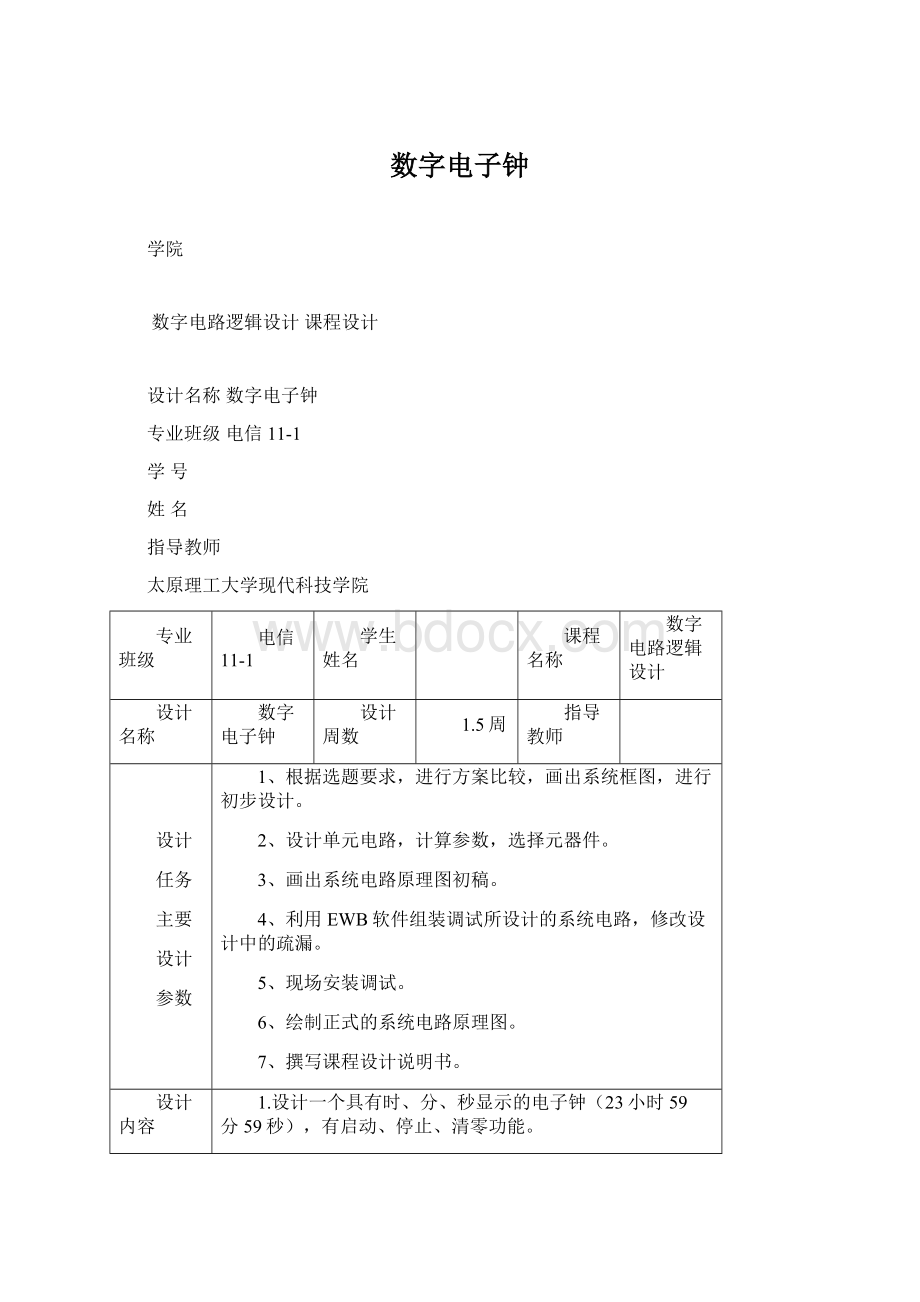

数字电子钟

学院

数字电路逻辑设计课程设计

设计名称数字电子钟

专业班级电信11-1

学号

姓名

指导教师

太原理工大学现代科技学院

专业班级

电信11-1

学生姓名

课程名称

数字电路逻辑设计

设计名称

数字电子钟

设计周数

1.5周

指导教师

设计

任务

主要

设计

参数

1、根据选题要求,进行方案比较,画出系统框图,进行初步设计。

2、设计单元电路,计算参数,选择元器件。

3、画出系统电路原理图初稿。

4、利用EWB软件组装调试所设计的系统电路,修改设计中的疏漏。

5、现场安装调试。

6、绘制正式的系统电路原理图。

7、撰写课程设计说明书。

设计内容

设计要求

1.设计一个具有时、分、秒显示的电子钟(23小时59分59秒),有启动、停止、清零功能。

2.使用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试。

主要参考

资料

王毓银,数字电路逻辑设计(第二版),高等教育出版社

贾秀美,数字电路硬件设计实践,高等教育出版社

白静,数字电路与逻辑设计,西安电子科技大学出版社

学生提交

归档文件

1.设计报告,加封皮,统一A4纸,简订;

2.仿真结果及调试结果;设计总结、报告。

课程设计任务书

注:

1.课程设计完成后,学生提交的归档文件应按照:

封面—任务书—说明书—图纸的顺序进行装订上交(大张图纸不必装订)

2.可根据实际内容需要续表,但应保持原格式不变。

指导教师签名:

日期:

2013年12月29日

……………………………………装………………………………………订…………………………………………线………………………………………

专业班级电信11-1学号姓名成绩

一.设计目的

1.掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

2.进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;

3.提高电路布局﹑布线及检查和排除故障的能力;

4.培养书写综合实验报告的能力。

二.设计要求

1.设计一个具有时、分、秒显示的电子钟(23小时59分59秒),有启动、停止、清零功能。

2.使用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试;

3.得出框图和逻辑电路图及仿真图,写出设计、实验总结报告。

三.设计原理

1.数字电子钟基本原理

数字电子钟的逻辑框图如下图所示。

它由555集成芯片构成的振荡电路、分频器、计数器、显示器和校时电路组成。

555集成芯片构成的振荡电路产生的信号经过分频器作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、“秒”译码器显示时间。

2.数字电子钟单元电路设计

时钟脉冲已经由实验箱提供,实验箱提供的是连续脉冲;

显示电路已经由实验箱提供。

计数器电路

A.秒个位计数器,分个位计数器,时个位计数器均是十进制计数器;

B.秒十位计数器,分十位计数器均是六进制计数器;

C.时十位计数器为二进制计数器

因此,选择74LS160加与非门(74LS00)可以实现二-五-十进制异步计数器芯片实现上述计数功能。

3.器件清单

类型

型号及规格

数量

中规模集成芯片

74LS160

6

中规模集成芯片

74LS00

2

导线

若干

4、设计方案

数字显示及时系统是通过控制电路使加法计数器对连续脉冲进行计数,而加法计数器通过译码器来显示它所记忆的脉冲周期个数。

1、连续脉冲产生

连续脉冲可选用555定时器构成的多谐振荡器产生,用555定时器构成的多谐振荡器,定时元件是电阻和电容,普通器件误差较大,易受温度变化影响,对于对时间要求高的应用场合,其误差较大。

连续脉冲也可选用石英晶体振荡器通过计数器分频产生,可获得精确的秒脉冲信号。

2、计数及译码显示

加法计数器构成电子秒表的计数单元,首先用一个分频器对多谐振荡器产生的脉冲信号进行分频,然后将输出端取得周期为1s的矩形脉冲送入计数器中,计数器都接成8421码十进制形式,其输出端与译码显示单元的相应输入端连接。

3、控制部分

控制部分用来控制计时器的清零、计时、停止。

环形计数器的输出分别作为计数部分的清零信号、计时信号和停止信号。

五、EWB仿真模拟

数字计数器原理图:

三位计时器仿真图

四位计时器仿真图

六位计时器仿真图

六、数字电子钟的组装与调试

由图中所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。

这里的每一级是指组成数字中的各个功能电路。

级联时如果出现时序配合不同步,或剑锋脉冲干扰,引起的逻辑混乱,可以增加多级逻辑门来延时。

数字电子钟由石英晶体振荡器、分频器、计数器、译码器和校时电路组成,石英晶体振荡器产生的信号经过分频作为秒脉冲,秒脉冲送入计数器,计数结果通过时、分、秒译码器显示时间。

由图中所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。

这里的每一级是指组成数字中的各个功能电路。

首先连三位计数器,完成9分59秒,运用六片74LS160和两片74LS00组成,将秒的十位部Qb、Qc通过一个与非门完成模为六的计数器。

然后将三位计数器增到四位计数器,多加一片74LS160和两个与非门,完成59分59秒,重复秒的十位部连接,将分的个位Rco接出两条线进入一个与非门,将这个输出作为分的十位的脉冲输入。

继续加到五位计数器,完成9时59分59秒,重复分的个位连接,将分的十位部的脉冲输入同时加到时的个位。

最后完成六位计时器,完成23时59分59秒,将时的两位作为一个整体完成模值为24的计数器,将时的个位的Qc与时的十位的Qb通过一个与非门将输出分别作为时的个十位脉冲输入,再将时的个位Roc出两条接一个与非门,将输出作为到时的十位脉冲输入。

完成电路的连接与设计。

实验箱效果图

七、实验结论

通过运用数字集成电路设计的24小时制的数字电子时钟,经过试验,成功实现了以下基本功能:

能准确计时,以数字形式显示时、分、秒的时间;

八、设计心得

在此次的数字钟设计过程中,我更进一步地了解并熟悉了芯片的内部结构,同时掌握了各芯片的工作原理及其使用方法。

要求必须熟悉逻辑电路及其芯片各个引脚的功能,否则在电路出现错误时很难准确地找出错误的原因。

在设计电路时要以电路的简单和实现功能的齐全为原则。

而我们一开始没有遵循这两条原则,只是考虑了功能的实现,所以做出的电路特别复杂。

由于电路的复杂进行调试时老是出现各种错误,最后在老师的建议下我们终于连好了电路,而且使电路比以前简易了许多,只用了六个74LS160,两个74LS00。

实验中我们遇到了实践中的各种困难,比如电路的接触不良,导线的短接,芯片的好坏等等一系列问题,在解决这些问题的过程中我们学会了很多书本上没有的知识,从而理解了开设这门儿课的真正意义——理论和实践的结合,同时也懂得了团队合作的意义。

现在想起来,刚开始时为了这次课设而愁眉苦脸是值得的,因为我们通过自己的努力取得了胜利,这让我们无比的兴奋,让我们对课设有了新的认识,并且产生了浓厚的兴趣,对我们以后的学习有很大的帮助。