FCAE1553B协议解析.docx

《FCAE1553B协议解析.docx》由会员分享,可在线阅读,更多相关《FCAE1553B协议解析.docx(15页珍藏版)》请在冰豆网上搜索。

FCAE1553B协议解析

FC-AE-1553B协议硬件结构

✧FC-AE-1553协议整体架构及模块划分

✧SERDES高速收发模块

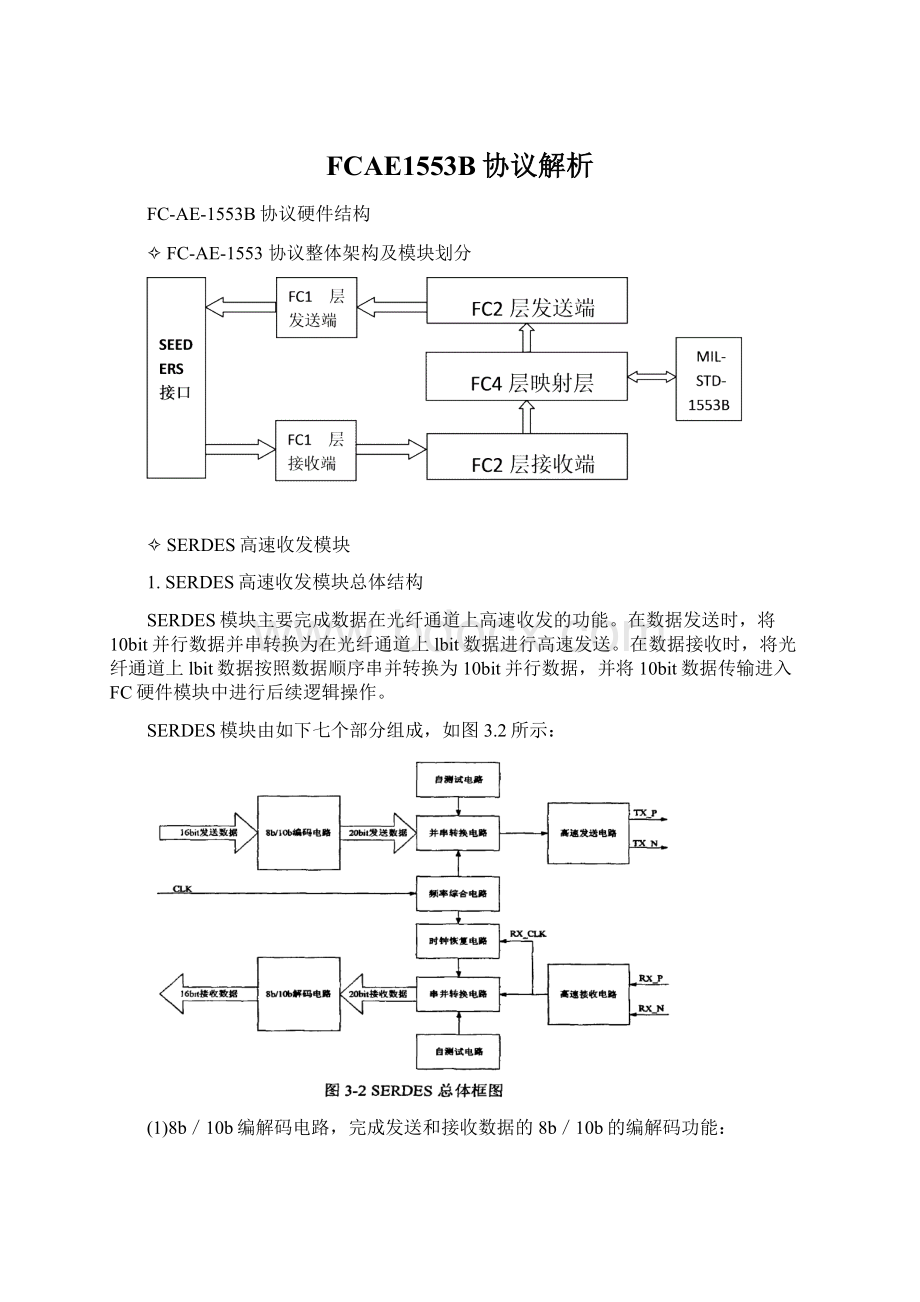

1.SERDES高速收发模块总体结构

SERDES模块主要完成数据在光纤通道上高速收发的功能。

在数据发送时,将10bit并行数据并串转换为在光纤通道上lbit数据进行高速发送。

在数据接收时,将光纤通道上lbit数据按照数据顺序串并转换为10bit并行数据,并将10bit数据传输进入FC硬件模块中进行后续逻辑操作。

SERDES模块由如下七个部分组成,如图3.2所示:

(1)8b/10b编解码电路,完成发送和接收数据的8b/10b的编解码功能:

(2)频率综合电路,即PLL产生电路,产生1.0GHz~2.5GHz的时钟供发送电路使用,以及接收电路时钟恢复使用;

(3)时钟恢复电路,主要功能是从输入数据中恢复时钟信号并为芯片内部提供工作需要的时钟;

(4)高速数据收发电路,采用LVDS接口,完成接收发送差分信号的功能;

(5)串并转换与并串转换电路,完成发送10bit到lbit及接收lbit到10bit的数据串并转换功能;

(6)信号质量侦测电路,完成判断差分信号是否符合要求,并给出检测结果:

(7)自测试模块电路,完成环路功能检测以及抖动等性能测试,完成SERDES模块自测试功能;

频率综合电路、时钟恢复电路、高速收发电路、串并与并串电路等涉及到模拟电路设计,而在XilinxV5FPGA中有成熟的IPRoeketlO可以直接调用,所以在本系统设计中除了8b/10b编解码电路进行详细逻辑设计之外,其余电路结构可以使用口核进行实现。

16位输入数据的接收时序

1.18b/10b编解码主要思想

8b/10b编解码是一种高性能的编码标准,主要目的是使数据在传输的过程之中保持高的信号变换频率。

编码的基本思想是将8比特字节宽度的数据转换为10比特数据,10比特数据宽度的中0和1的个数相差最大不能超过2,这样进行便面可以确保了在高频时钟下信息流的直流频谱分量最大限度的接近零,所以采用8b10b编码进行数据流传输特别适合光纤通信。

此外,这种编码方式可以提供一种简单的“逗号"特性,一种特殊的8比特数据串,解码模块可以利用这种简单的特性实现输出8bit数据的字同步。

8b/10b编码具有直流平衡和较强的检错能力的关键原因是编码过程中引用了Disparity和RD概念,如果1的个数大于0的个数则Disparity为2,RD值为正,如果1和0的个数相同则Disparity为0,RD值不变,如果1的个数小于0的个数则Disparity为.2,RD值为负。

RD值不可能为零,只可能是正负两种情况,所以在解码过程中能检测出Disparity违规的情况,而且有较强的直流平衡能力。

在8b/10b编码过程中,每个8比特数据对应了两组10比特数据,分别对应于Im+和RD一两种情况,可以将10B码字分为正持续差异值RD+和负持续差异值RD一,通过RD值的计算和判断来选择相应的10B码字进行输出。

1.28b/10b编码模块结构设计

8b10b编码模块结构如图3-3所示:

8b/10b编码模块结构框图如上图所示,在FC.FS协议中,起始数据RD恒定为负。

输入的8比特数据,被拆分为高3比特数据和低5比特数据,5比特数据查找模块通过初始RD值或者前一次编码反馈RD值确定的当前5比特数据到6比特数据查表操作,在查表后把5比特查表后得到的RD结果传送到3比特数据查找模块,3比特数据查找模块将通过当前RD值的执行3比特数据到4比特数据查表操作,最后将转换完成的4比特数据和6比特数据传输进入数据合并模块,得到10比特输出数据。

完成8bit数据到10bit数据的转换,并将最终的RD值反馈回输入作为下一次编码的起始RD。

1.38b10b解码模块结构设计

10比特数据输入时,首先进行RD计算,并将数据和计算结果传送到RD违规判断逻辑,RD违规判断逻辑通过上一次数据的RD反馈值和当前输入的RD计算值判断输入数据是否有RD违规,同时检测输入数据是否在8b10b编码表中,如果出现RD违规或者出现数据编码错误则报告错误类型。

如果输入数据没有错误,则将输入数据拆分为高6比特数据和低4比特数据进行3B/4B解码及5B/6B解码,将解码得到的3比特数据和5比特数据传送到数据合并模块,得到最终解码后的8比特数据。

✧FCl层发送模块划分与逻辑实现

FCl层发送模块如图3.19所示:

FCl层发送模块主要由三部分组成,32bit-16bit数据解复用模块(thirtytw02sixteen)16bit-20bit8b10b编码模块,20bit-10bit数据解复用模块。

✧32bit-16bit数据解复用模块设计

主要功能:

将FC2层发送的32比特数据,在两个时钟周期内拆分为两组16比特数据并发送给16bit-20bit8blob编码模块。

模块实现方法:

在此模块使用100M时钟,而FC2层发送模块使用50M时钟,所以两个时钟周期内FC2层发送到此模块的输入数据不会变化,模块在每个时钟周期的上升沿到来时,输出一个16bit数据,输出顺序是先输出32bit数据的高16bit数据,然后在第二个时钟周期上升沿到来时,输出32bit数据的低16bit数据。

✧16bit-20bit8blOb编码模块设计

主要功能:

将输入的16bit数据拆分为两个8bit数据,并行进行8b10b编码工作,输出20bit经过编码后的数据。

模块内部结构如图3.20所示:

实现方法:

当FC-FS硬件逻辑工作在2Gbit/s速率下,进入8b10b模块的数据率是212.4HZ,如果使用单个8b/10b解码模块,很难达到设计要求,所以本设计采用了两个8b10b模块迭代结构,对一组16比特数据同时进行8b10b数据编码。

这样处理就可以将编码数据的数据率降低一半,数据位宽增大一倍,提高了系统的可靠性和高数据率的扩展。

由8blob编码规则的约束,在两个编码模块之间存在RD值反馈与时钟反相。

8b10b编码模块一在模块上升沿输出编码结果和相应的RD值,此时将RD值反馈到8b10b编码模块二,由于8b10b编码模块二与8b10b编码模块一使用时钟有90°相移,所以在8b10b编码模块上升沿到来时,正好接收到16比特数据中高8比特数据编码后的RD值,型后续编码,得到正确的编码结果,并将编码后得到的RD值反馈到8blOb编码模块一。

通过16比特20比特解码模块可以得到解码后数据和数据相关信息,并将数据传入20bit-10bit数据解复用模块进行后续处理。

✧20bit-10bit数据解复用模块设计

功能描述:

将由8b10b输出的20bit数据,按照数据的先后顺序,将20bit数据分为两个10bit数据分别输出到FCO层。

实现方法:

由于16bit数据进行8b10b编码的时候,首先编码的是16bit数据中,高8bit数据,然后再编码低8bit数据,,两个8b10b编码模块时钟偏差了90。

,所以本模块的时钟频率为8b10b模块的两倍,使用212M时钟进行数据处理。

在输出数据的时候先输出din_f_8blbenl的10bit数据,然后再输出din_f_8b10ben2的10bit数据。

✧FCl层接收模块划分与逻辑实现

FCl层接收模块如图3-5所示:

FCl层接收模块主要分为了FClRMUX(IO比特到20比特串并转换模块),deel6b20b(2个并行8b10b解码模块),Invalidwordcheck(有效字检测模块),Commacheck(逗号检测模块),sixteen2thirtytwo(16比特到32比特串并转换模块)。

FCI接收模块接收到由SERDES模块发送到当前的10比特并行数据,经过各个模块的转换,最终得到32比特FC2层接收数据,原语信号,原语序列以及有效字检测结果。

16位输出数据的发送时序

1.210bit/20bit串并转换模块设计

在8b10b解码模块之前,为了降低数据率,可以将一路10比特数据进行锁存后输出两路10比特数据,将数据率降低一半,当硬件模块工作在2.12Gbit/s的数据率下,10bit-20bit串并转换模块之前,数据率为212.4Mhz,而经过此模块之后数据率降低为106.2Mhz。

1.320比特16比特解码模块设计

模块功能说明:

将两路并行输入的10bit数据通过两个8b10b解码模块解码后输出两路8bit数据输出,并给出每组10比特数据编码错误和游程值(Disparity)违规的相关信息。

模块内部结构如图3-6所示:

当FC-FS硬件逻辑工作在2G速率下,进入8b/10b模块的数据率是212.4HZ,如果使用单个8b/10b解码模块,很难达到设计要求,所以本设计采用了两个8b10b模块迭代结构,同时对20比特输入数据进行解码。

这样处理就可以将编码数据的数据率降低一半,数据位宽增大一倍,提高了系统的可靠性和高数据率的扩展。

通过20比特16比特解码模块可以得到解码后数据和数据相关信息,并将数据传入下一模块进行后续处理。

1.4逗号检测模块设计

在传输过程中数据逗号出现位型如图3.7所示:

模块功能:

检测FC2中32比特数据起始标志K28.5,并按照K28.5在前的顺序,将两路8比特数据输入转换为一路16比特数据输出,并将结果传送到16bit-32bit复用模块进行后续处理。

实现方法:

在FC-FS协议中规定,在两个FC端口进行通信时,会进行端口之间相互发送原语序列,通过端口状态机进行数据同步。

原语序列由K28.5特殊编码开头,通过16b/20b解码模块得到数据的K28.5标志位来确定,然后内部逻辑进行数据锁存,最后得到正确顺序的16比特数据,将特殊字标志位输出,完成16bit/32bit复用的后续操作。

如果硬件模块工作在212.4Mhz的数据率下,则经过逗号检测模块,数据率降低一倍,变为106.2Mhz。

1.516bit/32bit复用模块设计

模块功能:

将两个时钟周期内输入16比特数据按照K28.5在前的顺序复用为FC2层时钟的一组32比特数据。

并将特殊字标识符同输出数据一同传输到FC2接收模块进行后续操作。

实现方法:

在两个时钟周期内锁存两组由逗号检测模块输入的16比特数据。

通过kin的标志,判断输出32比特数据的顺序。

如果硬件工作在212.4Mhz的数据率下,经过逗号检测模块第一次降低数据率,变为106.2Mhz,最后通过16比特.32bit复用模块,数据率又降低一半,降低到FC2层的数据率53.1Mhz。

经过上面所有模块的功能,FC.FS硬件系统完成了协议中规定的FCl层接收的所有功能,将212.4Mhz数据率的10比特数据转换成为53.1Mhz数据率的32比特数据,并将原语标志位kout,数据有效字标志invalidword传输到FC2层接收模块,进行后续FC2数据操作。

✧FC2层接收端设计

FC-2层接收端要实现的功能主要包括:

序YU/交换管理,注册注销,将单帧数据重组为完整序列,通过FC-2接口递交给FC-4层处理。

图4.5给出了FC2层接收端设计框图,其具体流程如下:

查询接收缓存寄存器,当寄存器帧接收请求标志置1时,说明此时该缓存中已接收到一帧数据待处理,PPC将数据读取到内存中,开始帧处理。

同时寄存器信息包含该帧数据总数,以及帧是否有传输字错误等信息。

一一进行判断,若帧没有发现传输字错误、帧溢出等错误,则进入序列/交换管理阶段,包括:

SOF、EOF判断:

确定帧服务类型和帧在序列中得位置,并设置相应FLAG标

志;

帧头提取:

将光纤通道帧头部分单独提取出来进行帧头解析;

帧头解析:

判断目的地址是否为本端口,不是即丢弃该帧,若是继续判断;

判断源地址与本端口是否已完成N端口注册,若未注册,需先注册,已注册,则继续判断;

判断R_CTL交换类型,属于设备数据帧还是链路服务帧等,若为链路服务注册帧,则进入注册、注销进程,完成注册或注销。

若为设备数据帧则进行TYPE判断;

判断TYPE为何种上层应用,这里为FC-AE-1553协议;

判断OX_ID交换号:

该帧属于新交换,还是已有交换,新交换则建立新的交换状态块,填入交换信息;已有交换,则通过端口地址和交换号查找所属交换状态块,进行交换信息更新;

判断RX_ID:

FC-AE-1553该值均为0xFFFF;

判断F_CTL控制信息,F_CTL确定该帧是属于交换发起者发送或交换响应者发送,序列发起权归属,采用得错误处理策略,在交换中的位置,优先级等重要信息,判断其正确性,并填充/更新交换状态块;

判断SEQ_ID序列号:

该帧属于新序列或已有序列,新序列开辟新序列状态块,已有序列则根据序列号查找到所属序列状态块进行信息更新;

判读SEQ_CNT帧计数:

序列重组必备信息,确定帧在序列中的位置;

DF_CTL判断:

FC-AE-1553中为OxO;

参数域判断:

包含相关偏移量信息,为序列重组提供相关信息。

帧头解析完毕、序列/交换状态块更新完毕后,处理完成。

将正确帧的数据按帧顺序重组为完整序列,填FC-2接口原语(FC-2_SEQUENCE.indication),完成序列递交。

✧FC2层发送端设计

FC-2层发送端要实现的功能主要包括:

序YU/交换管理,注册分析,将FC-4请求的序列数据块划分为帧数据大小,将分配好的帧头与数据组成完整光纤通道帧放入发送缓存中。

图4.6给出了FC2层发送端模块的主要设计流程框图。

根据请求的FC-2接口原语信息(如FC-2_SEQUENCE.request)开始组帧程序,首先判断目的端口地址与本端口是否已完成N端口注册,若未注册,需先注册,已注册,则进行数据分割,将数据块分为帧数据大小,进入序列/交换管理阶段,包括:

目的端口地址填充;

源端口地址填充;

TYPE上层应用类型填充,这里为FC-AE-1553协议:

DF_CTL填充:

FC-AE-1553中为OxO;

F_CTL控制信息填充,FCTL确定该帧是属于交换发起者发送或交换响应者发送,序列发起权归属,采用的错误处理策略,在交换中的位置,优先级等重要信息,FC-2接口原语信息中包含,计算后填充;

优先级填充:

使用优先级,将优先级填入CS_CTL,F_CTL得17bit置1,不使用优先级,则CS_CTL为0x0;

RX_ID填充:

FC.AE.1553该值均为0xFFFF;

R_CTL交换类型填充,与接口原语一致;

分配OX_ID交换号:

该帧属于新交换,则随机为交换分配一个未使用的交换号并建立新的交换状态块,填入交换信息;已有交换,则通过端口地址和交换号查找所属交换状态块,进行交换信息更新;

分配SEQ_ID序列号:

该帧属于新序列或已有序列,新序列则随机为交换分配一个未使用的序列号并开辟新序列状态块,已有序列则根据序列号查找到所属序列状态块进行信息更新;

分配SEQ_CNT帧计数:

序列重组必备信息,确定帧在序列中的位置;按重复计数或连续计数方式分配,同一序列的帧,后一帧比前一帧大l;

参数域填充:

包含相关偏移量信息,为序列重组提供相关信息。

帧头分配完毕,于此同时建立/更新好序Yd/交换状态块,按正确帧的顺序将合适数据与帧头组合完毕,放入发送缓存,并将使用的服务类型信息通知硬件,由硬件添加SOF、EOF。

为新交换、新序列分配的交换号与序列号通过FC2接口原语(FC-2_SEQUENCE_TAG.indication)通知FC-4层。

当一个序列的所有数据均以帧的形式发送完毕,其发送结果:

成功,失败及失败原因通知FC_4层。

1.注册/注销模块

(一)N端口注册请求

N端口会在一个新的交换中发送一个PLOGI帧,端口名的数值大的N端口将发送一个PLOGI,在点对点连接中,只需一个N端口发送PLOGI即可。

注册过程完成了以下内容:

1、设置一个OX-ID。

2、将D.ID设置为目标N端口D,S.ID设置为源N端口ID。

3、净荷中根据需要设置相应的服务参数。

4、指定发起注册的N端口的端口名,节点名。

(二)N端口注册响应

正常的N端口注册响应是返回一个LS-ACC链路服务响应帧,不存在交换机时,可能有以下几种响应类型:

1、返回一个LS-ACC帧,帧的OX_ID等于PLOGI中的OX_ID,公共服务参数域中的N.PORT/F-PORT位置0,这是正常的N端口注册响应,说明注册成功。

LS-ACC的D-ID即为PLOGI中的S-ID;LS-ACC中的S-ID即为PLOGI中的D_ID。

LS-ACC帧内的净荷给出了服务参数设置,一个64位的N端口名,一个64位的节点名。

注册成功后,N端口就可以与远程的N端口之间通信。

2、返回一个P-BSY,说明目标N端口忙,稍后可重新发送PLOGI。

3、返回P-RJT,说明N端口注册被目标N端口拒绝。

P-RJT帧内净荷包含了

拒绝原因码。

若原因码为“不支持的服务类型”,则N端口将换一种服务类型,重新发送PLOGI。

4、收到PLOGI,说明两个N端口注册时发生冲突,若接收到的PLOGI内的N端口名小于自身的N端口名,则发送一个LS—RJT拒绝帧,帧内拒绝原因码为“已经开始注册进程”;否则,直接处理接收到的PLOGI进行注册。

5、若无响应,则表明表示链路出错,进行错误恢复。

使用第三类服务,响应的N端口发送了LS-ACC后,注册结束。

(三)注销

注销过程是指移除所有地服务参数,释放N端口,交换机的资源,N端口注销时,删除了N端口ID。

N端口可以发送LOGO-ELS帧向交换机请求注销。

✧FC4层模块划分与实现

FC-AE-1553映射层实现FC-AE-1553协议功能,完成FC-AE-1553的10种传输类型。

分为NC、NT2种模式工作,NC模式下安排整个网络中的传输过程,NT模式下响应各类数据传输。

✧NC模式管理模块

图4.3描述了NC模式管理模块的设计框图,上层应用通过FC-4接口原语FC-4_exchange.request请求FC-4层发起交换,NC分析该原语,协调发起交换所需的各类资源。

TYPE上层应用分析,这里确定为0x48,FC-AE-1553应用,进入FC-AE-1553处理。

广播/多播/单播判断分类;

进程注册分析:

判断交换2端口间是否已完成进程注册,若未完成,则首先进行进程注册,已完成,则继续判断;

突发模式判断:

普通模式,突发模式一,突发模式二共三种,不同模式下进行的传输类型相应的传输过程有所不同;

传输类型判断:

主要分为NC-NT(s),NT-NC,NT-NT(s)3大类,按各自特点分别进行;

根据各类传输类型,填FC-2接口原语FC-2_SEQUENCE.request,请求发起序列;

等待FC-2_SEQUENCE_TAG.indication,为新交换/新序列分配交换号与序列号;

根据序列发送结果进行下一步骤:

序列发送失败,则填FC.4接口原语FC-4_exchange.reply向上层应用报告交换失败原因;序列发送成功则根据传输类型和剩余数据大小判断是继续发起数据序列还是等待状态序列;

继续发起数据序列则填FC-2_SEQUENCE.request序列请求;

等待状态序列需开启计时器,在计时器时间内未收到相应的FC-2_SEQUENCE_indication则发生超时错误,错误信息报告给上层应用,并根据错误类型判断是否终止交换;若收到FC-2_SEQUENCE.indication,开始序列分析:

检查状态序列并验证扩展头信息,扩展域正确则提取数据,归并于所属交换块中,扩展域信息错误则将错误信息以FC-4接口原语形式(FC-4_exchange.reply)报告给上层应用,并根据错误类型判断是否终止交换。

在整个处理请求过程中,FC-4_exchange.request请求一直保存,作为交换发送的依据,提供交换信息查询。

每发送或接收一个序列,剩余数据信息等同步记录,一旦发送错误,剩余数据信息填入FC-4_exchange.reply中,向应用层报告。

✧NT模式管理模块

图4-4描述了NT模式管理模块的设计框图,NT接收到命令序列后,进行分析,填写FC-4_exchange.request原语,申请发起交换所需的各类资源。

NT接收到FC-2接口原语FC-2_SEQUENCE.indication分析该原语:

TYPE上层应用分析,这里确定为0x48,FC-AE-1553应用,进入FC-AE-1553

处理。

判断R_CTL,确定序列类型:

命令序列或数据序列;

命令序列:

收到命令序列即为新交换的第一个序列

命令扩展帧头信息分析,确定传输类型,RDMA,突发模式,请求数据大小等具体信息;

开辟FC-4_exchange.request请求原语和FC-4_exchange.reply应答原语,填入交换相应控制信息,如交换号,传输类型,RDMA,突发模式,请求数据大小等;

若命令扩展头出现错误,则向上层应用提交接口原语(FC-4_exchange.reply),报告错误,若正确,则提取序列数据,归并与所属交换块中;

数据序列:

交换中间序列,分析FC-2_SEQUENCE.indication原语,提取序列数据归并于相关交换块中,并从FC-4_exchange.request请求原语中查询传输类型,突发模式等信息,由此判断下一步是继续等待数据序列还是发送状态序列/数据序列;

组状态/数据序列请求原语FC-2_SEQUENCE.request,请求发起序列;

等待FC-2_SEQUENCE_TAG.indication;为新序配分配序列号;

根据序列发送结果进行下一步骤:

序列发送失败,则填FC-4接口原语(FC-4_Exchange.reply)类型和剩余数据大小判断是开始等待数据序列还是结束交换向上层应用报告状态;

等待数据序列需开启计时器,在计时器时间内未收到相应的FC-2_SEQUENCE.indication则发生超时错误,错误信息报告给上层应用,并根据错误类型判断是否终止交换;若收到FC-2_SEQUENCE.indication,开始序列分析;

在整个处理请求过程中,FC-4_exchange.request请求一直保存,作为交换发送的依据,提供交换信息查询。

每发送或接收一个序列,剩余数据信息等同步记录,一旦发送错误,剩余数据信息填入FC-4_exchange.reply中,向应用层报告。