公共自行车租赁系统混合锁桩设计与实现第4章.docx

《公共自行车租赁系统混合锁桩设计与实现第4章.docx》由会员分享,可在线阅读,更多相关《公共自行车租赁系统混合锁桩设计与实现第4章.docx(11页珍藏版)》请在冰豆网上搜索。

公共自行车租赁系统混合锁桩设计与实现第4章

混合锁桩硬件设计

上一章详细介绍了混合锁桩整体设计,从硬件和软件两方面进行分析,完成了主要芯片的选型和软件总体设计。

混合锁桩硬件设计是基于充电桩的设计,本章按照功能模块设计硬件电路,给出了各功能模块的详细硬件设计,从PCB板布局布线和预防电磁干扰考虑,完成了PCB板的制作。

4.1混合锁桩硬件详细设计

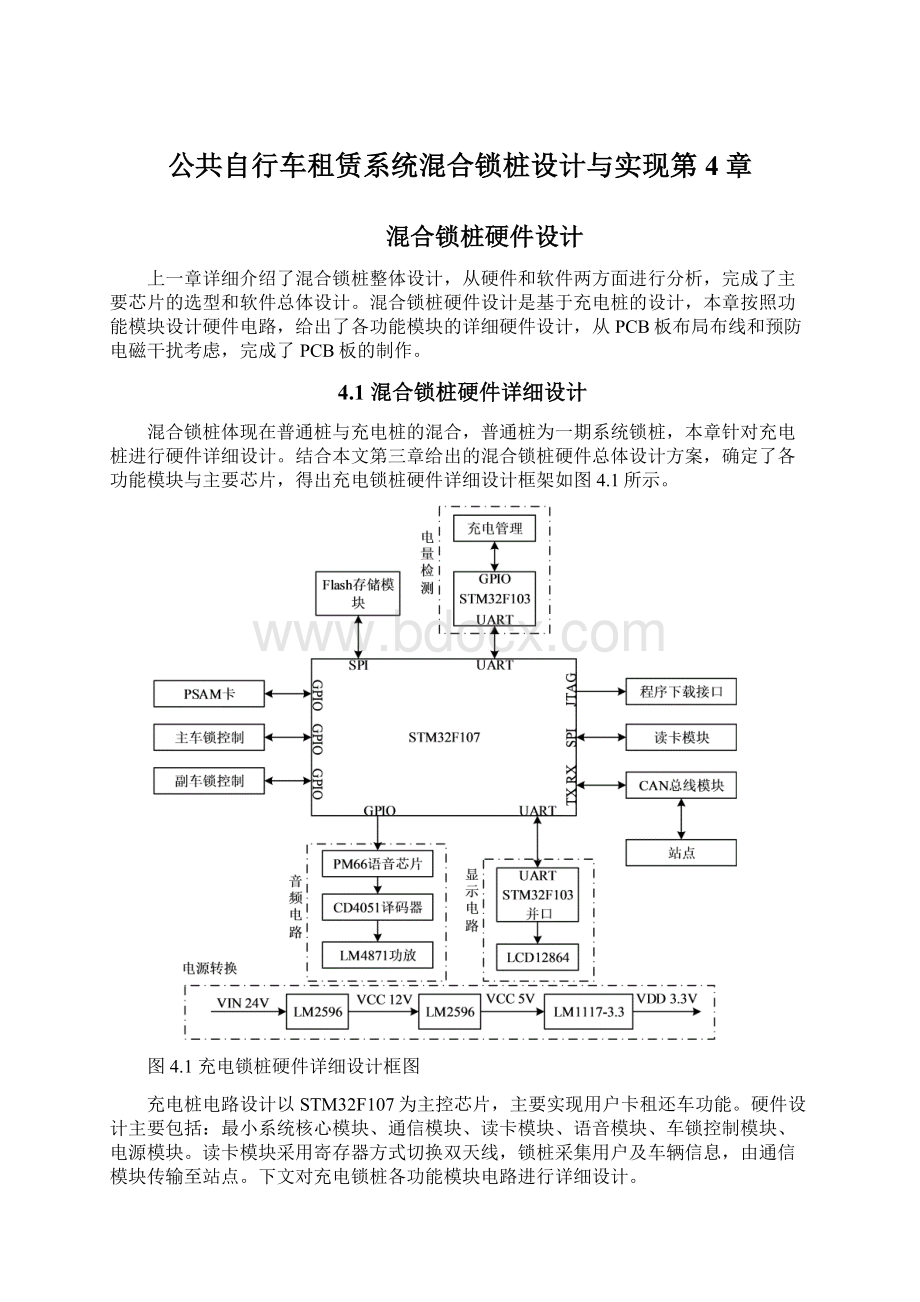

混合锁桩体现在普通桩与充电桩的混合,普通桩为一期系统锁桩,本章针对充电桩进行硬件详细设计。

结合本文第三章给出的混合锁桩硬件总体设计方案,确定了各功能模块与主要芯片,得出充电锁桩硬件详细设计框架如图4.1所示。

图4.1充电锁桩硬件详细设计框图

充电桩电路设计以STM32F107为主控芯片,主要实现用户卡租还车功能。

硬件设计主要包括:

最小系统核心模块、通信模块、读卡模块、语音模块、车锁控制模块、电源模块。

读卡模块采用寄存器方式切换双天线,锁桩采集用户及车辆信息,由通信模块传输至站点。

下文对充电锁桩各功能模块电路进行详细设计。

4.2锁桩硬件电路设计

14.2.1锁桩最小系统设计

STM32单片机最小系统由单片机、时钟电路、复位电路、电源电路组成[23]。

下面对最小系统电路作简要分析。

1.时钟电路

STM32F107芯片引脚OSC_IN(12脚)和OSC_OUT(13脚)分别为芯片内部振荡电路输入端和输出端。

外接定时元件(一个石英晶体和两个电容),内部振荡器可发生自激振荡。

时钟电路中石英晶振为25MHz,两个电容为33pF/10V。

图4.2电源电路

2.复位电路

复位电路的目的是让整个系统重新启动,强制系统恢复到起始状态,促使最小系统稳定工作。

3.电源电路

锁桩供电电压为24V,锁止器工作电压与锁桩供电电压一致,控制电压为5V,STM32单片机工作电压为3.3V。

因此,设计多级电源转换电路。

入口电压由24V转换至5V,再由5V转至3.3V。

考虑到24V直接转5V压降过大,中间增加一级12V过度电路,锁桩电源电路见图4.2。

为方便测试,在电源转换输出端口预留12V、5V、3.3V测试点,测试点后级设计0欧姆电阻,调试电源电路时不焊接。

24.2.2射频识别模块

RFID(RadioFrequencyIdentification,射频识别)读卡器由射频读写芯片FM1702、天线和外围电路组成,天线发射电磁能量为卡片供能[24,25]。

该芯片通过SPI接口与控制器连接,同时驱动两路射频天线。

双天线分别控制车辆卡与用户卡的读写,用于缩短租还车时间。

读卡器硬件连接如图4.3所示。

图4.3FM1702SL硬件连接图

1.读卡器天线设计

天线阻抗匹配是天线设计的难点。

根据天线尺寸经估算公式计算线圈电感,查找线圈电感与匹配电容容值对应关系,以此容值作为天线调谐起始值。

天线电感估算公式为:

式中,

——天线线圈电感

——天线一圈导线的长度

——天线线圈宽度

——天线形状常数(环形天线K=1.07,矩形天线K=1.47)

——线圈匝数

大天线为矩形天线,

,

,

,

,大天线线圈电感

;小天线为环形天线

,

,

,

,小天线线圈电感

。

表4.1线圈电感与匹配电容取值

天线线圈电感/uH

Cs/pf

Cp1/pf

Cp2/pf

1.3

15

180

180

1.4

15

150

180

1.5

15

150

150

1.6

15

120

150

根据大小天线线圈电感查找线圈电感与匹配电容对应表,如表4.1所示。

获得大天线起始容值:

Cs:

15,Cp1:

120,Cp2:

150;小天线起始容值:

Cs:

15,Cp1:

180,Cp2:

180,电容材料选用NPO电介值且误差为±2%。

天线采用PCB线圈,天线电路如图4.5所示。

天线设计时,因Cp电容影响天线谐振频率,将此电容设计为两并联电容。

天线调谐时,固定某电容容值,对另一电容微调。

小天线运用环境较大天线更恶劣,Cs电容也设计为两电容并联,分两级微调,提高天线参数调谐精度。

天线电路设计如图4.4所示(原理图标号唯一,大天线Cs标号为C1,Cp1标注为C2,Cp2标注为C3)。

图4.4天线设计

2.读卡器滤波电路

天线匹配电路调节天线发射谐振频率至13.56Mhz,匹配发射电路电阻至读卡芯片输出电阻附近,使得天线部分获得最大功率,提升读卡距离[26]。

图4.5滤波电路

滤波电路设计如图4.5所示。

读卡芯片内部携带TX1和TX2两路发射信号,大小天线共用RX接收端,接收端分别从大小天线处接入820Ω电阻作为分压器。

34.2.3CAN总线通信模块

CAN总线通信设计包括CAN控制器和收发器。

本设计中STM32主控自带CAN总线控制器。

CAN收发器是CAN控制器和物理总线之间的接口,将CAN控制器的逻辑电平转换为CAN总线的差分电平,在两条平行总线上传输数据。

其选型主要考虑收发器的驱动能力(最大节点数)、信号电平、通信速率和抗干扰能力。

收发器根据通信速率的不同,分为隔离收发器、高速收发器和容错收发器。

本节针对目前市场上主流的CAN总线收发器做对比分析,如表3.1所示。

同时,结合项目应用场景,选择最合适的收发器件。

表4.2CAN总线收发器比较

芯片型号

节点数

通信速率/Kbps

分类

备注

CTM1051

110

隔离收发器

具有隔离、静电保护能力

TJA1050

110

50-1024

高速收发器

支持较高的CAN通信速率

PCA82C251

110

0-50

通用收发器

支持较低的CAN通信速率

本设计选用带隔离、静电保护的收发器CTM1051,该芯片具有较高的抗干扰能力,工作温度范围在-40℃—+85℃,满足环境温度和静电防护的需求。

收发器CTM1051负责电平转换,自带保护电路,其工作电压为为4.5V~5.5V(DC5.0V±10%),CAN总线设计如图4.6所示。

图4.6CAN总线收发器设计

引脚TXD和RXD分别为数据收发引脚,CANH、CANL分别为CAN总线高低电平接口[27,28]。

为避免信号在电缆中传播时产生反射,引起电平变化,在CAN总线终端并联120欧姆“终端电阻”,降低信号传播反射[29]。

44.2.4PSAM智能卡接口模块

PSAM(PurchaseSecureAccessModule,销售点终端安全存取模块)卡有两类(A类和B类),通过供电电压区分。

A类为5V供电,B类为3.3V供电,本设计为B类PSAM卡[30]。

PSAM智能卡接口设计如图4.7所示。

图4.7PSAM智能卡接口电路

54.2.5存储模块设计

站点以锁桩编号为依据实现锁桩的动态管理,锁桩编号与锁桩位置一一对应。

首次启动时,管理人员依次为锁桩分配编号,安装位置决定锁桩编号顺序。

编号分配后固化于锁桩内部,掉电重启后不丢失、不更改。

外挂存储设备能达到锁桩编号存储的目的,Flash存储芯片具有高效永久存储能力,通过SPI接口即可读写,FLASH存储模块硬件连接如图4.8所示。

图4.8FLASH存储模块硬件连接图

64.2.6串口通信模块设计

原显示板与锁桩通信方式是串口。

为提高显示板的通用性,实现通信接口兼容,显示板和电量板均采用串口通信。

STM32处理器自带多路串行接口,输出TTL(TransistorTransistorLogic,逻辑电平)电平经SP3232芯片转换。

显示板和充电板分别实现屏幕显示与电量检测,由锁桩板统一供电。

因此,连接接口除发送(TX)与接收(RX)引脚外,设计5V电源。

串口通信接口电路如图4.9所示。

图4.9显示板与充电板串口通信设计

74.2.7语音模块设计

语音是判断租还车成功的重要手段,常见支持语音拷贝功能的语音芯片有ISD1760、PM66,本节对两款语音芯片做对比分析。

表4.3语音芯片比较

芯片型号

采样率

烧录方式

拷贝方式

ISD系列

外部振荡电阻调节采样率,采样率固定

手动计算语音地址分布,依次烧录语音文件

烧录语音时地址分布连续才能拷贝

PM66系列

软件调节采样频率,采样率可变

依据音频文件大小自动分配录音地址空间

直接拷贝

从语音拷贝难易程度考虑,语音芯片选用较为成熟的PM66,该芯片有PWM(IpulseWidthModulation,脉冲宽度调制)和DAC(DigitaltoAnalogConverter,数字模拟转换器)两种输出方式。

PWM能直接推动8欧姆0.5W喇叭;DAC需要外接功放器件。

根据3.1节混合锁桩需求分析知,锁桩分时段自主调节音量大小,DAC输出方式能满足设计要求。

在语音芯片后端与功放芯片前端设计译码电路,通过译码器选择功放电路阻值,控制功放芯片LM4871输出增益,达到音量控制的目的。

语音模块硬件电路设计如图4.10所示。

图4.10语音模块硬件连接图

84.2.8锁止器控制模块设计

锁止器控制接口电压为5V,主控芯片控制引脚电压3.3V,无法直接控制锁止器工作。

三极管的开关特性能很好解决控制端电压不匹配问题,双锁硬件控制电路如图4.11所示。

LOCK为高电平时,S9013三极管导通,CTRL接口下拉至低电平,此时锁止器弹出,状态信号ON为高电平,OFF为低电平;同理,LOCK为低电平时,S9013三极管截止,CTRL接口拉高至5V,锁止器弹入,状态信号ON为低电平,OFF为高电平。

图4.11锁止器控制电路

4.3PCB设计分析

本章4.2节完成PCB设计前期准备,PCB设计主要考虑电路板层面、元器件封装、铜模导线、过孔、焊盘、地与电源线的绘制,元器件、去耦电容放置以及电磁兼容控制等设计问题。

本文设计的PCB包含差分电路、晶振电路、退耦电路、模拟信号以及数字信号,在设计时考虑差分对布线、数字电源和模拟电源的隔离,射频阻抗匹配以及电磁兼容等。

14.3.1PCB布局设计

锁桩PCB板为两层设计,机械尺寸:

100mm×100mm。

首先,确定定位安装,然后合理布局电路元器件,最后完成走线工作。

PCB布局是布线的基础,在布局时按照功能模块就近集中原则[31],考虑外设芯片封装尺寸和通信接口电路。

根据锁桩板尺寸调整布局,缩短走线长度。

读卡模块和语音模块包含模拟电路,与数字电路分开放置。

CAN总线差分信号对平行走线,电源模块与其它芯片、器件保持一定间距,处理器晶振和读卡器晶振放置位置紧靠时钟输入引脚。

锁桩PCB板布局如图4.12所示。

(1)电源的布局主要考虑芯片散热,以及对其他芯片的干扰,电源模块放置在左侧,与其他模块隔离。

(2)时钟电路靠近芯片时钟引脚,缩短时钟电路的连线[32]。

(3)数字电路芯片的电源和地之间放置IC去藕电容,电容靠近芯片电源引脚。

(4)处理器模块居中设计,外围模块围绕处理器布局。

图4.12锁桩PCB布局

24.3.2PCB板电磁干扰设计

本文设计的RFID读卡器包含13.56Mhz射频信号,CAN总线通信电路包含差分信号,其PCB具有潜在的电磁干扰,与纯数字电路设计有所区别。

射频天线布线时设定特征阻抗为50ohms,采用圆弧角布线,为避免磁场涡流效应,不对天线正反面敷铜[33]。

差分信号是平行、成对、等长信号,其抗干扰能力强。

CAN信号线采用差分走线,能相互抵消对外辐射电磁场,抑制电磁干扰。

布线时同层走线,设置差分信号线宽0.5mm,线间距0.5mm,与其他走线保持同等间距。

本设计根据PCB设计规则和注意事项,用AltiumDesigner13软件完成了锁桩板和读卡器天线的PCB绘制,分别如图4.13、图4.14所示。

图4.13锁桩PCB板

图4.14天线PCB设计

4.4本章小结

混合锁桩硬件设计是基于充电桩的设计,本章主要完成充电锁桩硬件电路设计。

首先按照功能模块设计硬件电路;然后根据功能模块进行详细设计,并完成了原理图的绘制;最后结合布局布线要求,完成锁桩板和大小天线PCB板的绘制。