最新智力抢答器电路.docx

《最新智力抢答器电路.docx》由会员分享,可在线阅读,更多相关《最新智力抢答器电路.docx(9页珍藏版)》请在冰豆网上搜索。

最新智力抢答器电路

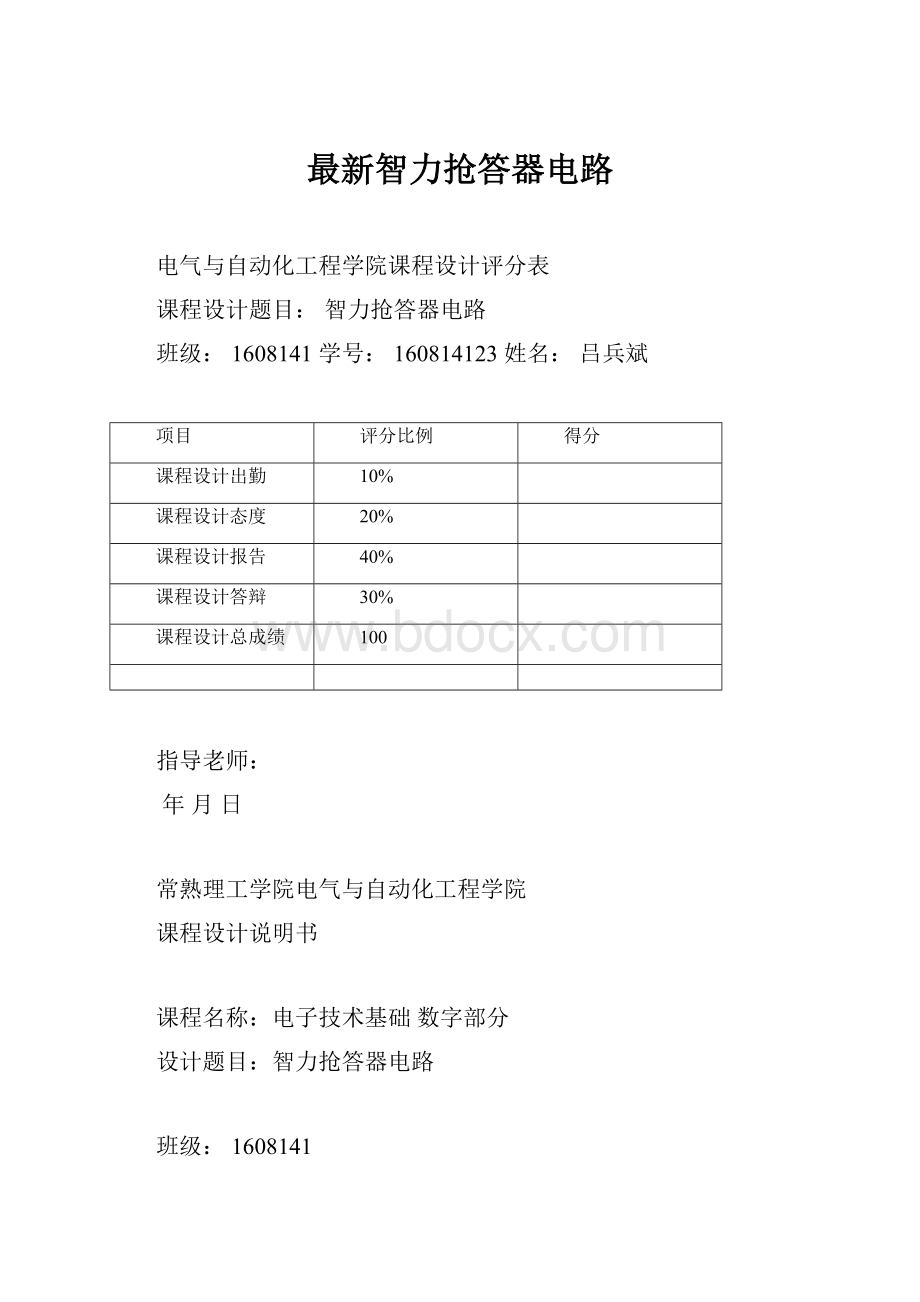

电气与自动化工程学院课程设计评分表

课程设计题目:

智力抢答器电路

班级:

1608141学号:

160814123姓名:

吕兵斌

项目

评分比例

得分

课程设计出勤

10%

课程设计态度

20%

课程设计报告

40%

课程设计答辩

30%

课程设计总成绩

100

指导老师:

年月日

常熟理工学院电气与自动化工程学院

课程设计说明书

课程名称:

电子技术基础数字部分

设计题目:

智力抢答器电路

班级:

1608141

姓名:

吕兵斌

学号:

160814123

指导老师:

设计时间:

2016-5-31

1.四路智力抢答器的组成框图……………………………4

2.抢答电路…………………………………………………5

3.控制部分…………………………………………………8

4.计时电路…………………………………………………9

5.报警电路…………………………………………………9

6.心得体会…………………………………………………10

一·四路智力抢答器的组成框图

二·抢答电路

抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,禁止其他选手抢答。

当处于工作状态是,有选手抢答时,按键信息送至优先编码器,经由优先编码器后送至锁存器锁存,然后送至译码显示电路显示,同时,控制电路将送一个信号到优先编码器使它停止工作。

74LS148

74LS148是8线-3线优先编码器,共有54/74148和54/74LS148两种线路结构型式,将8条数据线(0-7)进行3线(4-2-1)二进制(八进制)优先编码,即对最高位数据线进行译码。

利用选通端(EI)和输出选通端(EO)可进行八进制扩展。

0-7编码输入端(低电平有效)

EI选通输入端(低电平有效)

A0、A1、A2三位二进制编码输出信号即编码输出端(低电平有效)

GS片优先编码输出端即宽展端(低电平有效)

EO选通输出端,即使能输出端

输入

输出

EI

0

1

2

3

4

5

6

7

A2

A1

A0

GS

EO

H

X

X

X

X

X

X

X

X

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

L

L

X

X

X

X

X

X

X

L

L

L

L

L

H

L

X

X

X

X

X

X

L

H

L

L

H

L

H

L

X

X

X

X

X

L

H

H

L

H

L

L

H

L

X

X

X

X

L

H

H

H

L

H

H

L

H

L

X

X

X

L

H

H

H

H

H

L

L

L

H

L

X

X

L

H

H

H

H

H

H

L

H

L

H

L

X

L

H

H

H

H

H

H

H

H

L

L

H

L

L

H

H

H

H

H

H

H

H

H

H

L

H

74LS279

四/R-/S锁存器

简要说明:

279为四个/R-/S锁存器,共有54/74279和54/74LS279两种线路结构型式,其

主要电器特性的典型值如下(不同厂家具体值有差别):

型号tPDPD

54279/7427912ns90mW

54LS279/74LS27912ns19mW

四个锁存器中有2个具有2个置位端(/SA,/SB)。

当/S为低电平,/R为高电平时,输出端Q为高电平。

当/S为高电平,/R

为低电平时,Q为低电平。

当/S和/R均为高电平时,Q被锁存在已建立的电平。

当/S和/R均为低电平时,Q为不稳定的高电平状态。

对/SA和/SB,/S的低电平表示/SA和/SB只要有一个为低电平,/S的高电平表

示/SA和/SB均为高电平。

引出端符号:

1Q~4Q输出端

/1S~/4S置位端(低电平有效)

/1R~/4R复位端(低电平有效)

74LS48

7段显示译码器74LS48是输出高电平有效的译码器

三·控制部分

控制电路的作用是当主持人控制开关按下时,优先编码器工作,译码电路处于消隐状态,不显示数字。

整个系统处于等待工作状态。

有选手抢答时,显示选手编号,给予优先编码器一个禁止工作的信号,让他人无法作答。

当主持人按下控制开关时,系统重新回到等待工作状态。

74LS74

双上升沿D触发器(有预置、清除端)

引出端符号1CP、2CP

时钟输入端1D、2D

数据输入端1Q、2Q、1Q_、2Q_

输出端CLR1、CLR2

直接复位端(低电平有效)PR1、PR2

直接置位端(低电平有效)

四·计时电路

当有人抢答时,停止计数并显示此时的倒计时时间;如果没有人抢答,且倒计时时间到时,BO输出低电平到时序控制电路,以后选手抢答无效。

74HC192

CPU为加计数时钟输入端,CPD为减计数时钟输入端。

LD为预置输入控制端,异步预置。

CR为复位输入端,高电平有效,异步清除。

CO为进位输出:

1001状态后负脉冲输出

BO为借位输出:

0000状态后负脉冲输出。

4511BD

七段显示器译码器

五·报警电路

报警电路的主要作用是提醒主持人,有选手抢答。

报警电路主要由单稳态触发器74121及其一些外围电路组成。

工作原理当魔耀选手抢答时,74121的A1端为高电平,74121保持稳态,即输出端Q为低电平,与门关闭,报警不能通过,没有声响。

当有选手抢答时,单稳态触发器74121的A1端输入一个下降沿触发状态,输出Q出现一个高电平脉冲,高电平使与门短暂导通,发出1Khz的报警,提示有选手抢答。

使用单稳态触发器的主要目的是控制报警时间。

74121

74121构成的单稳态触发器也是由或非门和非门构成的微分型单稳态触发器

六·心得体会

这一课程设计使我们将课堂上的理论知识有了进步的了解,并增强了对数字电子技术这门课程的兴趣。

了解了更多电子元件的工作原理,但同时也暴露出我在知识上掌握不足等缺点。

其次在此次设计过程中由于我们频繁的使用一电子设计软件如:

Multisim等,因此使我熟悉了软件的使用,同时在电脑的电子设计和绘图操作上有了进一步提高。

加上在设计过程中遇到了一些问题,使得我得查找相关资料,从而增长知识的同时增强解决问题和动手的能力,锻炼我做事细心、用心、耐心的能耐。

这一课程设计,使我向更高的精神和知识层次迈向一大步。

所以在以后的学习生活中,我会努力学习,培养自己独立思考的能力,积极参加多种设计活动,培养自己的综合能力,从而使得自己成为一个有综合能力的人才而更加适应社会。