半导体制程及摩尔定律综述.docx

《半导体制程及摩尔定律综述.docx》由会员分享,可在线阅读,更多相关《半导体制程及摩尔定律综述.docx(14页珍藏版)》请在冰豆网上搜索。

半导体制程及摩尔定律综述

神秘的处理器制程工艺

摩尔定律指导集成电路(IC,IntegratedCircuit)工业飞速发展到今天已经40多年了。

在进入21世纪的第8个年头,各类45nm芯片开始批量问世,标志着集成电路工业终于迈入了低于50nm的纳米级阶段。

而为了使45nm工艺按时“顺产”,保证摩尔定律继续发挥作用,半导体工程师们做了无数艰辛的研究和改进—这也催生了很多全新的工艺特点,像大家耳熟能详的High-K、沉浸式光刻等等。

按照业界的看法,45nm工艺的特点及其工艺完全不同于以往的90nm、65nm,反而很多应用在45nm制程工艺上的新技术,在今后可能贯穿到32nm甚至22nm阶段。

今天就让我们通过一个个案例,来探索一下将伴随我们未来5年的技术吧。

你能准确说出45nm是什么宽度吗?

得益于厂商与媒体的积极宣传,就算非科班出身,不是电脑爱好者的大叔们也能知道45nm比65nm更加先进。

但如果要细问45nm是什么的长度,估计很多人都难以给出一个准确的答案。

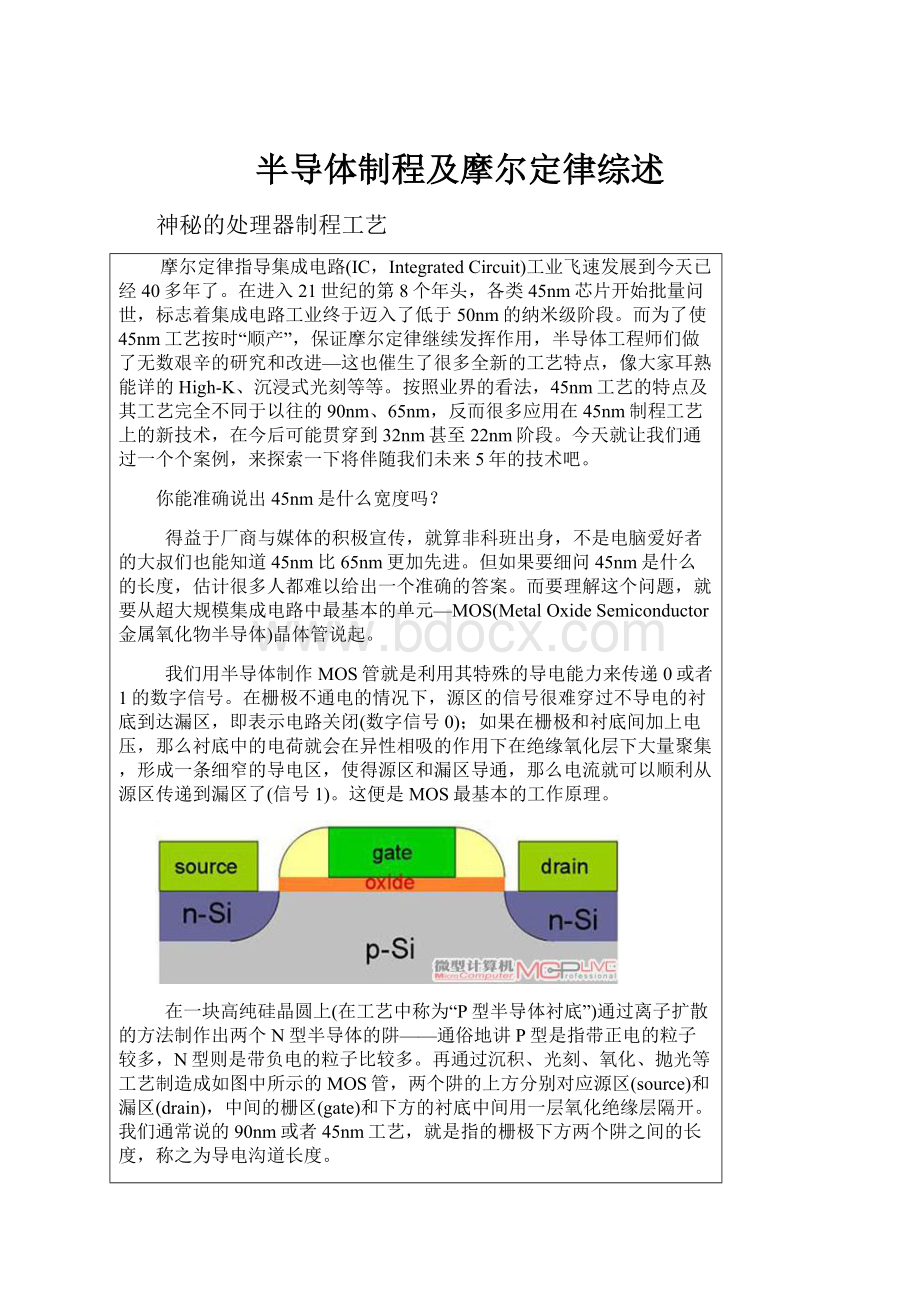

而要理解这个问题,就要从超大规模集成电路中最基本的单元—MOS(MetalOxideSemiconductor金属氧化物半导体)晶体管说起。

我们用半导体制作MOS管就是利用其特殊的导电能力来传递0或者1的数字信号。

在栅极不通电的情况下,源区的信号很难穿过不导电的衬底到达漏区,即表示电路关闭(数字信号0);如果在栅极和衬底间加上电压,那么衬底中的电荷就会在异性相吸的作用下在绝缘氧化层下大量聚集,形成一条细窄的导电区,使得源区和漏区导通,那么电流就可以顺利从源区传递到漏区了(信号1)。

这便是MOS最基本的工作原理。

在一块高纯硅晶圆上(在工艺中称为“P型半导体衬底”)通过离子扩散的方法制作出两个N型半导体的阱——通俗地讲P型是指带正电的粒子较多,N型则是带负电的粒子比较多。

再通过沉积、光刻、氧化、抛光等工艺制造成如图中所示的MOS管,两个阱的上方分别对应源区(source)和漏区(drain),中间的栅区(gate)和下方的衬底中间用一层氧化绝缘层隔开。

我们通常说的90nm或者45nm工艺,就是指的栅极下方两个阱之间的长度,称之为导电沟道长度。

上图中给我们勾勒出来的是一个NMOS,当栅极接正向电压时,NMOS会导通。

事实上还存在另外一种PMOS,其性质完全相反,当栅极接负电时,通过在绝缘区下方聚集正电荷来导通。

在实践中,工程人员很快就发现了单个MOS管在作为逻辑电路导通时,会有源源不断的电流通过,这使得MOS管功率居高不下。

而事实上我们只需要传递信号就行了,无论是用电流,又或者是用电压方式,而不需要MOS管有较高的功耗。

为了降低MOS管的工作功耗,可科学家们又开发了CMOS(ComplementaryMetal-OxideSemiconductor互补金属氧化物半导)电路。

CMOS的电路结构

物如其名,CMOS中包含NMOS和PMOS各一个,并且串联在一起。

由于PMOS和NMOS的导通特性正好相反,因此无论什么时候都只有一个MOS管导通,另一个必然关闭。

这样就起到了传递电压信号,但是无电流功的产生。

理论上CMOS的静态功耗应该为0,但是受材料和制造工艺的限制,CMOS的实际功耗却是不能忽略不计的,这样也就有了后面的各种改良工艺。

High-K工艺和Low-K工艺为什么能够共存?

在步入45nm生产工艺之后,英特尔高调宣布引入High-K工艺以降低芯片功耗,那与此同时,是不是意味着已经使用多年的Low-K工艺要被淘汰呢?

很多人都会有这样的想法,因为从名字上看,二者是完全相反的两个极端。

其实真正的情况并不是那么回事,两个工艺完全用在不同的地方,所要实现的功能也大相径庭。

要解释清楚这个问题,我们就要先弄清楚“K”是什么意思。

电容的物理学描述是C=Q/U,即每升高1V电压,电容中增加的电量。

而在实际电路中C正比于K/D,其中K为绝缘介质的介电常数单位,D是两电极之间的距离。

这样我们就可以看清楚Low-K工艺的发展历程。

电容的基本组成结构要求两端是导体,中间是绝缘体。

由于电容的存在,要改变两导体极板之间的电势差(即相对电压大小)就要先给电容充放电,才能让电压稳定下来,这势必会给信号造成延迟。

我们知道芯片上不仅仅只有MOS管,还有无数连接各个MOS管的导线,早先这些导线使用铝材料(Al)来制作,后来改用铜(Cu)互连提供更低的电阻。

问题就出在这些导线上面,两根距离很近的导线再加上中间的绝缘物,实际上已经组成了一个电容(专业名称叫做“寄生电容”)。

当半导体工艺还处在0.25μm以前时,导线之间的距离D很大,寄生电容很小,所以两条导线中的信号一直是井水不犯河水。

但是随着MOS管的逐渐增多,导线间的距离越来越短,寄生电容的影响越来越大—两根导线之间都是0电压,突然一根导线中的电压要从0上升到1,这时由于寄生电容的存在,上升过程就变得相对缓慢。

这种延迟现象轻则拖慢整个电路的数据传递速度,严重时会造成数值读取错误,影响高频电路的正常工作。

由于寄生电容的影响,本该瞬间完成的信号变化被严重滞后了。

为了降低信号线相互之间的串扰,工程师们找到了一种碳掺杂氧化物(CDO,CarbonDopedOxide)。

这种材料的介电常数为3K,要低于二氧化硅4.2K的介电值。

用新材料来充当导线之间的“填充物”,进而减少寄生电容对芯片的影响,让信号在芯片中的传递更加快速。

介绍完Low-K之后,再来看High-K。

需要大家注意的是,High-K工艺是针对MOS管的改进,而不是导线电路。

这里我们再来引入一个“阈值电压(Vt)”的概念。

顾名思义,阈值电压就是指使MOS管导通时加在栅极的最小电压,如果栅电压低于这个电压,MOS管将关闭。

常识告诉我们,要将栅极电压从0提升到Vt,或者从Vt降到0都是需要时间的,如果这个过程需要10ns,那么也就意味着这个MOS管一秒内最多变化1亿次,即MOS管最快只能有100MHz的频率。

有没有办法加快MOS开关的速度呢?

当然有!

而且有两种方法,其一是增大栅极电压,不过这么做的副作用是功率迅速增大,这是我们绝对不能接受的;另一种则是降低阈值电压,让MOS管更容易开关。

在这种思路下,CPU的工作电压从Pentium4时期的1.3V一直降到酷睿2时期的最低0.765V。

MOS管在电子显微镜下的剖面图

仔细研究之后,我们会发现导体栅极、绝缘层、不绝缘的衬底也能形成一个类似电容的模型。

而且如果这个电容值越大,那么同样的栅极电压就能吸附更多的电荷,提高MOS管导通的速度。

在这种思维的指导下,随着工艺的进步,二氧化硅绝缘层的厚度不断被减小。

到90nm工艺时,二氧化硅绝缘层的厚度已经做到1.2nm,仅仅5个原子厚。

极薄的二氧化硅层带来了MOS管速度的提升,也不可避免地助长了栅极漏电流,因为这么薄的“绝缘层”已经失去了绝缘的能力,大量电荷穿越二氧化硅层,通过衬底溜走。

最终的结果就像是90nm的Prescott核心的Pentium4处理器,工作频率接近4GHz,同时功率也近140W。

越过90nm门槛之后,单纯依靠缩小绝缘层厚度来提高MOS管开关速度已经行不通了。

于是科学家们拿自半导体工业诞生几十年来都未曾碰过的绝缘层介电常数K开刀了,目标就是充当绝缘介质的二氧化硅层。

在45nm生产工艺中,Intel的工程师开始使用一种新型的基于铪(Hr)的化合物作为绝缘层材料。

这种High-K物质能够在厚度不变的情况下提供更大的介电能力,从而帮助MOS管运行在更高的频率之上。

由于铪化合物的特殊分子结构,其绝缘能力达到传统二氧化硅的10000倍,即使是未来将绝缘层厚度降低到0.1nm时,也能充分履行绝缘的职责。

为了配合新的High-K绝缘层,栅极材料也做了更新,抛弃了和新绝缘层结合不好的多晶硅,改用了新的全金属材料。

故此,Intel的High-K技术全称为HKMG技术(High-KMetalGate高介电金属栅)。

HKMG技术让Intel的45nm的酷睿2处理器彻底扔掉了发热量大的毛病,同时其频率提升能力也强于65nm的酷睿2,无论是从性能还是功耗上讲都重新走到了业界前面。

为什么AMD(AdvancedMicroDevice)到目前仍没有使用High-K材料?

有的朋友会纳闷,为什么处理器另一阵营的AMD到现在都没有使用High-K,却能很好地控制CPU的功耗呢?

这就要归功于AMD自Athlon时代就开始使用SOI工艺。

SOI是SiliconOnIsolator的缩写,即绝缘体上的硅技术。

和传统的纯硅晶圆不同,SOI工艺使用的晶圆底部是一层绝缘层。

正是这层绝缘体切断了上方MOS管漏电流的回路,使得基于SOI技术的芯片天生就有抵抗漏电流的本事。

Low-K与High-K的区别

正因如此AMD这么多年来,都不需要考虑太多漏电流的问题。

不过按照计划,AMD将在32nm时导入High-K技术,以提高栅极控制能力。

由于SOI技术来自IBM技术联盟,而IBM出于压制Intel考虑,从未将SOI技术授权给后者,才使得Intel不得不自行开发High-K技术。

出水蛟龙——沉浸式光刻

沉浸式光刻是AMD在45nmPhenomⅡ处理器生产中最新应用的技术之一,其区别于过去干式光刻最大的特点就是整个光刻的过程并不是发生在空气中,而是沉浸在一种光学折射率较大的透明液体中。

如果按照常识去思考,也许我们只要提高掩模板的分辨率,不就能在硅片上“刻画”出更多的MOS管来吗?

从宏观上讲这是完全正确的,但不要忘了在微观的半导体制造工艺中,情况会有极大的不同。

你知道什么是光刻吗?

光刻技术是在一片平整的硅片上构建半导体MOS管和电路的基础,这其中包含有很多步骤与流程。

首先要在硅片上涂上一层耐腐蚀的光刻胶,随后让强光通过一块刻有电路图案的镂空掩模板照射在硅片上。

被照射到的部分(如源区和漏区)光刻胶会发生变质,而构筑栅区的地方不会被照射到,所以光刻胶会仍旧粘连在上面。

光刻的过程

接下来就是用腐蚀性液体清洗硅片,变质的光刻胶被除去,露出下面的硅片,而栅区在光刻胶的保护下不会受到影响。

随后就是粒子沉积、掩膜、刻线等操作,直到最后形成成品晶片。

如果受到保护的栅区的光刻胶留下来的宽度是130nm,那么最终做出来的MOS管大致就是130nm;同理,45nm技术就是最初栅极上留下大约45nm宽度的光刻胶。

由此可见,如果整套光刻设备的分辨率越高,它能够在晶片上定位出更细微的投影,最终就能制造出更小的MOS管。

半导体工艺的更新必然伴随着光刻设备的升级,其目的就是提高分辨率。

掩模板的缝隙以及投射在晶片上的阴影已经很小,这就会引发光波自身的衍射和干涉现象,导致明暗的界限不再那么分明。

这样一来,就不能完成前面提到的源区、漏区以及栅区的区分标定工作,最终MOS管的尺寸和性能无法达到设计要求。

如果这种模糊现象进一步加剧,就会使得源区与漏区的光影基本重叠在一起,栅区无法制造,整个晶圆也就彻底报废了。

晶圆曝光过程中会因为光的衍射问题而报废

因此,最大限度消除阴影就成了提高光刻分辨率的重中之重。

根据光的传播汇聚理论,有一个光学中计算最小分辨率的公式:

R=k1λ/nθ(瑞利判据)。

R代表可分辨的最小尺寸(对于光刻技术来说,自然越小越好),k1是工艺常数,λ是光波波长,n为光的折射率(空气中光折射率为1),θ为两点夹角。

在这个公式中,k1不可变,θ夹角也没有大幅提高的可能。

因此提高分辨率,减小R的首选工作就是降低光源的光波长λ。

瑞利判据

在业界,250nm工艺及其以前的光刻工艺中采用水银灯(波长365nm)作为光源。

为了提高光刻的分辨率,从180nm工艺开始采用波长为248nm的KrF(氟化氪)激光作为曝光光源;而从130nm到目前正在使用波长为193nm的ArF(氟化氩)激光作为曝光光源。

但是到了45nm工艺时,193nm的ArF激光也遇到了分辨率不够的问题。

同时受光刻其它配套设备的限制,取代ArF激光的新工艺还无法投入使用。

因此必须寻找新的降低最小分辨率的工艺。

于是工程师们开始考虑改善提高光刻系统中的折射率n,这就是沉浸式光刻的理论出发点。

新型的沉浸式光刻机,可以明显看到液体循环通道

在AMD的45nmPhenomII的生产中,整个晶圆是浸泡在去离子水(无杂质,无带电离子)中的,这种情况下n=1.44,相当于将光刻的分辨率提高了1.44倍,正好满足65/45=1.44的工艺改进幅度。

更好的消息是在实验室里,通过改进液体组成、光刻胶成分、镜头质量等等方法,沉浸式光刻已经能够实现22nm半导体工艺。

这也意味着在未来5年内,半导体制造业还将稳定地继续发展下去。

后45nm时代的新特点都有哪些?

现在,业界已经进入了45nm时代,而按照IntelTick-Tock的发展理论,今年Intel将对生产工艺进行改进,从45nm转入32nm。

那么在后45nm时代,芯片制造都有哪些新的特点呢?

难产的下一代光源——EUV

EUV的光刻机结构和原理

一直以来,Intel的工程师都在研发使用波长仅有13.5nm的EUV(ExtremeUltraViolet,极紫外光)作为光刻光源。

不过每次改变光源,还必须更换上和新光源相兼容的透镜系统、光刻胶等部分,相当于一次系统大换血。

而由于13.5nm的EUV相对目前的193nm激光跨度太大,相关的配套部件研发相当困难,所以被Intel寄予厚望的EUV技术的使用日程不得不从65nm跳票至32nm之后。

低温特性

从物理学课本上我们知道金属导体的电阻会随着温度的变化而变化。

大部分金属材料温度越低,电阻越小。

于是在很多超频比赛中,很多玩家都使用液氮(-170℃)来给芯片降温。

不过很多玩家发现在对英特尔第一代45nm处理器Core2ExtremeQX9650进行低温超频时,当温度低于-88℃时,部分CPU会自动断电造成超频失败。

这其中的原因极有可能是CPU在设计验证时没有考虑45nm的特殊低温特性(Intel方面没有给予官方证实)。

一般说来,在芯片制造前,会利用MOS管在不同工艺参数条件下的表现对芯片进行仿真,以求保证在MOS管速度最快和最慢情况下芯片都能够正常工作。

45nm工艺条件下,MOS管的延迟在温度降低到一定程度时又增加了。

如果在设计时没有考虑到这个特点,最终制造出来的芯片在极低温度下就可能出现工作异常。

业界洗牌

随着集成电路工艺更新到45nm,整个集成电路工业也开始新一轮洗牌。

以上提到的High-K、沉浸式光刻虽然从技术角度上成功地被投入使用,但应用这些新技术却要求更大的投资:

一台45nm沉浸式光刻机报价已超过6000万美元,而一条45nm生产线需要超过20台光刻机;符合45nm工艺生产的超净厂房和配套设备(超纯水、气体、排污净化等)需要投资超过5亿美元;Intel首个45nm厂房Fab32投资30亿美元,从其他工艺升级到45nm也需要投入20亿美元左右(据悉,EUV迟迟不能投入生产的最大原因就是极高的生产成本完全抵消了利润)。

在130nm工艺时代,全球有超过20家(阵营)公司能够进行芯片生产,但是由于之后越来越高的研发生产成本,使得目前跨入45nm半导体生产的仅有三大阵营:

财大气粗的Intel:

Intel每次都能在工艺升级上走在业界前列。

据报道,Intel将在2010年导入更先进的32nmWestmere架构处理器,将首次运用沉浸式光刻和第二代High-K金属栅工艺制造CPU部分,并同45nm的图形处理器封装在一块基板上。

IBM、特许半导体(新加坡)、AMD、Samsung、中芯国际阵营:

凭借IBM在半导体领域强大的研发实力和参与厂商的资金技术支持也能赶上摩尔定律的发展速度。

AMD将在2010年导入32nm和High-K金属栅工艺,并将首次使用自己制造CPU的工厂(位于德国的德累斯顿)代工GPU。

这将给未来的Raedon显卡带来多大的性能提升,全世界都拭目以待。

台积电和联电:

因为专注代工和众多的合作伙伴,也搭上了45nm的末班车。

不过技术能力较前两阵营稍显薄弱,其45nm既无SOI技术,也无High-K技术,因此无法兼顾高频和高性能。

目前代工双雄仅发布了45nm低功耗解决方案,高性能解决方案还需时日。

其它曾经如雷贯耳的半导体企业如今面对技术升级的巨额费用和金融危机,都或多或少地表现出举步维艰的困境:

剥离于德国英飞凌(Infineon)的奇梦达(Qimonda)已经申请破产;宝岛台湾的南亚(力晶)、茂德已经寻求政府救助,否则很难维持经营;富有“日本IBM”之称的富士通已经将半导体部门分拆出去,寻找合资方以谋出路……

未来,大者恒强是竞争残酷的集成电路市场永恒的定律。

65nm到45nm,从技术含量上来说,这次工艺升级是革命性的,因为应用了全新材料组成的新型晶体管(高-K金属栅极晶体管),而且我们会在32nm工艺上使用第二代高-K金属栅极晶体管。

赵军英特尔资深架构经理中国区产品市场部

至于为什么在45nm上没有应用SOI技术,Intel的技术人员也有多方面的考虑——SOI技术的成品率不容易控制,会增加硅晶圆的成本。

如果有更好的方案来达到更佳的效果,那么就没有必要使用SOI技术。

事实上,我们与IBM在半导体方面有很多合作,当然也有一定的竞争。

虽然我个人并不完全赞同作者的一些评论,但并不妨碍我对这篇文章的整体评价——这是一篇非常值得一读的介绍半导体最新工艺和技术的好文章,希望你读了之后也推荐给身边对半导体感兴趣的朋友们。

北京微电子国际研讨会再燃摩尔定律之争

出自:

SEMI作者:

彭晔

在全球半导体产业复苏之际,北京微电子国际研讨会于10月27日成功召开,摩尔定律这一引领半导体产业发展的“圣经”再次

成为了主题演讲会场争论的焦点。

摩尔定律减速之争

Intel中国研究院院长方之熙认为,摩尔定律还将延续,技术的发展不会止步。

目前Intel已开始15nm技术的研发,2011年将开

始10nm技术的研发。

追溯Intel的历史,每两年一代的新技术推出从未延迟,例如2005年的65nm技术,2007年的45nm技术

及2009年的32nm技术都为业界带来的全新的产品。

“摩尔定律不会减速,但设计与制造成本的增加的确是事实,因此如何将更多的功能整合在一起,减少小批量产品将是对企业的一大挑战。

”

Synopsys副总裁潘建岳认为,摩尔定律的延缓从45nm开始已很明显,在之前的90nm和65nm,自技术开发成熟后,大批量产品上市rampup通常需要2年的时间,但在45nm技术代,rampup速度已明显出现了滞后。

不过这对中国的半导体产业来说是件好事,因为我们追赶国际先进的脚步将因此而更快。

在摩尔定律的引导下,更多的科学家在探索新材料与新工艺。

SEMI中国区总裁陆郝安指出,为了提高半导体的性能,越来越多的元素已被成功应用于半导体工艺之中。

HKMG等新材料与新工艺的应用将使半导体技术不断发展自己,并超越自己。

摩尔定律的超越

Intel在追逐摩尔定律的同时,MoreThanMoore也是Intel中国研究院的重点研究课题之一。

方之熙介绍,CPU与存储器的3D封装将可能是未来的发展方向之一。

为解决CPU与Memory之间传送速度及管脚限制等问题,光互连传输已在Intel得到成功开发。

在Intel中国研究院10月中开幕仪式上,Intel就成功展示了第一套LightPeak高速光连线技术原型验证平台,实现在LightPeak上承载DisplayPort协议,传输带宽高达10Gbps。

SOC技术的发展也是业界关注的焦点之一。

“目前的SOC技术才刚刚开始,都还只是简单的集成,”方之熙说。

SOC未来在汽车电子等领域将有很大的发展空间。

当然IPcore的利用等问题也是需要仔细探讨的。

中国半导体产业的机会

半导体是新兴产业,也是高科技的代表行业之一。

每一次的危机都会给产业带来新的变化。

而此次中国在危机中率先复苏,

就充分证明了中国的实力。

中国半导体行业协会理事长江上舟认为,目前越来越多的IDM向FabLite转型,这对中国半导体制

造产业来说无疑是一个重大机遇。

中国的半导体制造、设计与设备行业都应该努力迈向世界先进水平。

陆郝安说,SEMI作为国际半导体行业协会,愿意搭建国际的沟通桥梁,中国业者只要坚定信心,就必定有更大的发展。

中国32nm技术脚步渐近

出自:

SEMI作者:

秦文芳

32nm离我们还有多远?

技术难点该如何突破?

材料与设备要扮演何种角色?

10月28日于北京举办的先进半导体技术研讨会即围绕“32nm技术发展与挑战”这一主题进行了探讨。

32nm节点挑战无限

“45nm已进入量产,32nm甚至更小的22nm所面临的挑战已摆在我们面前。

”中芯国际资深研发副总裁季明华博士在主题演讲时说,“总体来说,有四个方面值得我们注意。

首先是CMOS逻辑器件如何与存储器件更还的集成在一起;其次是SOC技术的巨大挑战,如低功耗问题等;第三是现在比较热门的3DIC和SIP集成;最后一个是如何建立更广泛的研发平台和联合机制,创造所谓的superfoundry。

”32nm技术面临巨大的研发成本和制造挑战,需要结合各方资源通力合作。

创造全兼容的CMOS技术平台、全兼容IP以及全球性全兼容芯片代工服务将是未来的发展趋势。

KLA-Tencor中国区技术总监任建宇博士认为,对于芯片制造来说,工艺控制至关重要。

45nm节点的测量步骤已超过200步,到了32nm或更小节点,工艺精度要求将会更为苛刻,测量步骤会更加繁琐。

现在能够预知的困难集中在高k金属栅部分的channel工艺控制、掩膜版缺陷的检测、硅片其它缺陷的及时识别判断等。

“小节点意味着图形更加细微,新的缺陷也会层出不穷,提高检测的灵敏度和分别率必不可少。

”任建宇博士坦言,“同时,制造业不同于单纯研发,对于生产效率有更高的要求,因此提高检测速度也是我们不可回避的问题。

”

光刻工艺如何齐头并进?

光刻技术历来是半导体技术发展路线图中的重头戏,对于它的讨论和研究不绝于耳。

ASML的中国区资深战略市场经理CurtisLiang博士就32nm节点光刻技术的进展进行了阐述。

“32nm对于存储器件的制造来说是一个新的转折点,因为很多新的技术将在这里被采用。

”CurtisLiang说,“在小节点引入浸入式光刻已毫无悬念,但是诸如光刻胶、浸入液等配套技术还有不小的进步空间。

现在大家也都在谈论双重图形,但是从长远角度来看,它应该是浸入式光刻与EUV光刻之间的一个过渡。

”

Cymer东南亚区光刻应用总监林思闽博士认为,32nm节点对于光刻工艺来说,意味着如何实现精确的栅极CD控制,线条边缘粗糙度以及OPC等也将困难重重。

光源是光刻机上最重要的组成部分之一,光源的能量、稳定性、寿命等在某种程度上影响着光刻技术的发展。

特别是未来有可能会采用的EUV光刻,光源的质量更是举足轻重的。

32nm节点目前来看还是以浸入式光刻配合双重图形技术为主,再往下发展,EUV的机会将会很大。

半导体材料不容忽视

当越来越多的新材料被引入半导体制造时,对于它的作用愈发引起人们的兴趣。

Cabot的亚洲研发总监吴国俊博士对32nm节点的CMP材料提出了自己的看法。

“CMP工艺与其它工艺有很大的不同,那就是它会更多的依赖于材料,如研磨料和研磨垫,。

换句话说,材料的发展引领者CMP技术的进步。

”吴国俊博士说,“我们现在常常提到的很多新结构,如高k金属栅和低k互连等都引入了很多新兴材料,CMP不仅要求迅速的实现抛光的目的,还要保证尽可能少的残留和缺陷。

目前的研发重点是对于不同材料实现良好的选择比,减少划伤等缺陷问题。

安集微电子的