模数转换器ADC0809应用原理.docx

《模数转换器ADC0809应用原理.docx》由会员分享,可在线阅读,更多相关《模数转换器ADC0809应用原理.docx(14页珍藏版)》请在冰豆网上搜索。

模数转换器ADC0809应用原理

AD0809应用原理--很全面的资料

1. 0809的芯片说明:

ADC0809是带有8位A/D转换器、8路多路开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,可以和单片机直接接口。

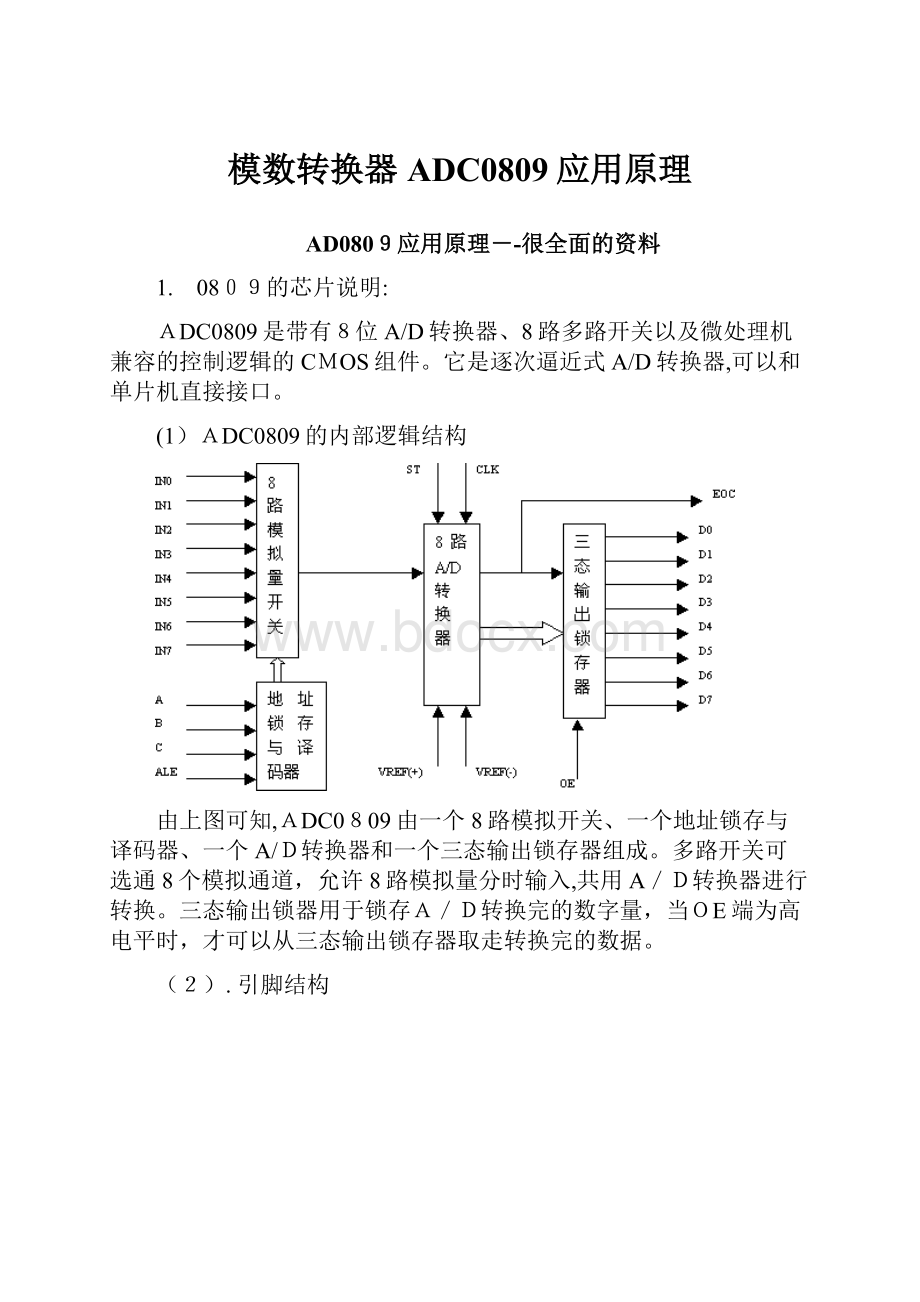

(1)ADC0809的内部逻辑结构

由上图可知,ADC0809由一个8路模拟开关、一个地址锁存与译码器、一个A/D转换器和一个三态输出锁存器组成。

多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用A/D转换器进行转换。

三态输出锁器用于锁存A/D转换完的数字量,当OE端为高电平时,才可以从三态输出锁存器取走转换完的数据。

(2).引脚结构

IN0-IN7:

8条模拟量输入通道

ADC0809对输入模拟量要求:

信号单极性,电压范围是0-5V,若信号太小,必须进行放大;输入的模拟量在转换过程中应该保持不变,如若模拟量变化太快,则需在输入前增加采样保持电路。

地址输入和控制线:

4条

ALE为地址锁存允许输入线,高电平有效。

当ALE线为高电平时,地址锁存与译码器将A,B,C三条地址线的地址信号进行锁存,经译码后被选中的通道的模拟量进转换器进行转换。

A,B和C为地址输入线,用于选通IN0-IN7上的一路模拟量输入。

通道选择表如下表所示。

C

B

A

选择的通道

0

0

0

IN0

0

0

1

IN1

0

1

0

IN2

0

1

1

IN3

1

0

0

IN4

1

0

1

IN5

1

1

0

IN6

1

1

1

IN7

数字量输出及控制线:

11条

ST为转换启动信号。

当ST上跳沿时,所有内部寄存器清零;下跳沿时,开始进行A/D转换;在转换期间,ST应保持低电平。

EOC为转换结束信号。

当EOC为高电平时,表明转换结束;否则,表明正在进行A/D转换。

OE为输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。

OE=1,输出转换得到的数据;OE=0,输出数据线呈高阻状态。

D7-D0为数字量输出线。

CLK为时钟输入信号线。

因ADC0809的内部没有时钟电路,所需时钟信号必须由外界提供,通常使用频率为500KHZ,

VREF(+),VREF(-)为参考电压输入。

2. ADC0809应用说明

(1).ADC0809内部带有输出锁存器,可以与AT89S51单片机直接相连。

(2). 初始化时,使ST和OE信号全为低电平。

(3).送要转换的哪一通道的地址到A,B,C端口上。

(4). 在ST端给出一个至少有100ns宽的正脉冲信号。

(5). 是否转换完毕,我们根据EOC信号来判断。

(6). 当EOC变为高电平时,这时给OE为高电平,转换的数据就输出给单片机了。

3. 实验任务

如下图所示,从ADC0809的通道IN3输入0-5V之间的模拟量,通过ADC0809转换成数字量在数码管上以十进制形成显示出来。

ADC0809的VREF接+5V电压。

4.电路原理图

5.程序设计:

(1).进行A/D转换时,采用查询EOC的标志信号来检测A/D转换是否完毕,若完毕则把数据通过P0端口读入,经过数据处理之后在数码管上显示。

(2).进行A/D转换之前,要启动转换的方法:

ABC=110选择第三通道

ST=0,ST=1,ST=0产生启动转换的正脉冲信号.

(3).关于0809的计算:

ad0809是根据逐位逼近的方法产生数据的。

。

参考电压为0-5V的话。

以0809八位255的转换精度每一位的电压值为(5-0)/255≈0.0196Vﻫ设输入电压为X则:

X-27*0.0196>=0则AD7=1否则AD7=0。

X-26*0.0196>=0则AD6=1否则AD6=0。

ﻫX-20*0.0196>=0则AD0=1否则AD0=0。

ﻫ(27指2的7次方。

26-------20同理)

若参考电压为0-1V

(1-0)/255≈0.0039V精度自然高了。

。

可测量范围小了。

1)汇编源程序:

CHEQU30H

DPCNTEQU31H

DPBUFEQU 33HﻫGDATA EQU32HﻫSTBITP3.0ﻫOEBITP3.1

EOCBITP3.2

ORG00H

LJMPSTART

ORG 0BHﻫLJMPT0X

ORG30HﻫSTART:

MOVCH,#0BCH

MOVDPCNT,#00H

MOVR1,#DPCNT

MOVR7,#5

MOVA,#10

MOV R0,#DPBUFﻫLOP:

MOV@R0,A

INC R0

DJNZR7,LOPﻫMOV@R0,#00H

INCR0ﻫMOV@R0,#00H

INCR0ﻫMOV@R0,#00HﻫMOVTMOD,#01HﻫMOVTH0,#(65536-4000)/256ﻫMOVTL0,#(65536-4000)MOD256

SETBTR0ﻫSETBET0ﻫSETBEA

WT:

CLRST

SETBSTﻫCLRST

WAIT:

JNBEOC,WAITﻫSETBOE

MOV GDATA,P0ﻫCLROEﻫMOV A,GDATA

MOV B,#100

DIVAB

MOV33H,A

MOV A,BﻫMOVB,#10

DIVAB

MOV 34H,A

MOV35H,BﻫSJMP WTﻫT0X:

NOPﻫMOV TH0,#(65536-4000)/256

MOV TL0,#(65536-4000) MOD 256ﻫMOVDPTR,#DPCD

MOV A,DPCNT

ADD A,#DPBUFﻫMOVR0,A

MOVA,@R0ﻫMOVCA,@A+DPTRﻫMOVP1,AﻫMOVDPTR,#DPBT

MOVA,DPCNTﻫMOVCA,@A+DPTRﻫMOV P2,A

INCDPCNT

MOVA,DPCNT

CJNEA,#8,NEXT

MOVDPCNT,#00H

NEXT:

RETI

DPCD:

DB3FH,06H,5BH,4FH,66HﻫDB6DH,7DH,07H,7FH,6FH,00HﻫDPBT:

DB 0FEH,0FDH,0FBH,0F7H

DB0EFH,0DFH,0BFH,07FHﻫEND

2)C语言源程序

#include

unsignedchar code dispbitcode[]={0xfe,0xfd,0xfb,0xf7,

0xef,0xdf,0xbf,0x7f};

unsignedcharcode dispcode[]={0x3f,0x06,0x5b,0x4f,0x66,

0x6d,0x7d,0x07,0x7f,0x6f,0x00};

unsignedchardispbuf[8]={10,10,10,10,10,0,0,0};

unsignedchardispcount;

sbit ST="P3"^0;ﻫsbit OE="P3"^1;

sbitEOC="P3"^2;

unsignedcharchannel="0xbc";//IN3ﻫunsigned chargetdata;

void main(void)ﻫ{ﻫTMOD=0x01;ﻫTH0=(65536-4000)/256;

TL0=(65536-4000)%256;ﻫTR0=1;

ET0=1;

EA=1;

P3=channel;

while

(1)

{ﻫST=0;

ST=1;ﻫST=0;ﻫwhile(EOC==0);ﻫOE=1;

getdata=P0;

OE=0;

dispbuf[2]=getdata/100;

getdata=getdata%10;ﻫdispbuf[1]=getdata/10;

dispbuf[0]=getdata%10;ﻫ}

}

voidt0(void)interrupt 1using0ﻫ{

TH0=(65536-4000)/256;

TL0=(65536-4000)%256;

P1=dispcode[dispbuf[dispcount]];

P2=dispbitcode[dispcount];

dispcount++;ﻫif(dispcount==8)

{

dispcount=0;

}

}

3)FPGA实现的程序:

(verilog)

moduleAD0809(clk, //脉宽(至少100ns)

ﻩﻩ rst_n,

ﻩﻩ EOC, //约100us后EOC变为高电平转换结束

START,//启动信号,上升沿有效(至少100ns)

ﻩ OE,//高电平打开三态缓冲器输出转换数据

ﻩﻩ ALE,//高电平有效,选择信道口

ﻩ ADDA,//因为ADDB,ADDC都接地了,这里只有ADDA为变量

ﻩﻩDATA,////转换数据

ﻩDATA_R);

outputSTART,OE,ALE,ADDA;

inputEOC,clk,rst_n;

input[7:

0]ﻩDATA;

output[7:

0]DATA_R;

regﻩSTART,OE,ALE,ADDA;

reg[7:

0]ﻩDATA_R;

reg[4:

0]CS,NS;

parameterIDLE=5''b00001,START_H=5''b00010,START_L=5''b00100,

ﻩCHECK_END=5''b01000,GET_DATA=5''b10000;

alwaysﻩ@(*)

case(CS)

IDLE:

ﻩNS=START_H;

START_H:

ﻩ

ﻩNS=START_L;

START_L:

NS=CHECK_END;

CHECK_END:

if(EOC)

NS=GET_DATA;

else

ﻩNS=CHECK_END;

GET_DATA:

NS=IDLE;ﻩ

default:

ﻩNS=IDLE;

endcaseﻩ

alwaysﻩ@(posedgeclk)

if(!

rst_n)

CS<=IDLE;

elseﻩ

CS<=NS;

always@(posedgeclk)

case(NS)

IDLE:

ﻩbegin

ﻩOE<=0;

ﻩSTART<=0;

ﻩALE<=0;ADDA<=1;

end

START_H:

ﻩ

begin

ﻩOE<=0;

ﻩSTART<=1; //产生启动信号

ﻩALE<=1;ADDA<=1;//选择信道口IN0

end

START_L:

ﻩbegin

ﻩOE<=0;

ﻩSTART<=0;

ﻩALE<=1;//启动信号脉宽要足够长,在启动的时候ALE要一直有效

end

CHECK_END:

ﻩbegin

ﻩOE<=0;

ﻩSTART<=0;

ﻩALE<=0;

ﻩend

GET_DATA:

ﻩbegin

OE<=1;ﻩ//高电平打开三态缓冲器输出转换数据

DATA_R<=DATA;//提取转换数据

ﻩSTART<=0;

ﻩALE<=0;

ﻩend

default:

begin

ﻩOE<=0;

START<=0;

ﻩALE<=0;ADDA<=0;

end

endcaseﻩ

endmodule

4)FPGA实现的程序:

(VHDL)

LIBRARY IEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;ﻫENTITY AD0809IS

PORT(D:

INSTD_LOGIC_VECTOR(7DOWNTO0); CLK,EOC:

INSTD_LOGIC;

CLOCK:

IN STD_LOGIC;

ALE,START,OE,LOCK0:

OUTSTD_LOGIC;

DOUT:

OUTSTD_LOGIC_VECTOR(6 DOWNTO0);

SEL:

OUT STD_LOGIC_VECTOR(2DOWNTO0));

ENDAD0809;

ARCHITECTUREbehav OF AD0809ISﻫTYPEstatesIS(st0,st1,st2,st3,st4);

SIGNALcurrent_state,next_state:

states:

=st0;

SIGNALREGL:

STD_LOGIC_VECTOR(7DOWNTO0);

SIGNALLOCK:

STD_LOGIC;

SIGNALCNT1:

STD_LOGIC_VECTOR(0 DOWNTO0);ﻫSIGNAL A:

INTEGER RANGE0TO 1;

SIGNALLOWDATA:

STD_LOGIC_VECTOR(3 DOWNTO0);ﻫSIGNAL HIGHDATA:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNAL LOWLED7S:

STD_LOGIC_VECTOR(6DOWNTO0);ﻫSIGNALHIGHLED7S:

STD_LOGIC_VECTOR(6DOWNTO0);ﻫBEGIN

LOCK0<=LOCK;

ﻫPROCESS(REGL)ﻫ BEGIN ﻫ LOWDATA<=REGL(3DOWNTO 0);

HIGHDATA<=REGL(7DOWNTO4);ﻫ CASELOWDATAISﻫ WHEN"0000"=>LOWLED7S<="0111111";

WHEN"0001"=>LOWLED7S<="0000110";

WHEN"0010"=>LOWLED7S<="1011011";

WHEN"0011"=>LOWLED7S<="1001111";ﻫ WHEN"0100"=>LOWLED7S<="1100110";

WHEN"0101"=>LOWLED7S<="1101101";

WHEN"0110" =>LOWLED7S<="1111101";

WHEN"0111"=> LOWLED7S<="0000111";

WHEN"1000"=>LOWLED7S<="1111111";ﻫ WHEN"1001"=>LOWLED7S<="1101111";ﻫ WHEN "1010" =>LOWLED7S<="1110111";ﻫ WHEN"1011"=> LOWLED7S<="1111100";ﻫ WHEN"1100"=>LOWLED7S<="0111001";ﻫ WHEN"1101"=> LOWLED7S<="1011110";

WHEN"1110" =>LOWLED7S<="1111001";

WHEN"1111"=> LOWLED7S<="1110001";ﻫ WHENOTHERS=>Null;ﻫ END CASE;

CASEHIGHDATA IS

WHEN "0000"=> HIGHLED7S<="0111111";ﻫ WHEN"0001" => HIGHLED7S<="0000110";

WHEN "0010"=>HIGHLED7S<="1011011";

WHEN "0011"=>HIGHLED7S<="1001111";ﻫ WHEN"0100"=> HIGHLED7S<="1100110";ﻫ WHEN"0101"=>HIGHLED7S<="1101101";

WHEN"0110"=>HIGHLED7S<="1111101";

WHEN"0111"=>HIGHLED7S<="0000111";

WHEN "1000"=>HIGHLED7S<="1111111";ﻫ WHEN"1001"=>HIGHLED7S<="1101111";ﻫ WHEN "1010"=> HIGHLED7S<="1110111";

WHEN "1011" =>HIGHLED7S<="1111100";

WHEN"1100"=>HIGHLED7S<="0111001";

WHEN"1101"=>HIGHLED7S<="1011110";

WHEN"1110" =>HIGHLED7S<="1111001";

WHEN"1111"=> HIGHLED7S<="1110001";

WHENOTHERS=>Null;

ENDCASE;ﻫEND PROCESS;

PROCESS(CLOCK)ﻫ BEGINﻫ IFCLOCK'EVENTANDCLOCK='1' THENCNT1<=CNT1+1;ﻫ END IF;ﻫEND PROCESS;

PROCESS(CNT1)

BEGINﻫ CASECNT1ISﻫ WHEN"0"=>SEL<="111"; A<=0;ﻫ WHEN"1"=>SEL<="110"; A<=1;

WHENOTHERS=>NULL;ﻫ ENDCASE;ﻫENDPROCESS;

PROCESS(A)

BEGIN

CASEA IS

WHEN0=>DOUT<=LOWLED7S;

WHEN1=>DOUT<=HIGHLED7S;ﻫ WHENOTHERS=>NULL;

END CASE;ﻫENDPROCESS;ﻫ

COM:

PROCESS(current_state,EOC) ﻫ BEGIN

CASE current_stateIS

WHENst0=>ALE<='0';START<='0';LOCK<='1';OE<='0';next_state<=st1;

WHENst1=>ALE<='1';START<='0';LOCK<='1';OE<='0';next_state<=st2; ﻫ WHENst2=>ALE<='0';START<='1';LOCK<='0';OE<='0';

IF (EOC='1')THENnext_state<=st3;

ELSEnext_state<=st2; ﻫ END IF;

WHENst3=>ALE<='0';START<='0';LOCK<='0';OE<='1';next_state<=st4;

WHENst4=>ALE<='0';START<='0';LOCK<='1';OE<='1';next_state<=st0; ﻫ WHEN OTHERS=>next_state<=st0;ﻫ ENDCASE;ﻫENDPROCESS COM;

REG:

PROCESS(CLK)

BEGIN

IF(CLK'EVENTANDCLK='1')THENcurrent_state<=next_state;

ENDIF;ﻫENDPROCESSREG;

LATCH1:

PROCESS(LOCK) ﻫ BEGINﻫ IFLOCK='1'AND LOCK'EVENTTHENREGL<=D;ﻫ END IF;

END PROCESSLATCH1;

ENDbehav;