FIR滤波器设计剖析.docx

《FIR滤波器设计剖析.docx》由会员分享,可在线阅读,更多相关《FIR滤波器设计剖析.docx(18页珍藏版)》请在冰豆网上搜索。

FIR滤波器设计剖析

4 FIR数字滤波器的设计与实现

4.1 FIR数字滤波器在Simulink环境下的仿真

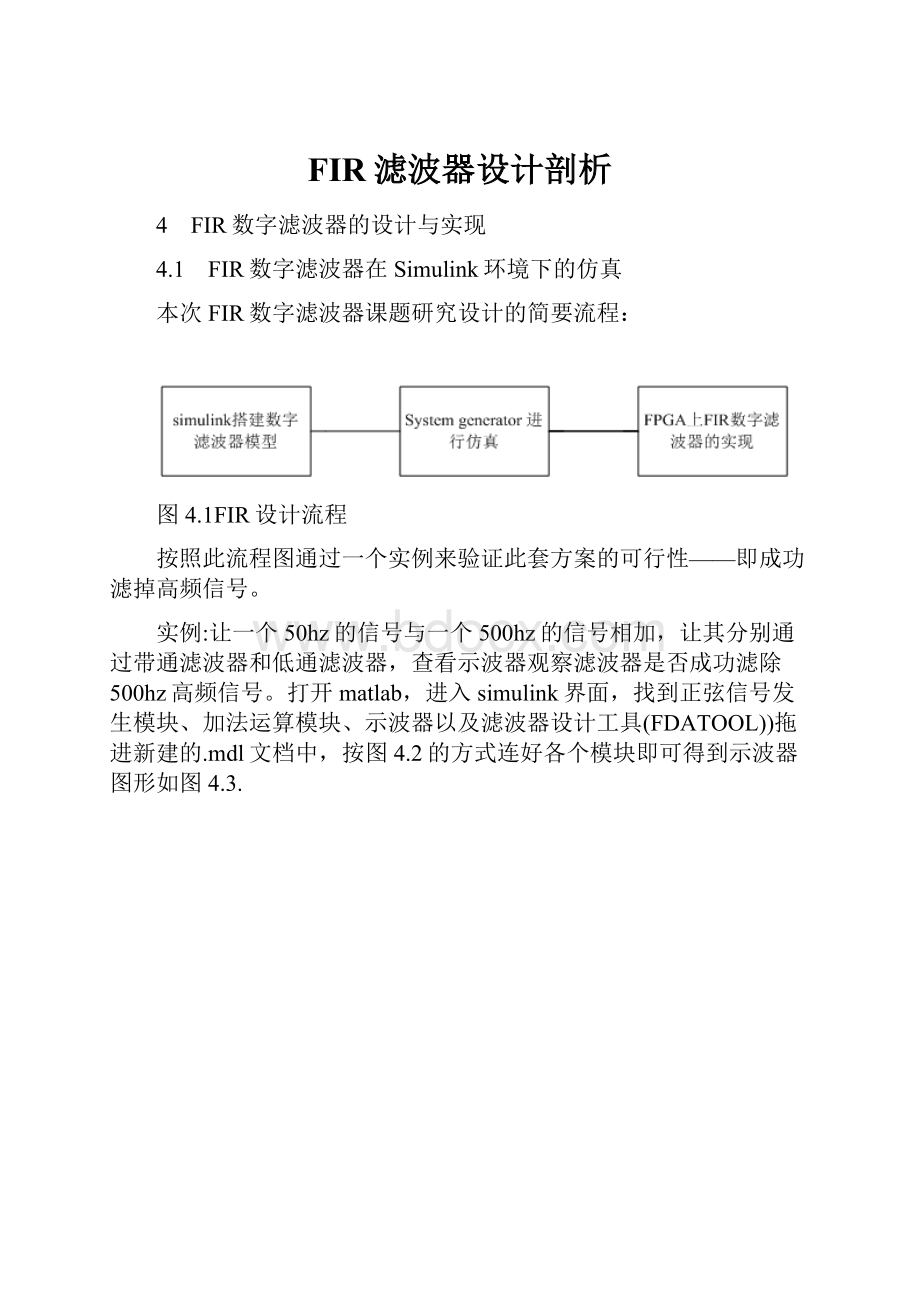

本次FIR数字滤波器课题研究设计的简要流程:

图4.1FIR设计流程

按照此流程图通过一个实例来验证此套方案的可行性——即成功滤掉高频信号。

实例:

让一个50hz的信号与一个500hz的信号相加,让其分别通过带通滤波器和低通滤波器,查看示波器观察滤波器是否成功滤除500hz高频信号。

打开matlab,进入simulink界面,找到正弦信号发生模块、加法运算模块、示波器以及滤波器设计工具(FDATOOL))拖进新建的.mdl文档中,按图4.2的方式连好各个模块即可得到示波器图形如图4.3.

图4.2simulink搭建的滤波器

图4.3simulink仿真波形

图4.3由上到下依次是50hz正弦波、500hz正弦波、两个正弦波的和信号经过带通滤波器以及两个正弦波的和信号经过低通滤波器后的信号。

此图说明我们搭建的Simulink模型是正确的,而且可以明显看出低通滤波器成功滤掉了高频信号。

4.2 FIR数字滤波器在Systemgenerator环境下的仿真

上一小节论述了在Simulink环境下的数字滤波器模型搭建并完成仿真验证,接下来要做的就是用SystemGenerator搭建硬件执行程序实现仿真并验证。

以下简单介绍所需要的模块以及参数设置。

(1)SystemGenerator模块

SystemGenerator模块的参数设置里允许用户选择FPGA的硬件目标、系统时钟周期等选项。

Simulink和FPGA系统仿真时间可以由SystemGenerator的时钟设置来设置,滤波器模型中有很多小的模型例如信号发生模块、AD/DA模块等,Simulink的采样周期是这些小模块采样周期的最大公因子,这点可由SystemGenerator来设定。

而硬件中隐含的采样时间实际上比Simulink中可看到的仿真采样时间要快。

基于此我们将FPGA时钟信号设定为10ns,Simulink采样周期设定为1s。

(2)信号发生模块

信号发生有很多方式,这里采用ROM产生一个500hz的正弦信号,DDS来产生一个50hz的信号。

下图分别为其时序电路设计:

图4.4信号发生模块

(3)输入输出模块。

图4.5输入模块

把Simulink的浮点数转换成定点数,送给Systemgenerator的FPGA设计,功能相当于信号系统中的ADC定义顶层设计中的输入端口,对应HDL设计中的inputports。

图4.6输出模块

把Systemgenerator的FPGA设计的定点数转换成浮点数送给Simulink,功能相当于信号系统中的DAC;定义顶层设计中的输出端口,对应HDL设计中的output。

(4)滤波器模型

图4.7FDATOOL图标

MATLAB的信号处理工具箱研发出一种编辑者自己设置滤波器参数,系统根据所设定的参数自动生成滤波器的工具即FDATOOL。

FDA是FilterDesignandAnalysis的首字母缩写词,它的中文名称应为滤波器设计与分析工具。

FDA工具根据用户指定的滤波器频域响应要求自动设计滤波器阶数和权重系数,操作也很简便,可以用来快速设计与分析滤波器如幅度和相位响应和零极点图等。

在Simulink库中找到该模块拖拽进模型设计中。

双击进入该参数设置界面。

以低通滤波器参数设计为例,各参数设置如下图所示:

图4.8FDATOOL选项卡

1.CurrentFilterInformation(当前滤波器信息)

图4.9当前滤波器信息

Structure(结构):

表明当前的滤波器结构是离散时间滤波器结构

Order(阶数):

显示当前滤波器的阶数为124阶

Stable(部分):

表明这个滤波器是渐近稳定(是的)或不稳定(不是),极点在在单位圆上或圆外滤波器被认为是不稳定的。

此时的滤波器设计是稳定地。

Source(资源):

表明当前滤波器是用FDATool设计的(设计)或从另一个资源导进的(导进)。

Storefilter(储存滤波器):

按钮储存当前滤波器的设计到滤波器的管理。

FilterManager(滤波器管理):

按钮打开滤波器管理对话框。

2.ResponseType(响应类型)

图4.10相应类型栏

3.FilterOrder(滤波器的阶数)

图4.11滤波器结束栏

指定阶数的滤波器(Specifyorder:

指定阶数),最小阶滤波器(MinimumOrder:

最低阶数)。

在满足规范要求下,被计算的滤波器拥有最小阶数。

在SpecifyOrder中填入所要设计的滤波器的阶数(n阶滤波器,SpecifyOrder=n-1),如果选择MinimumOrder则Matlab根据所设定滤波器类型自动采用所设置的最小值。

4.DesignMethod(设计方式)

图4.12滤波器设计方式栏

选择FIR滤波器并采用等波纹设计法。

5.FrequencySpecifications(频率说明)

图4.13频率采样栏

在文本框中指定以下频率单位全部设置为Hz:

Fs——采样频率为6250Hz

Fpass(或Wpass)——通带截止频率为50Hz

Fstop(或Wstop)——阻带截止频率为150Hz

FrenquencySpecifications选项,可以设置频带的各参数,包括采样频率fs和频带的截止频率。

它的具体选项由所设计滤波器类型和设计方法决定。

例如选择窗函数来设计数字滤波器时,不需要设置阻带参数但必须设置通带截止频率。

6.MagnitudeSpecifications(幅度规格)

图4.14幅度调整栏

MagnitudeSpecifications选项,用来设置幅值衰减。

图4-14显示通带截止频率处衰减1db,阻带截止频率范围内衰减60db。

至此,一个针对此系统的低通滤波器就生成了。

为了使生成的能够导入设计中,需要将其滤波器的系数值先通过一个向量导入MATLAB的Workspace中以便调用。

此时点击FDATOOL菜单栏下的File,找到Export选项并单击打开,出现以下界面:

图4.15导出数据选项卡

通过Export对话框的参数设置即可将所设计的滤波器的系数导入到Workspace中,可以通过打开Matlab中的Workspace窗口来确认是否成功导入。

如图4.16系数B即为Workspace中低通滤波器系数参数。

图4.17为其具体数值,由于滤波器阶数124阶所以系数为124+1,+1是因为系统函数中有个常数项,图4.17只截取前13个系数。

图4.16workspace滤波器参数

图4.17滤波器系数具体数值

带通滤波器设置参数导出系数方式和前面所讲的低通滤波器设计方式相同,具体数值见表4.1.

模块名称

设置选项

Responsetype(滤波器类型)

Bandpass(低通)

Designmethod(设计方法)

FIREquiripple(FIR等波纹设计法)

Fiterorder(滤波器阶数)

Minimumorder

Options(选项卡)

20

Frequencyspecifications

(频率参数设置)

Units-Hz;Fs-6250;Fpass-50;Fstop1-200;Fpass1-300;

Fpass2-700;Fstop2-800

Magnitudespecifications(衰减度)

Units-db;Apass-1;Astop1-60;Astop2-60

表4.1带通滤波器参数设置

其中Fstop1-下阻带截止频率、Fpass1-通带下限截止频率、Fpass2-通带上限截止频率、Fstop2-上阻带截止频率,而设计低通滤波器只需要定义下阻带截止频率、通带下限截止频率。

设置好滤波器参数下来面临的问题就是怎样才能将上面的系数应用到设计当中。

XilinxBlockset目录中提供了与FDATOOL工具的接口——FIRCompiler.设计时只需将FDATool模块和FIRCompiler5.0模块拉入设计电路图,其中FDATOOL模块单独放置不用连接其他模块,相当于提供系数导入口,而FIRCompiler5.0模块可以直接用来连接电路功能上等价于一个实际的滤波器。

此时由FDATOOL设计的FIR滤波器系数可以直接传给FIRCompiler5.0模块作为有具体系数的FIR滤波器。

这种做法省去了手工设计滤波器冗长而又机械的过程。

SystemGenerator库中的FIRCompiler5.0,如下图:

图4.18FIRcompiler图标

双击打开该模块进行属性设定。

在FilterSpecification选项卡中的系数向量一栏中会自动生成刚刚用FDATOOL导出的滤波器系数,它是接受滤波器系数的模块,当然也可以手动将Workspace中生成的系数填写入CoefficientVector(系数向量的系数向量指定为一个单一的MATLAB行向量。

抽头数是从MATLAB行向量的长度推断。

前面已经通过使用FDATOOL工具可以输入这些数据。

HardwareOversamplingRate:

硬件采样率,过采样率决定并行度的硬件。

硬件过采样格式为硬件过采样率,其值可根据自身要求设定,在此设定为250。

其余都保持默认即可,低通滤波器规格选项卡具体设置如下图:

图4.19规格选项卡

实现选项卡的具体参数如下:

FilterArchitectura(滤波器结构)选择Systolic_Multiply_Accumulate(基于乘法器/XtremeDSP片级联的MAC架构)。

其余参数如图:

图4.20实现选项卡

DetailedImplementation详细的实施标签具体参数设置如下:

图4.21详细设置选项卡

同样带通滤波器FIRCompiler5.0参数具体设置如下表:

选项卡名称

设置选项

Coefficientvector(系数矢量)

C

HardwareOversamplingRate

(过采样率)

250

Filterarchitecture(滤波器结构)

Systolic_multiply_accumulate

Coefficientstructure(系数结构)

Non_symmetric

Coefficientwidth(系数宽度)

16

表4.2带通滤波器FIRCompiler5.0参数具体设置

其余参数保持默认,这样带通滤波器也就设置完成了。

设置好FDATOOL和FIRCompilier5.0,就可以用SystemGenerator搭建仿真电路。

我们在SimulinkLibraryBrowser中浏览XilinxBlockset,选择BasicElements选项。

在元件窗口将所需要的模块图标拖拽到模型编辑器中。

从Simulink目录下的Sources栏找到Constant单元,从同一目录下的Sinks栏目找到Scope单元,均放入电路编辑器。

按下图方式连接电路:

图4.22SystemGenerator搭建仿真电路

示波器仿真出的波形:

图4.23SystemGenerator仿真波形

图4.23由上到下依次显示50hz正弦波、500hz正弦波、两个正弦波的和信号经过带通滤波器以及两个正弦波的和信号经过低通滤波器后的信号。

由图可以发现用SystemGenerator仿真出来的结果和Similink结果基本一致,不仅说明了滤波器实现了滤波功能也为后期在硬件平台上的验证提供可能。

4.3 FIR数字滤波器在FPGA上的实现

在前面4.2小节中,实现了在SystemGenerator环境下对该滤波器的仿真,这也说明此套方案是可以在FPGA上实现。

考虑到Simulink和FPGA输出数据类型有所区别,所以必须在原有SystemGenerator的滤波器模型图的基础上添加DA模块。

本次毕设采用了四路DA,下图为其时序电路:

图4.24DA时序电路

将DA模块添加到编辑栏中,调整输入输出数据类型即可得到如下数字滤波器的FPGA仿真电路

图4.24SystemGenerator完整电路

成功编译后通过双击SystemGenerator图标,单击Compilation选择生成Bitstream,点击Generate就可以自动生成比特流文件。

XINLIX公司提供的Adept软件可以将生成的比特流文件下载到FPGA中,按图4.25连接硬件电路,如下图所示:

图4.25FPGA硬件连接电路

下图为示波器仿真图形:

图4.26示波器输出波形

图4.26由上到下依次显示50hz正弦波、500hz正弦波、两个正弦波的和信号经过带通滤波器后的信号、两个正弦波的和信号经过低通滤波器后的信号。

通过比较Simulink、SystemGenerator和FPGA三个仿真图可以得出,此套设计流程是可行的,可以在FPGA上实现了一个FIR数字滤波器的设计。

4.4 如何优化数字滤波器性能

在设计滤波器采用FDATOOL工具时最大一个优点就是当设定好滤波器参数,例如:

通带截止频率、阻带截止频率、通带最大衰减系数、阻带最小衰减系数,设定好参数,点击DesignFilter系统会自动计算出合适的滤波器阶数,这也说明,一个滤波器阶数主要由这几个参数来决定。

理论上讲阶数N越大,这些参数波动范围就会变小也就是更精确,这样得出的滤波器滤波效果也很会很好。

但是事实上,在设计一个数字滤波器时,我们不仅要考虑其软件设计结构还要考虑硬件实现成本,阶数N越大,实际电路就越复杂,耗费的资源也就越多,遇到此类情况,就需要大量实验证明是否阶数越大效果越好以及如何在成本与高性能之间做出合理抉择。

研究人员在一系列实验总结之后得出,并不是N越大,滤波器性能就越好,它有个临界点超过这个临界点,滤波效果就不会随着阶数的增大而提升,相反过度的增加阶数有可能带来码间串扰,即使得窄的脉冲变宽,是信号出现严重失真。

综上所述,阶数高不一定滤波效果就好,只有通过准确计算不断调试得到合适的阶数才能达到最好的滤波效果。