集成电路课设全加器.docx

《集成电路课设全加器.docx》由会员分享,可在线阅读,更多相关《集成电路课设全加器.docx(17页珍藏版)》请在冰豆网上搜索。

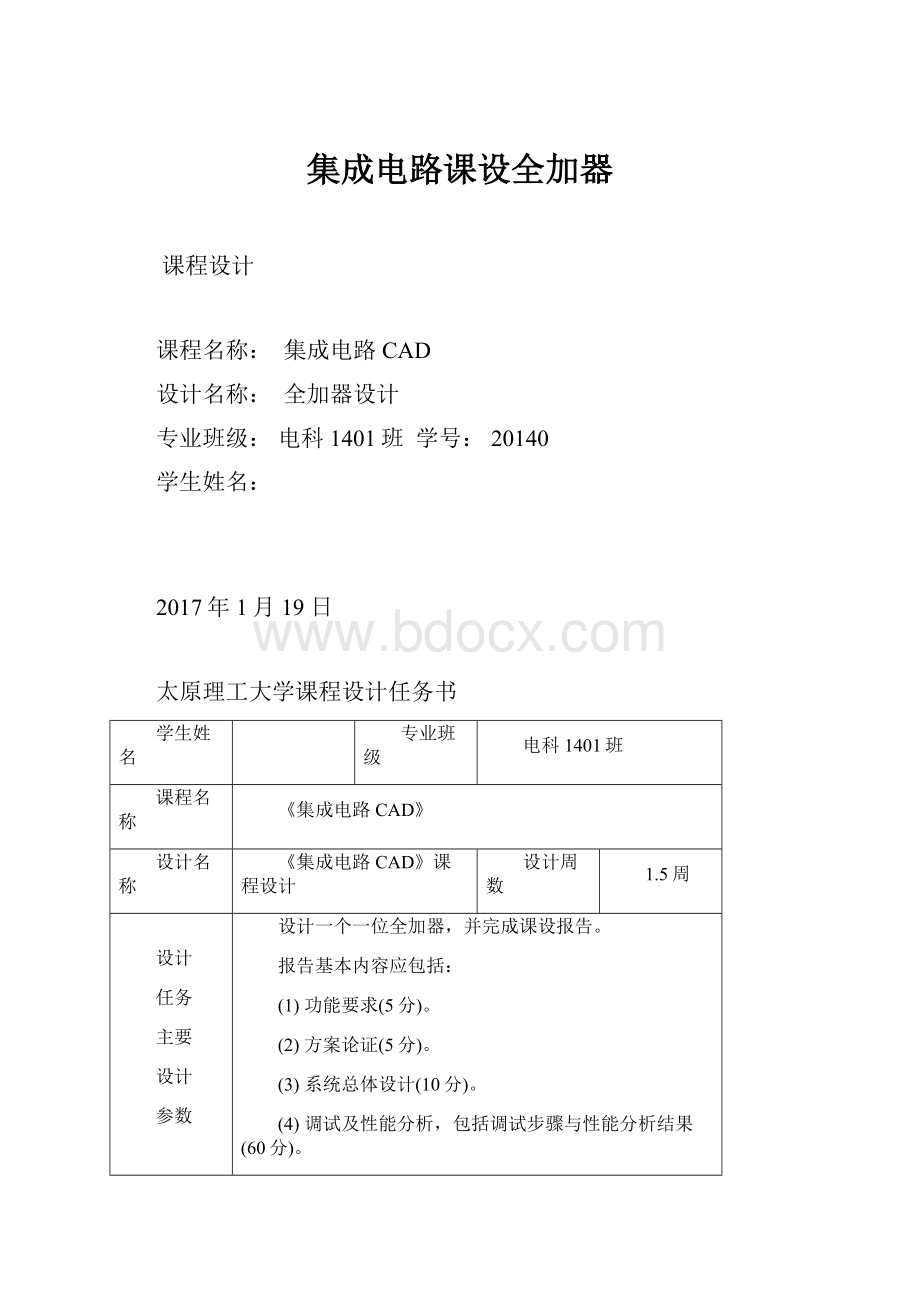

集成电路课设全加器

课程设计

课程名称:

集成电路CAD

设计名称:

全加器设计

专业班级:

电科1401班学号:

20140

学生姓名:

2017年1月19日

太原理工大学课程设计任务书

学生姓名

专业班级

电科1401班

课程名称

《集成电路CAD》

设计名称

《集成电路CAD》课程设计

设计周数

1.5周

设计

任务

主要

设计

参数

设计一个一位全加器,并完成课设报告。

报告基本内容应包括:

(1)功能要求(5分)。

(2)方案论证(5分)。

(3)系统总体设计(10分)。

(4)调试及性能分析,包括调试步骤与性能分析结果(60分)。

(5)源程序清单(15分)。

(6)设计小结(5分)。

设计内容

设计要求

需要完成电路编辑、性能仿真、版图绘制、LVS校验四部分的内容

主要参考

资料

《集成电路CAD与实践》

学生提交

归档文件

《CAD集成电路课程设计报告》

注:

1.课程设计完成后,学生提交的归档文件应按照:

封面—任务书—说明书—图纸的顺序进行装订上交(大张图纸不必装订)。

2.可根据实际内容需要续表,但应保持原格式不变。

一、绪论

1.1设计背景

Tanner集成电路设计软件是由TannerResearch公司开发的基于Windows平台的用于集成电路设计的工具软件。

早期的集成电路版图编辑器L-Edit在国内已具有很高的知名度。

TannerEDATools也是在L-Edit的基础上建立起来的。

整个设计工具总体上可以归纳为电路设计级和版图设计级两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

Tanner软件包括S-Edit,T-Spice,L-Edit与LVS。

L-EditPro是TannerEDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-EditPro包含IC设计编辑器(LayoutEditor)、自动布线系统(StandardCellPlace&Route)、线上设计规则检查器(DRC)、组件特性提取器(DeviceExtractor)、设计布局与电路netlist的比较器(LVS)、CMOSLibrary、MarcoLibrary,这些模块组成了一个完整的IC设计与验证解决方案。

L-EditPro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

1.2课设基本任务:

全加器设计

(1)依据全加器的真值表,给出全加器的电路图完成全加器由电路图到晶体管级的转化(需提出至少2种方案);

(2)用tanner软件中的版图编辑器L-Edit进行一位全加器电路的版图绘制,并进行DRC验证;

(3)完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间;

(4)遵循设计规则完成全加器晶体管级电路图的版图,流程如下:

版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图;

(5)用tanner软件的layout-Edit中的lvs功能对一位全加器进行LVS检验观察原理图与版图的匹配程度;

(6)针对自己画的版图,给出实现该全加器的工艺流程图。

二、电路设计方案

原理:

三个输入位:

数据位A和B,低位进位输入Ci

二个输出位:

全加和S,进位输出C0

表1真值表

A

B

Ci

S

C0

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

根据一位全加器的输入输出关系得:

图1全加器原理图

方案一:

传输门一位全加器

图2:

传输门一位全加器

优点:

晶体管使用数目少

缺点:

电路功耗大

方案二:

互补静态CMOS实现的全加器

图3:

互补静态CMOS实现的全加器

优点:

静态功耗小

缺点:

晶体管数目多,占硅片面积大,延迟时间高

三、电路特性仿真及分析

3.1电路图

全加器电路采用传统的CMOS电路构成,整个电路分为4行,P管与N管各两行。

由于进位电路的器件数少,用第2和第3行组成进位电路的前级,第1行和第4行组成求和电路的前级。

由于第2、3行的器件比1、4少,其有源区水平方向的长度比第1、4行短,可以让多晶C从第1行延伸到第4行而不跨越第2.3行的有源区,避免了形成寄生MOS管的可能。

PMOS管的衬底连接系统最高电位,NMOS管的衬底连接系统的最低电位。

电路原理图如图4所示:

图4一位全加器电路原理图

3.2电路图网表

*SPICEnetlistwrittenbyS-EditWin327.03

*WrittenonJan10,2015at22:

57:

48

*Waveformprobingcommands

.probe

.optionsprobefilename="Module1.dat"

+probesdbfile="C:

\Users\ASUS\Desktop\集成电路实践\tanner\S-Edit\MYB3110433031.sdb"

+probetopmodule="Module0"

.lib"C:

\Users\ASUS\Desktop\集成电路实践\ic_techfiles\cz6h+_v20.lib"tt

*Maincircuit:

Module0

M1CoN2VddVddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M2CoN2GndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M3N2AN12VddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M4N6BVddVddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M5N5AGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M6N2AN16GndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M7N5BGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M8N16BGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M9N2CiN5GndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M10N2CiN6VddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M11N12BN6VddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M12N6AVddVddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M13N19N2N1N1NENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M14N1AGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M15N1BGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M16N1CiGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M17N19CiN10GndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M18N10AN22GndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M19N22BGndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M20SUMN19GndGndNENHL=0.35uW=0.7uAD=66pPD=24uAS=66pPS=24u

M21N9CiVddVddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M22N9AVddN4PENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M23N9BVddN7PENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M24N19N2N9VddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M25N13BN11N14PENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M26N19CiN13N14PENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M27N11AN9N14PENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

M28SUMN19VddVddPENHL=0.35uW=1.4uAD=66pPD=24uAS=66pPS=24u

v29VddGnd5.0

v30AGndpulse(0.05.220n1n1n200n400n)

v31BGndpulse(0.05.0100n1n1n100n200n)

v32CiGndpulse(0.05.040n1n1n50n100n)

.modelPENHPMOS

.modelNENHNMOS

*Endofmaincircuit:

Module0

VININGNDPULSE(03.3010n50n100n)

.tran/op10n600nmethod=bdf

.printtranv(A)v(B)v(Ci)v(SUM)v(Co)

.end

3.3一位全加器电路仿真分析波形

给一位全加器电路网表输入高电平电源电压VDD和低电平GND,添加库,加入激励,再进行瞬态分析。

.includeF:

\13\tanner\TSpice70\models\ml2_125.md

vvddVDDGND5

vaAGNDPULSE(0505n5n50n100n)

vbBGNDPULSE(0505n5n60n120n)

vcCGNDPULSE(0505n5n70n140n)

.tran/op10n400nmethod=bdf

.printtranv(A)v(B)v(C)v(SUM)v(CO)

对一位全加器电路进行TSpice进行仿真,分析输出波形与自己设计电路的逻辑功能是否一致。

波形图如下图5所示:

图5一位全加器电路原理图输入输出仿真波形

四、一位全加器电路的版图绘制

4.1版图与DRC验证结果

用L-Edit版图绘制软件对一位全加器电路进行版图绘制,同时进行DRC检查,对于进位和求和的输出反相器都采用了比较大的宽长比,进位从左面输出,求和从右面输出,整个版图的宽度和长度显得比较适中。

一位全加器版图如图6所示:

图6一位全加器电路版图及DRC验证结果

4.2TSpice进行仿真

给一位全加器版图网表输入高电平电源电压VDD和低电平GND,添加库,加入激励,再进行瞬态分析,

.includeF:

\13\tanner\TSpice70\models\ml2_125.md

vvddVDDGND5

vaAGNDPULSE(0505n5n50n100n)

vbBGNDPULSE(0505n5n60n120n)

vcCGNDPULSE(0505n5n70n140n)

.tran/op10n400nmethod=bdf

.printtranv(A)v(B)v(C)v(SUM)v(CO)

对一位全加器版图进行TSpice进行仿真,分析输出波形与自己设计电路的逻辑功能是否一致。

波形图如下图7所示:

图7一位全加器版图输入输出仿真波形

4.3版图网表

*CircuitExtractedbyTannerResearch'sL-EditVersion9.00/ExtractVersion9.00;

*TDBFile:

F:

\13\tanner\bantu\wubingfeng.tdb

*Cell:

Cell0Version1.134

*ExtractDefinitionFile:

..\LEdit90\Samples\SPR\example1\lights.ext

*ExtractDateandTime:

07/02/2013-22:

10

.includeF:

\13\tanner\TSpice70\models\ml2_125.md

vvddVDDGND5

vaAGNDPULSE(0505n5n50n100n)

vbBGNDPULSE(0505n5n60n120n)

vcCGNDPULSE(0505n5n70n140n)

.tran/op10n400nmethod=bdf

.printtranv(A)v(B)v(C)v(SUM)v(CO)

*Warning:

LayerswithUnassignedAREACapacitance.

*

*

*

*

*

*

*Warning:

LayerswithUnassignedFRINGECapacitance.

*

*

*

*

*

*

*

*

*Warning:

LayerswithZeroResistance.

*

*

*

*

*NODENAMEALIASES

*1=SUM(29,27.5)

*7=CO(-138.5,36.5)

*12=B(-77.5,99)

*15=GND(20.5,34.5)

*16=A(-85.5,99)

*17=C(-69.5,99)

*19=VDD(19.5,86.5)

M1SUM2VDDVDDPMOSL=2uW=11u

*M1DRAINGATESOURCEBULK(371582)

M221310VDDPMOSL=2uW=11u

*M2DRAINGATESOURCEBULK(-2671-2482)

M35B6VDDPMOSL=2uW=11u

*M3DRAINGATESOURCEBULK(-1171-982)

M4VDDC5VDDPMOSL=2uW=11u

*M4DRAINGATESOURCEBULK(-571-382)

M510CVDDVDDPMOSL=2uW=11u

*M5DRAINGATESOURCEBULK(-3471-3282)

M66A2VDDPMOSL=2uW=11u

*M6DRAINGATESOURCEBULK(-1771-1582)

M7SUM2GNDGNDNMOSL=2uW=6u

*M7DRAINGATESOURCEBULK(340546)

M82138GNDNMOSL=2uW=6u

*M8DRAINGATESOURCEBULK(-2640-2446)

M93B4GNDNMOSL=2uW=6u

*M9DRAINGATESOURCEBULK(-1140-946)

M10GNDC3GNDNMOSL=2uW=6u

*M10DRAINGATESOURCEBULK(-540-346)

M118CGNDGNDNMOSL=2uW=6u

*M11DRAINGATESOURCEBULK(-3440-3246)

M124A2GNDNMOSL=2uW=6u

*M12DRAINGATESOURCEBULK(-1740-1546)

M13VDDB10VDDPMOSL=2uW=11u

*M13DRAINGATESOURCEBULK(-4271-4082)

M14VDDB18VDDPMOSL=2uW=11u

*M14DRAINGATESOURCEBULK(-5871-5682)

M1511BVDDVDDPMOSL=2uW=11u

*M15DRAINGATESOURCEBULK(-7871-7682)

M1613C11VDDPMOSL=2uW=11u

*M16DRAINGATESOURCEBULK(-7071-6882)

M1710AVDDVDDPMOSL=2uW=11u

*M17DRAINGATESOURCEBULK(-5071-4882)

M1818A13VDDPMOSL=2uW=11u

*M18DRAINGATESOURCEBULK(-6271-6082)

M19VDDA11VDDPMOSL=2uW=11u

*M19DRAINGATESOURCEBULK(-8671-8482)

M20VDD13COVDDPMOSL=2uW=11u

*M20DRAINGATESOURCEBULK(-10671-10482)

M21GNDB8GNDNMOSL=2uW=6u

*M21DRAINGATESOURCEBULK(-4240-4046)

M22GNDB14GNDNMOSL=2uW=6u

*M22DRAINGATESOURCEBULK(-5840-5646)

M239BGNDGNDNMOSL=2uW=6u

*M23DRAINGATESOURCEBULK(-7840-7646)

M2413C9GNDNMOSL=2uW=6u

*M24DRAINGATESOURCEBULK(-7040-6846)

M258AGNDGNDNMOSL=2uW=6u

*M25DRAINGATESOURCEBULK(-5040-4846)

M2614A13GNDNMOSL=2uW=6u

*M26DRAINGATESOURCEBULK(-6240-6046)

M27GNDA9GNDNMOSL=2uW=6u

*M27DRAINGATESOURCEBULK(-8640-8446)

M28GND13COGNDNMOSL=2uW=6u

*M28DRAINGATESOURCEBULK(-10640-10446)

*TotalNodes:

19

*TotalElements:

28

*TotalNumberofShortedElementsnotwrittentotheSPICEfile:

0

*ExtractElapsedTime:

1seconds

.END

五、LVS检查匹配

用layout-Edit中的lvs对一位全加器进行LVS检查验证,首先添加输入输出文件,选择要查看的输出,分析输出结果检查一位全加器电路原理图与版图的匹配程度;输出结果如下图8所示:

图8一位全加器LVS检查匹配图

由上图的Circuitsareequal.可得电路原理图和版图完全匹配。

六、总结

在本次课程设计过程中我学习到了许多课堂上无法学到的东西。

它能够让我对课堂上学到的知识进行查漏补缺,而且锻炼了我的逻辑思考能力。

在本次课程设计过程中我遇到一些课堂中从未有过的问题,通过网络查找和同学交流,大大促进了实训进程。

并在过程中进一步提高自身的创作、创新水平,扎实基础,扩展所学。

本次版图课程设计使用tanner软件绘出一位全加器的电路原理图,版图并进行仿真与匹配检查。

在绘制电路原理图过程中,由于改错了EXPORTnetlist的路径,所以在导出网表的时候出现问题,把原来的库文件给覆盖了,最后复制新的库文件才把问题解决了。

在绘制版图的时候要注意交叠的距离,间距,因为所要画的管子多所以尽量要节省面积,所以尽量用最小宽度来画。

最后还要进行DRC检查。

在导出网表的时候一定要先ReplaceSetup,如果不进行这一步那么后面不能导出网表,在lvs匹配检查的时候一定要把库文件加入电路原理图,否则在匹配的时候就会出现警告,并且在匹配检查的时候一定要把激励屏蔽。

在TSpice仿真时候要把激励加入,要仿真的时序加上,最后要分析仿真出来的波形与自己