正负脉宽数控调制信号发生器设计报告书.docx

《正负脉宽数控调制信号发生器设计报告书.docx》由会员分享,可在线阅读,更多相关《正负脉宽数控调制信号发生器设计报告书.docx(20页珍藏版)》请在冰豆网上搜索。

正负脉宽数控调制信号发生器设计报告书

课题十一正负脉宽数控调制信号发生器

一、课题目的

1.熟练掌握预置计数器的描述方法。

2.掌握VHDL语言反馈信号的处理。

3.设计正负脉冲宽度可调的数控调制信号发生器。

二、

课题原理

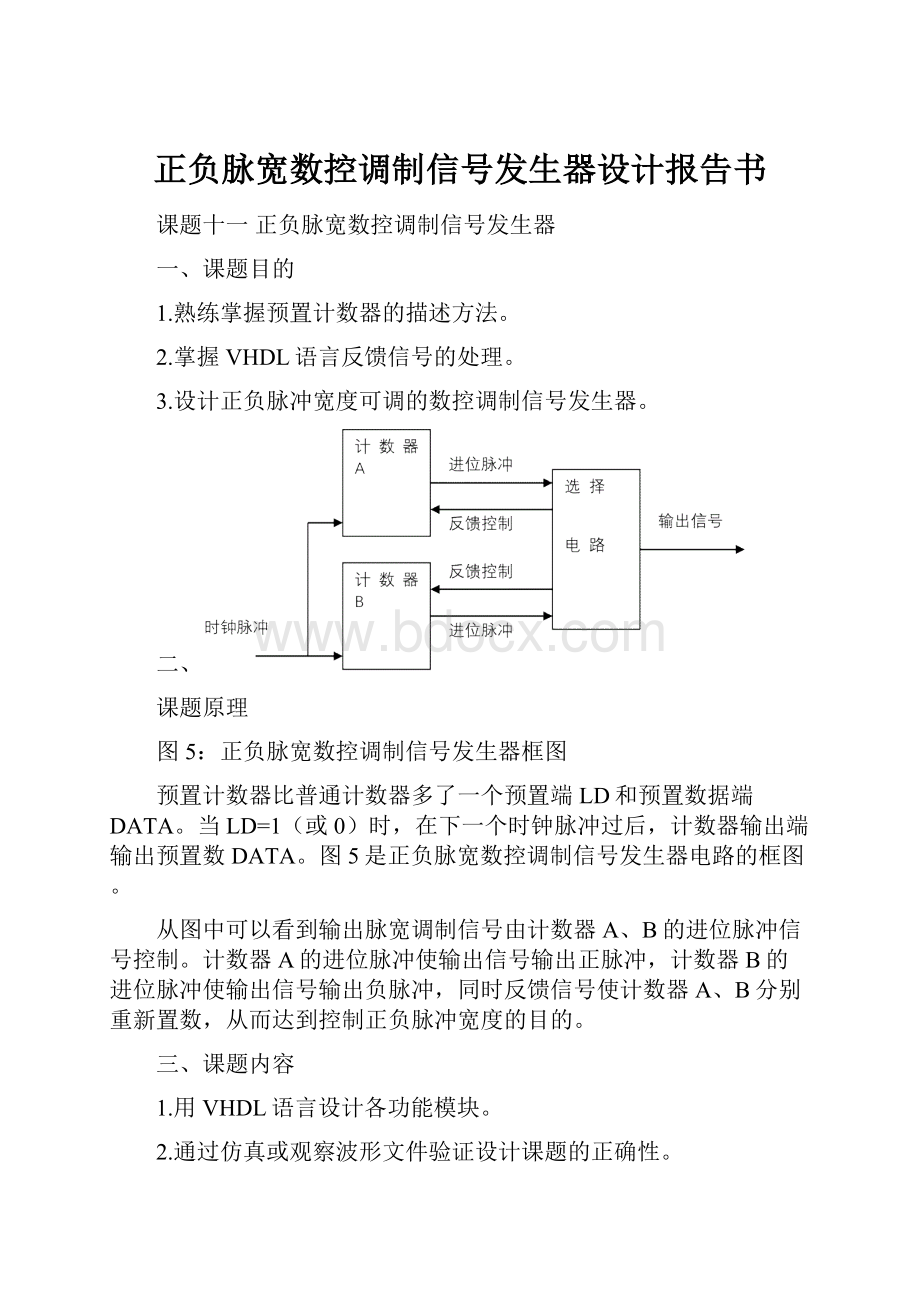

图5:

正负脉宽数控调制信号发生器框图

预置计数器比普通计数器多了一个预置端LD和预置数据端DATA。

当LD=1(或0)时,在下一个时钟脉冲过后,计数器输出端输出预置数DATA。

图5是正负脉宽数控调制信号发生器电路的框图。

从图中可以看到输出脉宽调制信号由计数器A、B的进位脉冲信号控制。

计数器A的进位脉冲使输出信号输出正脉冲,计数器B的进位脉冲使输出信号输出负脉冲,同时反馈信号使计数器A、B分别重新置数,从而达到控制正负脉冲宽度的目的。

三、课题内容

1.用VHDL语言设计各功能模块。

2.通过仿真或观察波形文件验证设计课题的正确性。

3.编译下载并通过示波器验证结果。

四、设计提示

1.选择电路可用一带清零端的D触发器构成,也可以用VHDL语言的进程语句进行描述。

2.注意用到反馈信号的地方,输出信号线应定义成Buffer类型。

五、课题报告要求

1.写出各模块的源程序。

2.画出详细电路图并分析电路的工作原理。

3.画出电路工作时序波形图。

4.书写心得体会。

1.绪论

1.1EDA和QuartusⅡ的简介及起源

EDA是英文“electronicdesignautomation”(电子自动化设计)的缩写,EDA技术是20世纪90年代迅速发展起来的,是现代电子设计的最新技术潮流,是综合现代电子技术和计算机技术的最新研究成果,是电子线路设计与分析的一门技术。

EDA包括电子线路的设计、计算机模拟仿真和电路分析及印制电路板的自动化设计三个方面的内容。

随着可编程逻辑器件迅速发展,出现了功能强大的全新的EDA工具。

具有较强描述能力的硬件描述语言(VHDL、VerilogHDL)及高性能综合工具的使用,使过去单功能电子产品开发转向系统级电子产品开发。

QuartusⅡ是Altera提供的FPGA/CPLD开发集成环境,Altera是世界上最大的可编程逻辑器件供应商之一。

QuartusⅡ是在21世纪初推出,是Altera前一代FPGA/CPLD集成开发环境MAX+plusⅡ的更新换代产品,其界面友好,使用环境便捷。

它提供了一种与结构无关的设计环境,使设计者能方便地进行设计输入、快速处理和器件编程。

QuartusⅡ设计工具完全支持VHDL、Verilog的设计流程,其内部嵌有VHDL、Verlog逻辑综合器。

QuartusⅡ包括模块化的编译器。

编译器包括的功能模块有分析/综合器(Analysis&Synthesis)、适配器(Fitter)、装配器(Assembler)、时序分析器(TimingAnalyzer)、设计辅助模块(DesignAssistant)、EDA网表文件生成器(EDANetlistWriter)、编辑数据接口(CompilerDatabaseInterface)等。

可以通过选择StartCompilation来运行所有的编译器模块,也可以通过选择Start来单独运行各个模块。

还可以通过选择CompilerTool,在CompilerTool窗口中运行该模块来启动编译器模块。

在CompileTool窗口中,可以打开该模块的设置文件或报告文件,或打开其它相关窗口。

1.2EDA的优势及其发展趋势

EDA技术的优势体现在:

●用HDL对数字系统进行抽象的行为与功能描述到具体的内部线路结构,从而可以在电子设计的各个阶段、各个层次进行计算机模拟验证,保证设计过程的正确性,可以大大降低设计成本,缩短设计周期。

●EDA工具之所以能够完成各种自动设计过程,关键是有种类库的支持,如逻辑仿真时的模拟库、逻辑综合时的综合库、版图综合时的版图库、测试综合时的测试库等。

●某些HDL本身也是文档型的语言(如VHDL),极大地简化了设计文档的管理。

●EDA中最为瞩目的功能,最具现代化电子设计技术特征的功能,是日益强大的逻辑设计仿真测试技术。

极大地提高了大规模系统电子设计的自动化程度。

EDA的发展趋势,表现在以下几个方面:

●超大规模集成电路的集成度和工艺水平不断提高,深亚微米(Deep-Submicron)工艺,如0.13um、90nm已经走向成熟,在一个芯片上完成的系统级的集成已经成为可能。

●由于工艺不断减小,在半导体材料上的许多寄生效应已经不能简单地补码忽略,这就对EDA工具提出了更高的要求。

同时,也使得IC生产线的投资更为巨大。

●高性能的EDA工具得到长足的发展,其自动化和智能化程度不断提高,为嵌入式系统设计提供了功能强大的开发环境。

●市场对电子产品提出了更高的要求,从而也对系统的集成度不断提出更高的要求。

同时,设计的效率也成了一个产品能否成功的因素,促使EDA工具应用更为广泛。

2.可自加载加法计数器的设计

取计数器的端口为:

脉冲输入端CLK、加载使能输入端LD(高电平有效)、预置输入端D、计数进位输出端CAO。

当脉冲CLK上升沿到来之时,若加载使能端LD有效,则通过预置端D可对计数器进行预置数。

之后,计数器就以此预置数为始,一直加1计数。

至计数到255时,输出端CAO输出1。

框图如图2.1。

其VHDL程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLCNT8IS

PORT(CLK,LD:

INSTD_LOGIC;

D:

ININTEGERRANGE0TO255;

CAO:

OUTSTD_LOGIC);

ENDLCNT8;

ARCHITECTUREBEHAVEOFLCNT8IS

SIGNALCOUNT:

INTEGERRANGE0TO255;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFLD='1'THENCOUNT<=D;

ELSECOUNT<=COUNT+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(COUNT)

BEGIN

IFCOUNT=255THENCAO<='1';

ELSECAO<='0';

ENDIF;

ENDPROCESS;

ENDBEHAVE;

3.信号发生器设计过程

3.1核心设计

此信号发生器是由两个完全相同的可自加载加法计数器LCNT8组成的,它的输出信号的高低电平脉宽可分别由两组8位预置数进行控制。

如果将初始值可预置的加法计数器的进位信号作为本计数器的初始预置加载信号LD,则可构成计数初始值自加载方式的加法计数器,从而构成数控分频器,如图3.1所示。

这就是本设计的核心部分。

取顶层文件中信号PINT,当计数器1输出CAO1=1时,PINT=0;当计数器2输出CAO2上升沿脉冲到来时,PINT=1。

将PINT赋予信号发生器的输出端POUT,就可以得到高低电平宽度可调的方波信号。

先将预置数设置好,则CAO1输出1后,由LD1=NOTPINT=1,计数器1立刻进行预置,重新计数;计数器2亦然。

于是产生持续的可调脉宽信号发生器。

其相应的VHDL程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYPULSEIS

PORT(CLK:

INSTD_LOGIC;

A,B:

INSTD_LOGIC_VECTOR(7DOWNTO0);

POUT:

OUTSTD_LOGIC);

ENDPULSE;

ARCHITECTUREBEHAVEOFPULSEIS

COMPONENTLCNT8

PORT(CLK,LD:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

CAO:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALCAO1,CAO2:

STD_LOGIC;

SIGNALLD1,LD2:

STD_LOGIC;

SIGNALPINT:

STD_LOGIC;

BEGIN

U1:

LCNT8PORTMAP(CLK=>CLK,LD=>LD1,D=>A,CAO=>CAO1);

U2:

LCNT8PORTMAP(CLK=>CLK,LD=>LD2,D=>B,CAO=>CAO2);

PROCESS(CAO1,CAO2)

BEGIN

IFCAO1='1'THENPINT<='0';

ELSIFCAO2'EVENTANDCAO2='1'THENPINT<='1';

ENDIF;

ENDPROCESS;

LD1<=NOTPINT;LD2<=PINT;POUT<=PINT;

ENDBEHAVE;

3.2总体设计

考虑到是数控调制,本设计对预置输入进行数码显示。

因为计数器范围是0~255,故而一个预置数的显示要用到3个数码管;一共两组预置数,则要用到6个数码管,所以设计一个6进制计数器COUNT6来控制数码管的位选。

至于数码管的段选,先将预置8位输入D转化为12位的供3个数码管显示的数组,当COUNT6计数为0时,把第一个12位数组(对应第一个预置数)中的低4位送入译码管的输入端BEDIN;当计数为1时,把中间4位送入译码管的BEDIN;当计数为2时,把高4位送入译码管的BEDIN;当计数为3时,把第二个12位数组(对应第二个预置数)中的低4位送入译码管的输入BEDIN端……如此可实现对输入的数码显示。

考虑到实验箱上提供的脉冲是20MHz,既不便于灯的观察又不便于数码显示,所以设计了一个1000Hz的分频器,将脉冲分频为1000Hz的脉冲输入。

总体设计原理框图如附录1。

4.软件仿真及硬件验证

4.1软件仿真

输入取A=252,B=254。

可得到仿真波形,如图4.1:

图4.1EDA仿真波形

4.2引脚锁定

输入时钟CLK接16管脚PIN_16,A、B预置数输入利用16个拨码开关可实现,A、B各占8个。

可调脉宽的输出POUT可接PIN_104,以便用发光二极管的亮灭速度来观察结果。

6进制计数器COUNT6的输出CNT接3-8译码器的输入SEL,译码器SEG7DEC的输出SEGT接数码管的段选输入端。

如表4.1:

4.3硬件验证

向目标芯片Cyclone系列的EP1C3T144C8下载适配后的逻辑设计文件,通过PIN_49~PIN_56对应的8个拨码开关输入控制高电平信号脉宽的预置数(对应于A输入),并显示于数码管1、2、3;再通过PIN_57~PIN_62、PIN_67、PIN_68对应的8个拨码开关输入控制低电平信号脉宽的预置数(对应于B输入),并显示于数码管4、5、6。

可观察到,当A较低,而B输入较高时,发光二极管的点亮时间大于熄灭时间;当A较高,B输入较低时,发光二极管的点亮时间少于熄灭时间;当A输入255时,POUT=0,则发光二极管一直保持熄灭状态。

也可以将POUT接入到示波器,通过观察示波器的显示波形得到结果。

5.设计总结

在传统的数字电子系统或IC设计中,手工设计占了较大的比例。

一般都是先按电子系统的具体功能要求进行功能划分,然后对每个子模块画出真值表,用卡诺图进行手工逻辑简化,写出布尔表达式,画出相应的逻辑线路图,再据此选择元器件,设计电路板,最后进行实测与调试。

显然,手工设计的缺点让人越来越不可接受。

故而,EDA技术变得越来越重要,作为当代大学生,要与时俱进,更要掌握这种电子自动化设计。

通过EDA的模拟编译、适配、仿真,可以大大缩短设计周期,降低设计成本。

EDA仿真测试技术只需通过计算机就能对所设计的电子系统从各种不同层次的系统性能特点完成一系列准确的测试与仿真操作,在完成实际系统的安装后,还能对系统的目标器件进行所谓边界扫描测试、嵌入式逻辑分析仪的应用,这一切都极大地提高了大规模系统电子设计的自动化程度。

至于课设报告中涉及到的WORD排版知识,随着一次次课设的进行,也一点点积累,现在可以说是得心应手。

至少在排版时不会遇到障碍。

总之本次课设,让我重新熟悉了QuartusⅡ、WORD两个常用软件,也复习了一遍VHDL语言的相关知识,又熟悉了一遍用VHDL语言进行编程的过程。

参考文献

[1]潘松,黄继业.EDA技术与VHDL(第2版).北京:

清华大学出版社,2007.

[2]孟庆辉,刘辉,程继航,石静苑.EDA技术实用教程.北京:

国防工业出版社,2008.

[3]刘江海.EDA技术.武汉:

华中科技大学出版社,2009.

[4]杨跃.FPGA应用开发实战技巧精粹.北京:

人民邮电出版社,2009.

[5]王辉,殷颖,陈婷,俞一鸣等.MAX+plusII和QuartusII应用与开发技巧.北京:

机械工业出版社,2007.

附录1整体原理框图

附录2设计程序

可自加载加法计数器LCNT8

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYLCNT8IS

PORT(CLK,LD:

INSTD_LOGIC;

D:

ININTEGERRANGE0TO255;

CAO:

OUTSTD_LOGIC);

ENDLCNT8;

ARCHITECTUREBEHAVEOFLCNT8IS

SIGNALCOUNT:

INTEGERRANGE0TO255;

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFLD='1'THENCOUNT<=D;

ELSECOUNT<=COUNT+1;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(COUNT)

BEGIN

IFCOUNT=255THENCAO<='1';

ELSECAO<='0';

ENDIF;

ENDPROCESS;

ENDBEHAVE;

1000Hz分频器DIV

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYDIVIS

GENERIC(DATAWIDTH:

INTEGER:

=25);

PORT(CLK:

INSTD_LOGIC;

QO:

OUTSTD_LOGIC);

END;

ARCHITECTUREBHVOFDIVIS

SIGNALCOUNT:

STD_LOGIC_VECTOR(DATAWIDTH-1DOWNTO0);

BEGIN

PROCESS(CLK)

BEGIN

IFRISING_EDGE(CLK)THEN

IFCOUNT=20000THEN

COUNT<=(OTHERS=>'0');

ELSECOUNT<=COUNT+1;

IFCOUNT<10000THEN

QO<='0';

ELSE

QO<='1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

ENDBHV;

6进制计数器CNT6

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCOUNT6IS

PORT(CLK:

INSTD_LOGIC;

CNTOUT:

BUFFERSTD_LOGIC_VECTOR(2DOWNTO0));

END;

ARCHITECTUREBHVOFCOUNT6IS

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCNTOUT<5THEN

CNTOUT<=CNTOUT+1;

ELSECNTOUT<=(OTHERS=>'0');

ENDIF;

ENDIF;

ENDPROCESS;

END;

将8位预置数转化为12位数组change

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCHANGEIS

PORT(D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(11DOWNTO0));

ENDCHANGE;

ARCHITECTUREBHVOFCHANGEIS

BEGIN

PROCESS(D)

BEGIN

CASEDIS

WHEN"00000000"=>DOUT<="000000000000";

WHEN"00000001"=>DOUT<="000000000001";

WHEN"00000010"=>DOUT<="000000000010";

WHEN"00000011"=>DOUT<="000000000011";

WHEN"00000100"=>DOUT<="000000000100";

WHEN"00000101"=>DOUT<="000000000101";

WHEN"00000110"=>DOUT<="000000000110";

WHEN"00000111"=>DOUT<="000000000111";

……

……

……

WHEN"11111000"=>DOUT<="001001001000";

WHEN"11111001"=>DOUT<="001001001001";

WHEN"11111010"=>DOUT<="001001010000";

WHEN"11111011"=>DOUT<="001001010001";

WHEN"11111100"=>DOUT<="001001010010";

WHEN"11111101"=>DOUT<="001001010011";

WHEN"11111110"=>DOUT<="001001010100";

WHEN"11111111"=>DOUT<="001001011001";

ENDCASE;

ENDPROCESS;

ENDBHV;

段选译码器SEG7DEC

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYSEG7DECIS

PORT(BEDIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

SEGOUT:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDSEG7DEC;

ARCHITECTUREBHVOFSEG7DECIS

BEGIN

PROCESS(BEDIN)

BEGIN

CASEBEDINIS

WHEN"0000"=>SEGOUT<="0111111";

WHEN"0001"=>SEGOUT<="0000110";

WHEN"0010"=>SEGOUT<="1011011";

WHEN"0011"=>SEGOUT<="1001111";

WHEN"0100"=>SEGOUT<="1100110";

WHEN"0101"=>SEGOUT<="1101101";

WHEN"0110"=>SEGOUT<="1111101";

WHEN"0111"=>SEGOUT<="0000111";

WHEN"1000"=>SEGOUT<="1111111";

WHEN"1001"=>SEGOUT<="1101111";

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

ENDBHV;

顶层文件PULSE

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYPULSEIS

PORT(CLK:

INSTD_LOGIC;

A,B:

INSTD_LOGIC_VECTOR(7DOWNTO0);

POUT:

OUTSTD_LOGIC;

SEGT:

OUTSTD_LOGIC_VECTOR(6DOWNTO0);

CNT:

OUTSTD_LOGIC_VECTOR(2DOWNTO0));

ENDPULSE;

ARCHITECTUREBEHAVEOFPULSEIS

COMPONENTLCNT8

PORT(CLK,LD:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

CAO:

OUTSTD_LOGIC);

ENDCOMPONENT;

COMPONENTCOUNT6IS

PORT(CLK:

INSTD_LOGIC;

CNTOUT:

BUFFERSTD_LOGIC_VECTOR(2DOWNTO0));

ENDCOMPONENT;

COMPONENTCHANGEIS

PORT(D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(11DOWNTO0));

ENDCOMPONENT;

COMPONENTSEG7DECIS

PORT(BEDIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

SEGOUT:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDCOMPONENT;

COMPONENTDIVIS

PORT(CLK:

INSTD_LOGIC;

QO:

OUTSTD_LOGIC);

ENDCOMPONENT;

SIGNALCAO1,CAO2,CLKO:

STD_LOGIC;

SIGNALLD1,LD2,PINT:

STD_LOGIC;

SIGNALBED1:

STD_LOGIC_VECTOR(3DOWNTO0);

SIGNALCNT1:

STD_LOGIC_VECTOR(2DOWNTO0);

SIGNALDOUT1,DOUT2:

STD_LOGIC_VECTOR(11DOWNTO0);

BEGIN

U1:

LCNT8PORTMAP(CLK=>CLKO,LD=>LD1,D=>A,CAO=>CAO1);

U2:

LCNT8PORTMAP(CLK=>CLKO,LD=>LD2,D=>B,CAO=>CAO2);

U3:

COUNT6PORTMAP(CLK=>CLKO,CNTOUT=>CNT1);