STM8L中文参考手册1要点.docx

《STM8L中文参考手册1要点.docx》由会员分享,可在线阅读,更多相关《STM8L中文参考手册1要点.docx(116页珍藏版)》请在冰豆网上搜索。

STM8L中文参考手册1要点

简介

本参考手册的目标应用程序开发人员。

它提供了完整的信息如何使用stm8l05xx,stm8l15xx和stm8l16xx微控制器的存储器和外围设备。

该stm8l05xx/stm8l15xx/stm8l16xx是一个家庭的不同存储密度的微控制器和外围设备。

这些产品是专为超低功耗应用。

可用的外设的完整列表,请参阅产品数据表。

订购信息,引脚说明,机械和电气设备的特点,请参阅产品数据表。

关于STM8SWIM通信协议信息和调试模块,请参阅用户手册(um0470)。

在STM8的核心信息,请参阅STM8的CPU编程手册(pm0044)。

关于编程,擦除和保护的内部快闪记忆体,请参阅STM8L闪存编程手册(pm0054)。

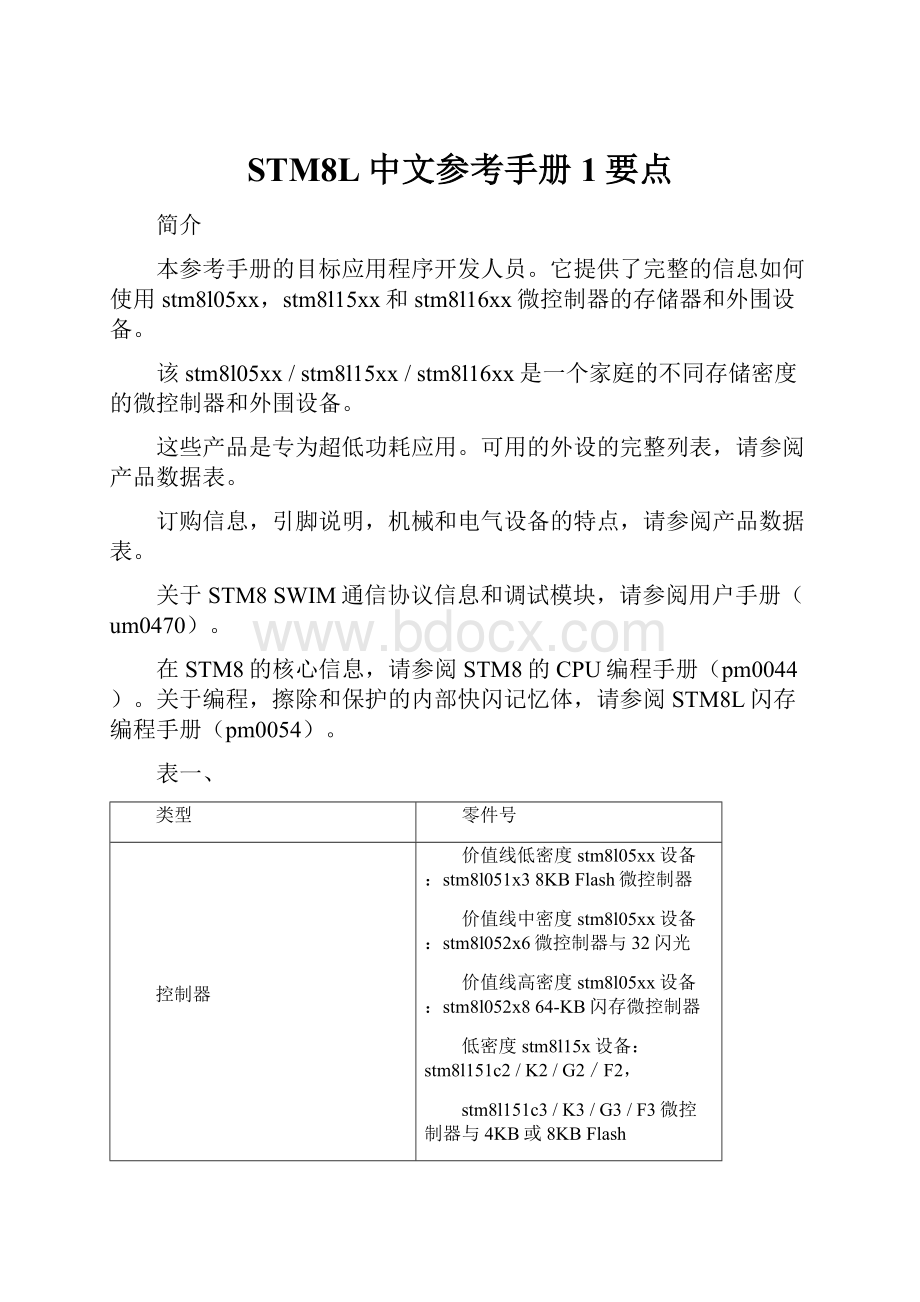

表一、

类型

零件号

控制器

价值线低密度stm8l05xx设备:

stm8l051x38KBFlash微控制器

价值线中密度stm8l05xx设备:

stm8l052x6微控制器与32闪光

价值线高密度stm8l05xx设备:

stm8l052x864-KB闪存微控制器

低密度stm8l15x设备:

stm8l151c2/K2/G2/F2,

stm8l151c3/K3/G3/F3微控制器与4KB或8KBFlash

中密度stm8l15xx设备:

stm8l151c4/K4/G4,

微控制器stm8l151c6/K6/G6,stm8l152c4/K4和stm8l152c6/K6

微控制器与16-KB或32闪光

培养基+密度stm8l15xx设备:

stm8l151r6和

stm8l152r6微控制器与闪存(32比中密度器件广泛的外设范围)

高密度stm8l15xx设备:

stm8l151x8和stm8l152x8

随着64-KB闪存微控制器(相同的外周设置为中等+)

高密度stm8l16xx设备:

stm8l162x8微控制器与闪存(相同的外周设置为64-KB高密度stm8l152设备加AES硬件加速器

目录

1中央处理单元(CPU)。

30。

1.1引言30

1.2CPU的寄存器。

30。

1.2.1描述CPU寄存器。

..。

30

1.2.2STM8CPU寄存器图。

..。

34

1.3全球配置寄存器(cfg_gcr)。

34。

1.3.1激活水平。

..。

34

1.3.2游泳禁用。

..。

35

1.3.3描述全局配置寄存器(cfg_gcr)。

..。

35

1.3.4全局配置寄存器图及复位值。

..。

35

2启动ROM...36

3程序存储器和数据存储器。

37。

3.1引言37

3.2术语。

37。

3.3个主要的快闪存储器的特点。

38。

3.4记忆的组织。

39。

3.4.1低密度设备的存储器组织。

39

3.4.2介质密度的装置记忆的组织。

..。

40

3.4.3介质+密度装置记忆的组织。

..。

41

3.4.4高密度存储器组织。

..。

42

3.4.5专有代码区(译)。

43

3.4.6用户区(UBC)。

43

3.4.7数据的EEPROM(数据)。

..。

46

3.4.8主程序区。

46

3.4.9选项字节。

..。

46

3.5内存保护。

47。

3.5.1读出保护。

47

3.5.2内存访问安全系统(质量)。

47

3.5.3使写访问选项字节。

49

3.6内存编程49

3.6.1同时读写(读写网)。

..。

49

2/573文档ID15226转9

rm0031内容

3.6.2字节编程。

..。

49

3.6.3字编程。

50

3.6.4块编程。

50

3.6.5选项字节编程。

52

Flash3.7的低功耗模式。

52。

3.8例ICP和IAP。

52。

3.9闪光寄存器57

3.9.1闪光控制寄存器1(flash_cr1)。

57

3.9.2闪光控制寄存器2(flash_cr2)。

58

3.9.3Flash程序存储器的解密密钥寄存器(flash_pukr)。

58

3.9.4数据EEPROM解除保护关键寄存器(flash_dukr)。

..。

59

3.9.5闪光状态寄存器(flash_iapsr)。

..。

59

3.9.6Flash寄存器图及复位值。

60

4单线接口模块(游泳)和调试模块(DM)61

4.1引言61

4.2个主要特征。

61。

4.3游泳模式。

61。

5内存和寄存器图62

5.1寄存器描述缩写。

62。

6功率控制(PWR)。

63。

6.1电源63

6.2上电复位(POR)/掉电复位(PDR)。

64。

6.3掉电复位(BOR)65

6.4可编程电压检测器(PVD)。

66。

6.5的内部参考电压(vrefint)67

6.6的电压调节器68

6.7压水堆寄存器69

6.7.1功率控制和状态寄存器1(pwr_csr1)。

69

6.7.2压水堆控制和状态寄存器2(pwr_csr2)。

..。

70

6.7.3PWR寄存器图及复位值。

70

7低功耗模式。

71。

7.1减速系统时钟72

文件编号15226启93/573

内容rm0031

7.2周门控时钟(PCG)72

7.3等待模式(WFI或WFE模式)。

72。

7.4等待中断(WFI)模式。

73。

7.5等待事件(WFE)模式73

7.5.1WFE寄存器。

74

7.5.2WFE寄存器图及复位值。

..。

79

7.6低功率运行模式。

80。

7.6.1进入低功率运行模式。

..。

80

7.6.2退出低功率运行模式。

..。

80

7.7低功率待机模式。

80。

7.8停止模式。

81。

7.8.1进入暂停模式。

81

7.8.2退出暂停模式。

..。

81

7.9主动停止模式。

82。

8复位(RST)。

83。

8.1“复位状态”和“下复位”的定义。

83。

8.2外部复位(NRST引脚)83

8.2.1异步外部复位的描述。

..。

83

8.2.2配置活动/PA1引脚作为通用输出。

84

8.3内部复位84

8.3.1上电复位(POR)。

..。

84

8.3.2独立看门狗复位。

..。

84

8.3.3窗口看门狗复位。

..。

84

8.3.4游泳复位。

84

8.3.5非法操作码复位。

84

8.4个寄存器。

85。

8.4.1复位引脚配置寄存器(rst_cr)。

..。

85

8.4.2复位状态寄存器(rst_sr)。

85

8.4.3RST寄存器图及复位值。

..。

86

9控制的时钟(CLK)。

87。

9.1引言87

9.2HSE时钟。

88。

9.3个HSI时钟90

4/573文档ID15226转9

rm0031内容

9.4LSE时钟。

90。

9.5集成电路的时钟。

91。

9.6系统的时钟源。

91。

9.6.1系统启动。

..。

..91

9.6.2系统时钟切换程序。

..。

..92

9.7周门控时钟(PCG)95

9.8时钟安全系统(CSS)95

9.8.1时钟安全系统对HSE。

..。

..95

9.8.2时钟安全系统在伦敦经济学院。

..。

..96

9.8.3CSSLSE控制和状态寄存器(csslse_csr)。

..。

..97

9.8.4CSSLSE寄存器图及复位值。

..98

9.9时钟和液晶时钟。

98。

9.10声钟。

98。

9.11可配置时钟输出能力(CCO)。

98。

9.12个独立的系统时钟的时钟源TIM2/TIM3。

99。

9.13时钟中断99

9.14时钟寄存器。

100。

9.14.1系统时钟分频寄存器(clk_ckdivr)。

..。

100

9.14.2时钟RTC寄存器(clk_crtcr)。

..。

100

9.14.3内部时钟寄存器(clk_ickcr)。

..。

102

9.14.4周围门控时钟寄存器1(clk_pckenr1)。

..。

103

9.14.5周围门控时钟寄存器2(clk_pckenr2)。

..。

104

9.14.6周围门控时钟寄存器3(clk_pckenr3)。

..。

105

9.14.7可配置时钟输出寄存器(clk_ccor)。

106

9.14.8外部时钟寄存器(clk_eckcr)。

107

9.14.9系统时钟状态寄存器(clk_scsr)。

..。

108

9.14.10系统时钟切换寄存器(clk_swr)。

..。

109

9.14.11开关控制寄存器(clk_swcr)。

109

9.14.12时钟安全系统寄存器(clk_cssr)。

..。

..110

9.14.13时钟嘀寄存器(clk_cbeepr)。

..。

111

9.14.14HSI校准寄存器(clk_hsicalr)。

..111

9.14.15HSI时钟校准微调寄存器(clk_hsitrimr)。

..。

..112

9.14.16HSI解锁寄存器(clk_hsiunlckr)。

..。

..112

9.14.17主调节器控制状态寄存器(clk_regcsr)。

..。

..113

9.14.18时钟寄存器图及复位值。

..。

..114

10个通用I/O端口(GPIO)。

115。

10.1引言115

10.2个GPIO的主要特点。

115。

10.3端口的配置与使用。

116。

10.3.1输入模式。

..。

117

10.3.2输出模式。

118

10.4复位配置118

10.5未使用的I/O引脚。

118。

10.6低功率模式118

10.7输入模式的细节118

10.7.1函数输入。

118

10.7.2中断能力。

119

10.8个输出模式的详细介绍。

119。

10.8.1交替输出功能。

119

10.8.2斜率控制。

119

10.9个GPIO寄存器。

120。

10.9.1端口X输出数据寄存器(px_odr)。

120

10.9.2端口X引脚输入寄存器(px_idr)。

120

10.9.3X口数据方向寄存器(px_ddr)。

121

10.9.4端口X控制寄存器1(px_cr1)。

..。

121

10.9.5端口X控制寄存器2(px_cr2)。

..。

122

10.9.6外围函数映射。

122

10.9.7GPIO寄存器图及复位值。

..。

122

11路由接口(RI)和系统配置

控制器(syscfg)。

123。

11.1引言123

11.2日的主要特点。

123。

11.2.1RI功能描述。

125

11.2.2的I/O组。

125

11.2.3TIM1输入捕捉路由。

..。

127

11.2.4TIM2和TIM3路由。

128

11.2.5比较器的路由。

..129

11.2.6DAC的路由。

..。

..129

11.2.7内部参考电压的路由。

131

11.3日131个中断

6/573文档ID15226转9

rm0031内容

11.4日寄存器。

131。

11.4.1定时器输入捕捉路由寄存器1(ri_icr1)。

..。

131

11.4.2定时器输入捕捉路由寄存器2(ri_icr2)。

..。

132

11.4.3I/O输入寄存器1(ri_ioir1)。

..。

132

11.4.4I/O输入寄存器2(ri_ioir2)。

..。

132

11.4.5I/O输入寄存器3(ri_ioir3)。

..。

133

11.4.6I/O控制寄存器1(ri_iocmr1)。

..。

133

11.4.7I/O控制寄存器2(ri_iocmr2)。

..。

133

11.4.8I/O控制寄存器3(ri_iocmr3)。

..。

134

11.4.9I/O寄存器开关1(ri_iosr1)。

..。

134

11.4.10I/O寄存器开关2(ri_iosr2)。

..。

136

11.4.11I/O寄存器开关3(ri_iosr3)。

..。

137

11.4.12IO控制寄存器(ri_iogcr)。

..。

138

11.4.13模拟开关寄存器1(ri_ascr1)。

140

11.4.14模拟开关寄存器2(ri_ascr2)。

140

11.4.15电阻控制寄存器(ri_rcr)。

141

11.4.16控制寄存器(ri_cr)。

142

11.4.17IO屏蔽寄存器1(ri_iomr1)。

..。

143

11.4.18IO屏蔽寄存器2(ri_iomr2)。

..。

143

11.4.19IO屏蔽寄存器3(ri_iomr3)。

..。

144

11.4.20IO屏蔽寄存器4(ri_iomr4)。

..。

144

11.4.21I/O输入寄存器4(ri_ioir4)。

..。

145

11.4.22I/O控制寄存器4(ri_iocmr4)。

..。

145

11.4.23I/O寄存器开关4(ri_iosr4)。

..。

146

11.4.24RI寄存器图及复位值。

..。

147

11.5syscfg寄存器。

149。

11.5.1syscfg映射控制寄存器1(syscfg_rmpcr1)。

..。

149

11.5.2syscfg映射控制寄存器2(syscfg_rmpcr2)。

..。

150

软件syscfg映射控制寄存器3(syscfg_rmpcr3)。

..。

151

11.5.4syscfg寄存器图及复位值。

..。

152

12中断控制器(ITC)。

153。

12.1引言153

12.2中断屏蔽和处理流程。

153。

12.2.1服务等待中断。

154

12.2.2中断源。

155

12.3个中断和低功耗模式156

文件编号15226启97/573

内容rm0031

12.4的激活水平/低功率模式控制。

157。

12.5并行嵌套中断管理157

12.5.1并发中断管理模式。

..。

157

12.5.2嵌套中断管理模式。

..。

158

12.6个外部中断159

12.7中断指令。

160。

12.8中断映射。

160。

12.9国贸EXTI寄存器。

161。

12.9.1CPU条件码寄存器中断位(CCR)。

161

12.9.2软件优先级寄存器X(itc_sprx)。

..。

162

12.9.3外部中断控制寄存器1(exti_cr1)。

..。

162

12.9.4外部中断控制寄存器2(exti_cr2)。

..。

164

12.9.5外部中断控制寄存器3(exti_cr3)。

..。

165

12.9.6外部中断控制寄存器4(exti_cr4)。

..。

166

12.9.7外部中断状态寄存器1(exti_sr1)。

166

12.9.8外部中断状态寄存器2(exti_sr2)。

167

12.9.9外部中断端口选择寄存器(exti_conf1)。

..。

168

12.9.10外部中断端口选择寄存器(exti_conf2)。

..。

169

12.9.11ITC和完全寄存器图及复位值。

..。

170

13直接存储器存取控制器(DMA)。

171。

13.1DMA的介绍。

171。

词汇。

..。

171

13.2DMA的主要特点。

172。

13.3的DMA功能描述173

13.3.1DMA交易。

173

13.3.2DMA仲裁者。

..。

174

13.3.3DMA通道。

..。

174

13.3.4蛋白Dma1请求映射。

..。

..181

13.3.5DMA硬件要求描述。

..。

183

13.4DMA低功率模式184

13.5DMA中断。

185。

13.6DMA寄存器。

185。

13.6.1DMA全球配置和状态寄存器(dma_gcsr)。

..185

13.6.2DMA全局中断寄存器1(dma_gir1)。

186

13.6.3DMA通道配置寄存器(dma_cxcr)。

..。

..186

8/573文档ID15226转9

rm0031内容

13.6.4DMA通道状态和优先级寄存器(dma_cxspr)。

..。

..188

13.6.5DMA数据传输寄存器(dma_cxndtr)。

..。

..189

13.6.6DMA地址寄存器(外周高dma_cxparh)。

..。

189

13.6.7DMA地址寄存器(dma_cxparl)低周。

..190

13.6.8DMA通道3周地址1地址的高高的记忆

寄存器(dma_c3parh_c3m1arh)。

190

13.6.9DMA通道3周地址低1低内存地址

寄存器(dma_c3parl_c3m1arl)。

..。

191

13.6.10DMA存储器地址寄存器(dma_cxm0arh)高0。

..。

191

13.6.11DMA存储器地址寄存器(dma_cxm0arl)低0。

..。

192

13.6.12DMA通道3个内存0扩展地址寄存器

(dma_c3m0ear)。

..。

192

13.6.13DMA寄存器图及复位值。

..。

193

14模拟到数字转换器(ADC)。

195。

14.1引言195ADC

14.2模数转换器的主要特点。

195。

14.3ADC功能描述。

196。

14.3.1一般描述。

196

14.3.2数模拟通道。

..。

197

14.3.3ADC开关控制。

..。

197

14.3.4单转换模式。

..。

197

14.3.5连续转换模式。

199

14.3.6ADC时钟。

199

14.3.7模拟看门狗。

..。

199

14.3.8中断。

200

14.3.9信道选择(扫描模式)。

..。

200

14.3.10数据完整性。

201

14.3.11DMA传输。

..。

201

14.3.12配置分辨率。

201

14.3.13数据对齐。

..。

201

14.3.14可编程采样时间。

202

14.3.15施密特触发器禁用。

203

14.3.16温度传感器。

..。

203

14.3.17内部参考电压转换。

204

14.4ADC低功耗模式。

204。

14.5ADC中断。

204。

文件编号15226启99/573

内容rm0031

14.6ADC寄存器。

205。

14.6.1ADC配置寄存器1(adc_cr1)。

..。

205

14.6.2ADC配置寄存器2(adc_cr2)。

..。

206

14.6.3ADC配置寄存器3(adc_cr3)。

..。

207

14.6.4ADC状态寄存器(adc_sr)。

..。

208

14.6.5ADC数据寄存器高(adc_drh)。

..。

209

14.6.6ADC数据寄存器低(adc_drl)。

..。

209

14.6.7ADC的高门槛高(adc_htrh)寄存器。

210

14.6.8ADC的高门槛低(adc_htrl)寄存器。

210

14.6.9ADC低阈值寄存器高(adc_ltrh)。

210

14.6.10ADC低阈值寄存器低(adc_ltrl)。

211

14.6.11ADC通道序列1寄存器(adc_sqr1)。

211

14.6.12ADC通道序列寄存器2(adc_sqr2)。

212

14.6.13ADC通道选择扫描3(adc_sqr3)。

..。

212

14.6.14ADC通道选择扫描4(adc_sqr4)。

..。

213

14.6.15ADC触发禁用1(adc_trigr1)。

213

14.6.16ADC触发禁用2(adc_trigr2)。

214

14.6.17ADC触发禁用3(adc_trigr3)。

214

14.6.18ADC触发禁用4(adc_trigr4)。

214

14.6.19ADC寄存器图及复位值。

..。

215

15个数字到模拟转换器(DAC)。

216。

15.1引言216DAC

15.2个DAC的主要特点。

216。

15.3的DAC功能描述。

218。

1.X使DAC通道。

..。

218

15.3.2DAC输出缓冲区启用。

..。

218

15.3.3DAC输出开关配置。

218

15.3.4数据格式。

219

15.3.5DAC转换序列。

..。

219

15.3.6DAC输出电压。

219

15.3.7DAC触发选择。

..。

219

15.3.8DAC的DMA请求。

..。

220

15.3.9DACDMA下溢中断。

..。

220

15.3.10噪声的产生。

..。

220

15.3.11三角波的产生。

..。

221

15.3.12双DAC转换。

..。

222

10/573文档ID15226转9

rm0031内容

15.4个DAC寄存器。

226。

15.4.1DAC通道控制寄存器1(dac_chxcr1)。

..226

15.4.2DAC通道控制寄存器2(dac_chxcr2)。

..。

..227

15.4.3DAC软件触发寄存器(dac_swtrigr)。

..。

228

15.4.4DAC状态寄存器(dac_sr)。

..228

15.4.5DAC通道X右对齐的数据保持寄存器高

(dac_rdhrh)。

..。

..229

15.4.6DAC通道X右对齐的数据保持寄存器低

(dac_chxrdhrl)。

..。

..229

15.4.7DAC通道X左对齐数据保持寄存器高

(dac_chxldhrh)。

..。

..229

15.4.8DAC通道X左对齐数据保持寄存器低

(dac_chxldhrl)。

..230

15.4.9DAC通道×8位数据保持寄存器

(dac_chxdhr8)。

230

15.4.10DAC通道X双模式右对齐的数据保持寄存器高

(dac_dchxrdhrh)。

231

15.4.11DAC通道X双模式右对齐的数据保持寄存器低

(dac_dchxrdhrl)。

..。

231

15.4.12DAC通道X双模式左对齐数据保持寄存器高

(dac_dchxldhrh)。

..。

232

15.4.13DAC通道X左对齐数据保持寄存器低

(dac_dchxldhrl)。

..。

232

15.4.14DAC通道的双模式的8位数据保持寄存器

(dac_dchxdhr8)。

..。

..233

15.4.15DAC通道数据输出寄存器高

(dac_chxdorh)。

..。

233

15.4.16DAC通道数据输出寄存器低

(dac_chxdorl)。

..。

233

15.4.17DAC寄存器映射及复位值。

..。

..234

16个比较器(COMP)。

237。

16.1公司简介。

237。

16.2计算机的主要特点。

239。

16.3比较器1(COMP1)。

240。

16.4比较器2(comp2)。

241。

16.5使用比较器在窗口模式242

16.6公司的低功耗模式。

243。

16.7比赛中断243

16.8公司注册。

244。

文件编号15226启911/573

内容rm0031

16.8.1比较器控制和状态寄存器1(comp_csr1)。

..。

244

16.8.2比较器控制和状态寄存器2(comp_csr2)。

..。

245

16.8.3比较器控制和状态寄存器3(comp_csr3)。

..。

246

16.8.4比较器控制和状态寄存器4(comp_csr4)。

..。

247

16.8.5比较器控制和状态寄存器5(comp_csr5)。

..。

247

16.8.6COMP寄存器图及复位值。

..。

248

17液晶显示控制器。

249。

17.1液晶显示控制器的介绍。

249。

17.1.1定义。

249

17.2液晶显示控制器的主要特点。

250。

17.3液晶显示功能描述。

252。

17.3.1一般描述。

252

17.3.2频率发生器。

..。

253

17.3.3通用驱动程序。

256

17.3.4段驱动器。

264

1