Cadence学习笔记4PCB板设计.docx

《Cadence学习笔记4PCB板设计.docx》由会员分享,可在线阅读,更多相关《Cadence学习笔记4PCB板设计.docx(28页珍藏版)》请在冰豆网上搜索。

Cadence学习笔记4PCB板设计

Cadence学习笔记4__PCB板设计

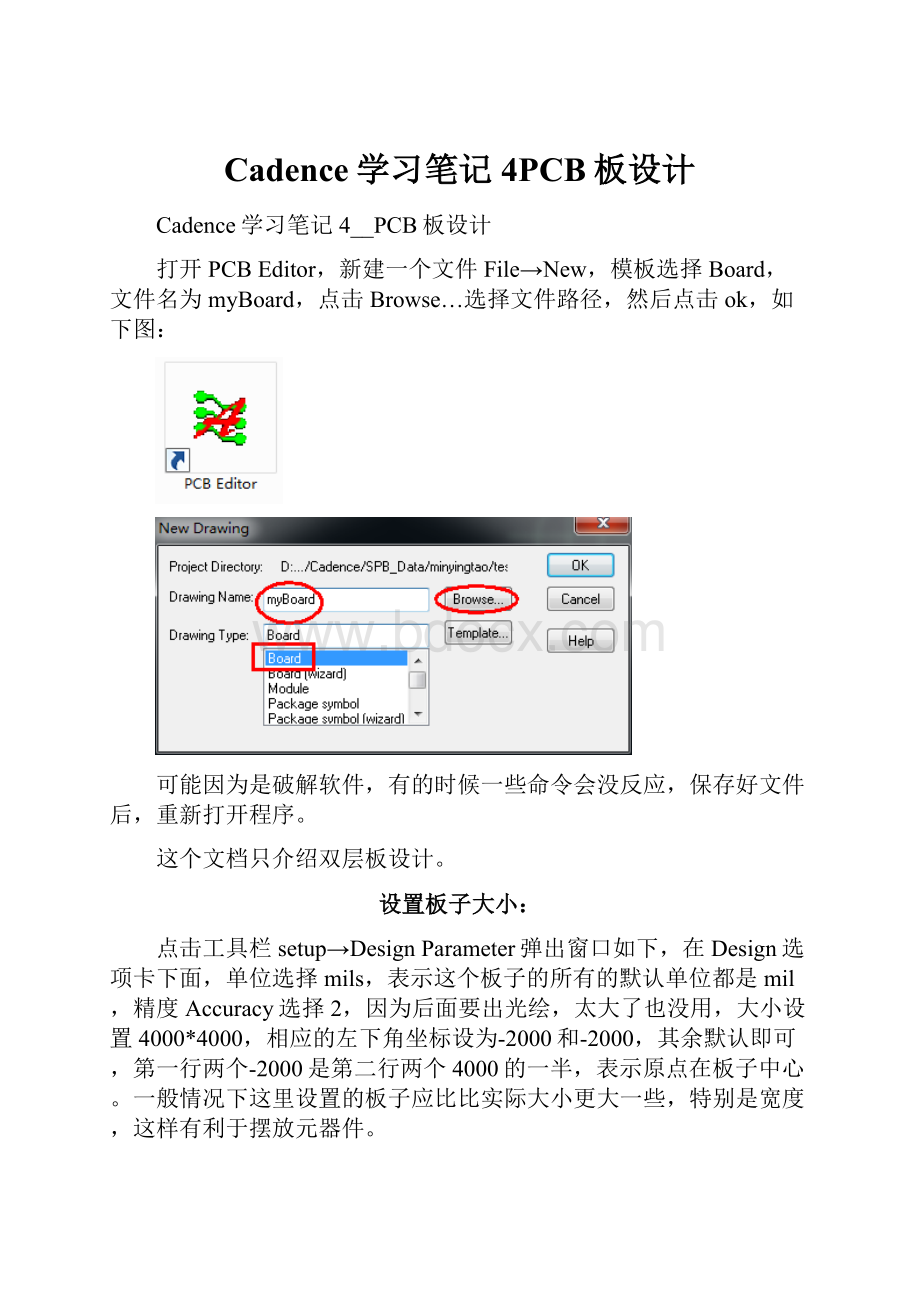

打开PCBEditor,新建一个文件File→New,模板选择Board,文件名为myBoard,点击Browse…选择文件路径,然后点击ok,如下图:

可能因为是破解软件,有的时候一些命令会没反应,保存好文件后,重新打开程序。

这个文档只介绍双层板设计。

设置板子大小:

点击工具栏setup→DesignParameter弹出窗口如下,在Design选项卡下面,单位选择mils,表示这个板子的所有的默认单位都是mil,精度Accuracy选择2,因为后面要出光绘,太大了也没用,大小设置4000*4000,相应的左下角坐标设为-2000和-2000,其余默认即可,第一行两个-2000是第二行两个4000的一半,表示原点在板子中心。

一般情况下这里设置的板子应比比实际大小更大一些,特别是宽度,这样有利于摆放元器件。

接着设置栅格点大小,点击工具栏setup→Grids,勾选“GridsOn”显示栅格点,在非电气属性区域Non-Etch设置为25mil,表示布局<摆放元件)时的最小栅格点为25mil,在电气属性区域AllEtch及下面的TOP和BOTTOM设为5mil,表示布线时的最小栅格点为5mil,在AllEtch这里的Spaceingx和y可以设置所有层的电气属性栅格点,在下面的TOP和BOTTOM可以单独设置各个层,这里默认的是两层,如果还有更多的层,都会在这里显示。

设置板框:

板框大小就是做出来的板子的实际大小,根据实际情况确定。

点击Add→line或左侧工具栏的划线图标

,在右侧工具栏选择Options,然后选择类BoardGeometry和子类Outline,其余默认,如下图。

其右上角有三个很小的图标

,可以点击右上角的图标

将其展开,否则鼠标移开后会自动收缩,展开后也可以点击

将其收缩。

如果不小心点击

关掉了这个小窗口,可以在上方工具栏View→Windows勾选Options,同样的Visibility和Find都可以这么操作。

如果Options、Visibility和Find窗口都是点击了

展开,那么可以点击

将其中一个置于最前。

用输入坐标的方式确定板框大小,大小为2760*2160,在下方命令行输入x13801080回车,确定了第一个点坐标;然后输入ix-2760回车,向左移动2760mil;输入iy-1080回车,向下移动1080mil;输入ix2760回车,向右移动2760mil;输入iy1080回车,向上移动1080mil。

最后鼠标右击Done结束,可以看见白色的边框线。

导角:

就是将矩形边框的四个直角变成圆弧,免得割伤手,工具栏Manufacture→Dimension/

Draft→Filet,在右侧工具栏设置大小,一般的100mil即可,这里写100mil,然后点击矩形边框一个直角的相邻两边,如下图,直角变成圆弧了。

同样的设置其余角,设置好后右击Done结束。

如果想改变导角大小,激活命令后直接输入新的导角大小,然后点击各个角的相邻边即可。

注意,Z-copy命令产生的板边框不能设置导角,必须是line的方式画的边框才行。

允许布线区:

点击上方工具栏Setup→Areas→RouteKeepin,在右侧工具栏options中选择类RouteKeepin和子类All,Type为无填充Unfilled,其余默认,如果All最左边的小方块是黑色的,表示这个没有显示,点击这个黑色的小框变成和All左边一样的黄色,表示可以显示了。

允许布线区一般在板框内100mil,即长和宽都小200mil,距板边太近会在生产时被夹具夹断走线。

输入坐标即可,这里的大小为2560*1960,默认颜色为黄色。

也可以用一种快速放置的方式,在放好板边框后,点击上侧工具栏Edit→Z-copy,options选择类RouteKeepin和子类All,下面的Size选择Contract,表示新的边框在原来边框内部,Expand表示在外部,Offset表示偏移多少,设为100,单位是在设置板子大小时设置的mil,如下图。

然后点击刚才设置的板子边框的任意一点,就出现了黄色的允许布线区,右击Done结束。

快速创建:

这里介绍快速创建板框和允许布线区,点击上侧工具栏Setup→Outlines→BoardOutline弹出下面窗口,如果还没有创建就会默认选择Create,BoardEdgeClearance表示板框和允许布线区的间距,下面如果选择DrawRectangle,就可以在板子中用鼠标点击或输入坐标创建,输入的坐标是矩形的两个对角的坐标,最后点击ok结束。

如果选择的不是DrawRectangle而是PlaceRectangle,就会显示下图右的样子,分别输入板框的宽度和高度,用鼠标点击或在命令行输入矩形左下角的坐标即可。

如果选择的是DrawPolygon,表示可以画出由直线和直角构成的任意形状,直接鼠标点击或输入坐标即可,如下图。

如果已经创建了这个东西,下次打开这个窗口的时候,会默认选择Edit,然后在下面输入板框和允许布线区的间距再点击ok即可。

如果此时选择Create,会提示删除当前的板框和允许布线区,因为一个板子只能有一个。

同样的,可以选择Move移动或Delete删除。

允许摆放区:

点击上方工具栏Setup→Areas→PackageKeepin,在右侧工具栏options中选择类PackageKeepin和子类All,Type为无填充Unfilled,Shapegrid选择Currentgrid,其余默认。

同样的,在允许布线区内100mil,即长和宽都小200mil,距离太近会在生产时被夹具夹断走线。

输入坐标即可,这里的大小为2360*1760,默认颜色为紫色。

设置好后如下图:

同样可以用一种快速放置的方式,在放好板边框后<也可以用允许布线区,那么应该是偏移100),点击上侧工具栏Edit→Z-copy,options选择类PackageKeepin和子类All,下面的Size选择Contract,表示新的边框在原来边框内部,Expand表示在外部,Offset表示偏移多少,设为200,单位是在设置板子大小时设置的mil,如下图。

然后点击刚才设置的板子边框的任意一点,就出现了紫色的允许摆放区,右击Done结束。

放置安装孔:

可以直接放置机械孔,点击上方工具栏Place→Manually,先在AdvancedSettings选项卡下面勾选Library,表示在自带库和指定路径中搜索元件,指定的路径就是做封装时在工具栏Setup→Userpreferences→Paths→Library的padpath和psmpath添加的路径。

如果勾选AutoHide表示放置元件时自动隐藏这个窗口,放置完成后又显示,如下图左,然后回到PlacementList选项卡,如下图右,选择Mechanicalsymbols,下面会显示可用的机械零件,也就是机械孔,勾选一个放置即可,现在选择MTG156,右下方出现预览,直接放置到板子中即可,也可以通过输入坐标的方式放置,也就是勾选这个之后,在下方命令栏输入坐标回车,如x00。

注意每次勾选只能放置一次,下次放置还要勾选。

记得放完后要点击ok关闭窗口,如果点击Cancel就取消了刚才的放置。

也可以自己做一个机械孔,先做一个带有Flash的通孔类焊盘,命名为installhole.pad,添加好路径,在做一个封装installHole.dra,以机械零件的方式加入该焊盘,在封装中加入Place_Bound_Top和Ref,Ref在Assembly层的元件中心输入*即可,封装如下图所示。

然后在PCB设计中点击上方工具栏Place→Manually,先在AdvancedSettings选项卡下面勾选Library,再在PlacementList选项卡选择Packagesymbols,如下图,勾选INSTALLHOLE,右下方出现预览,鼠标移到PCB板中会看到一个机械孔,点击鼠标放置或输入坐标放置都可以,注意每次勾选只能放置一次,下次放置还要勾选,放置完成之后点击ok结束放置。

安装孔和与元件一样,要在允许摆放区内。

这里顺便介绍一下Move命令,点击Edit→Move或点击上侧工具栏图标

,可以在右侧Find中勾选要选中的类型,然后选中元件、边框、线等移动,此时可以直接点击放置,也可以输入坐标放置。

导入网表:

打开PCB板后,点击File→Import→Logic,弹出下面的窗口,在Cadence选项卡选择DesignentryHDL,Always和Importchangesonly,下面的Importdirectory选择原理图目录下的allegro目录,然后点击ImportCadence按钮,显示下面的进度条,最后弹出一个报告,报告的最后会说明有没有错误,如果有警告,如下图,一定要解决,仔细看前面的内容可以知道具体错误。

解决了错误之后,可以成功导入网表,并显示下面的提示信息

打开上方工具栏Place→Manually,看到显示所有未摆放的元件,勾选任意一个可以看到右下角显示预览,如果没有显示,可能是封装错误,或封装路径没有添加<在PCBEditor里面点击工具栏Setup→UserPreferences→Path→Library→padpath和psmpath添加封装所在路径,不支持子目录搜索,一个完整的封装应该包括焊盘文件*.pad,数据文件*.psm,Device文件*.txt,封装文件*.dra)

摆放元件的4种方式:

A.手动一个个摆放:

点击工具栏Place→Manually,弹出上图的窗口,可以在AdvancedSettings选项卡下面勾选AutoHide,表示放置时隐藏窗口,放置完成后又显示,删除PCB中的某个原件后,这里又显示该元件,因为这里都是没有摆放的元件。

B.原理图交互式摆放:

打开原理图组件OrCADCaptureCIS,点击上侧工具栏Options→Preference,打开选项卡Miscellaneous,勾选EnableIntertoolCommunication,表示打开原理图组件和PCB组件的数据传递工具,这样就可以将原理图组件中的一些元件属性或原理图属性传递到PCB组件中,传递的途径是网表的导出与导入。

下面还有个Allowcomponentmovewithconnectiviychanges,也可以勾选上,画线时方便。

接着在PCBEditor中点击Place→Manually激活摆放元件命令,在原理图中选一个元件右击选择最后一项PCBEditorSelect,将鼠标移动到PCBEditor中,鼠标上会悬挂该元件摆放即可

C.原理图整页摆放:

在OrCADCaptureCIS工程树目录里选一个原理图页,如第一页miniSystem_page1,点击工具栏Edit→Browse→Parts弹出下面的窗口,选择默认的即可,点击ok

然后在弹出的窗口中按住Shift用鼠标点击选择所有的元件,点击工具栏Edit→Properties,弹出下面的窗口,点击New新建一个属性,输入属性名和属性值如下,点击ok后在窗口右侧显示一个PAGE属性,所有的元件都有这个属性而且属性值都为1,点击ok即可<要删除该属性就选中该列点击Remove),其它各页都这样设置,Name都为PAGE,Value不同,设为页面编号即可。

最后创建网表,选中工程文件*.dsn后点击工具栏Tools→CreateNetlist弹出下面的窗口,按下面的步骤点击Setup,在弹出的窗口中点击Edit…编辑配置文件,然后在下面的位置上添加PAGE=YES表示添加刚才添加的PAGE属性,保存关闭即可,然后要记得勾选AllowUserDefinedProperties允许用户自定义属性,InputBoard和OutPutBoard都选自己的板子文件*.brd的路径,最后导出网表即可。

在PCBEditor中点击File→Import→Logic,要勾选Createuser-definedproperties,再导入网表

点击工具栏Place→Quickplace→选择Placebyproperty/value,选择Page属性,属性值选择1或2或3,下面的Edge至少勾选一个,表示元件放置的位置,右侧的BoardSide选择放在哪一层,最后要点击Place放置,之后点击ok

D.快速摆放所有元件:

在PCBEditor中点击Edit→Quickplace,选择placeallcomponents,下面设置摆放的位置和层,点击Place,点击ok。

颜色管理器:

工具栏Display→Color/Visibility或点击图标

,打开颜色管理器,默认选择左上角的Layers,如果选择Nets会显示不同的网络并设置网络颜色。

主要的颜色设置如下:

布局基本知识:

电源大小不同的模块应该分开,因为后面铺铜时要分割铺铜。

中央芯片周围的去耦电容放到底层,不要和中央芯片在同一层;

数字部分与模拟部分分开,因为模拟电路对噪声比较敏感;

对噪声敏感的电路<有磁珠、滤波器),滤波出来后直接接到中央芯片管脚上,越近越好,且不要通过过孔<就是要最先布线);

原理图中去噪部分常是电源进来接磁珠,再是大电容、小电容、引脚,布局布线也应如此;

时钟和RAM都会产生很大的干扰,因此要远离模拟器件,如果对时钟用引脚去耦的方式,会将噪声滤的很干净,Flash速度慢、干扰小,高速数据总线干扰大;

线性电源的噪声不太大,而开关电源噪声大,要远离运放,因此开关电源要放在对噪声不太敏感的器件旁边;

电容不要随便摆,如3.3V和1.2V交叉放;

越小的电容越靠近所去耦的芯片,因为平面去耦时,电容是有去耦半径的;

球形封装的去耦电容可放在芯片中间,效果很好<值指很小的,如0.1uF,值大放外面);

设置线宽:

线宽、线间距、引脚间距和区域规则等都是约束规则设置的内容,这里把几个最常用的规则设置一下,其余的在约束规则里面介绍。

在PCBEditor中点击工具栏Setup→Constraints→Physical→PhysicalConstraintSet→AllLayers,点击PCS的Objects一列,上面显示的是DEFAULT,右击选择Create→PhysicalCSet,弹出下面右图的窗口,输入规则名,比如说LineWidth20Mil,点击ok,然后输入各项的值,比如说线宽设为20,Neck设为20和400<或其他值),过孔设为VIA26<点击过孔名弹出一个窗口,选择即可,右侧是自己选择的,可以选择多个,布线时在Options中选择具体哪一个过孔)其余默认,如下图。

如果要删除该约束,右击约束名Delete即可。

再点击Physical→Net→AllLayers,将GND和5V,3V3这三个网络的ReferencedPhysicalCset属性设为刚才设置的LineWidth20Mil,如下图:

设置线间距:

点击Setup→Constraints→Spacing→SpacingConstraintSet→AllLayers→All,同样的新建一个约束,命名为SPACE12MIL,并且将所有的值都设为12,如下图:

然后,在Spacing→Net→AllLayers,将GND和5V,3V3这三个网络的ReferencedSpacingCset属性设为刚才设置的SPACE12MIL,如下图:

设置区域规则:

点击Setup→Constraints→Physical→Regions→AllLayers,右击Dsn的Objects属性,也就是板子文件的文件名myBoard,选择Create→Region,分别为下图的两个值,然后关闭约束规则管理器。

在PCBEditor中点击工具栏Shape→Rectangular,用鼠标拉出一个矩形区域,并在Options中选择类Constraint和子类All,在下面的AssigntoRegion选择刚设置的区域,区域规则表示在整个PCB约束规则设置之后,可以对某一个区域设置新的规则。

手动布线:

点击左侧工具栏的布线图标

或是快捷键F3,然后再Options中设置,如下图,可以设置当前层级如下图当前层级为Top,下一行表示如果画线时加了过孔,下一层就到了Bottom,这两个选项在布线时都可以改变,布线时右击也可以选择当前层下面可以选择过孔,接着设置线的线型直线Line或圆弧Arc,角度有45和90,Miter表示几倍于默认线宽最小值,下图1xwidth表示1倍,同时显示了约束中设置的线宽5,也可以在这里直接改,Bubble选Hugonly等,表示布线时自动避开线、焊盘和过孔,Shovepreferred表示推挤模式,Hugpreferred优先报警,报警不行就会推挤。

下面的Shovevias如果是off表示不推挤过孔,选Minimal表示尽量不推挤,Full表示优先推挤过孔。

勾选Gridless表示线自动对齐栅格点。

勾选Snaptoconnectpoint表示自动连接到焊盘中心,勾选Replaceetch表示自动替换正在画的相同两个引脚之间的线,一般这两个都勾选。

画线接近终点时右击Finish自动完成,画线右击选择Toggle改变出现方向。

修线:

Route→Slide或点击左侧工具栏修线图标

,Options还可以选择一些东西,如勾选Tswithsegments表示移动T形点<拓扑点),勾选Viaswithsegments表示修线时移动过孔。

自动布线:

不要用自动布线功能。

工具栏Route→PCBRouter→RouteNet(s>ByPick,然后在Find中输入网络回车,RouteAutomatic→selletions选项卡下AllSelect中选一要布的网络,在RouteEditor,RouterSetup重点RouteUndo表示取消刚才的自动布线。

其余设置:

摆放元件后发现有很多信息,现在来设置一下显示。

关闭飞线:

Display→BlankRats→All。

显示飞线:

Display→ShowRats→All。

按网络显示:

在Find中选Net,在More左边直接输网络名回车。

移动元件:

Edit→Move,右侧工具栏只勾选symbols,下面的FindByName选Symbols(orpin>,Name,输入元件参考编号,如C1,R2等,元件就挂在鼠标上,摆放即可。

移动、翻转、镜像:

点击Edit→Move启动Move命令后点击一个元件,元件挂在鼠标上,右击选择Rotation可以翻转,Options可以设置翻转角度,其余类似。

用的最多的命令:

Move,Mirror,Spin。

更新封装:

Place→Updatesymbol。

移动原点:

Setup→DesignParameters→Design选项卡→Moveorigin中填写x和y坐标,或者在Setup→ChangeDrawingorigin,鼠标点击PCB中一点,就是原点了。

高亮:

Display→HighLight,再点某一个元件<或网络)即可高亮,高亮颜色在颜色管理器中Display→TemporaryHighLight可设置,可高亮元件、DRC错误、网络等。

取消高亮:

Display→DehighLight。

设置原件或网络颜色:

Display→Assigncolor,在Options选择颜色,点击元件或网络等,在Find中可以勾选要设置的东西。

在颜色管理器中Display→Color/Visibility中左上角点击Nets<默认是Layers)可设置不同网络颜色。

动态显示走线长度:

Setup→UserPreference→Route→Connect,勾选allegro_etch_length_on,画线时线长信息跟着鼠标显示。

它上面的allegro_dynam_timing若选on,表示画线时动态显示线长是否超过约束中对线长的规定<红色表示超出了,+100表示超出100mil,单位是约束管理器中规定的,不一定是mil)。

DRC:

点击Display→Status→UpdateDRC显示DRC错误个数,更改约束规则后更新DRC也在这里,点击最左方的小方块可以查看错误信息,或者单击工具栏Display→Elements,在右侧Find中只勾选DRCerrors,然后点击一个DRC错误的小蝴蝶结,会显示出具体错误。

也可以在工具栏Tools→UpdateDRC更新DRC。

可以点Display→WaiveDRCs显示不同DRC。

点击Setup→DesignParameters→Display选项卡→DRCMarkerssize设置DRC上字母大小。

铺铜:

点击工具栏Shape下的Rectangular矩形、Circle圆形或Polygon任意形状,然后在Options中选择Etch类和子类Top或Bottom,Type选择动态铜皮Dynamiccopper,然后在Assignnetname下指定一个网络,比如Gnd,其余默认,在PCB中用鼠标拖出一个区域或在命令行输入坐标确定这个区域,结束后右击Done结束。

此时可点工具栏Display→Element在点一下铜皮,检查一下网络是否指定正确。

编辑铜皮:

Shape→EditBoundary,在边界上拉一个以边界为一个边的形状,可以挖掉一块铜皮,Shape→Manuallvoid/cavity→各种形状,比如说在铜皮上拉一个圆就挖掉了。

铜皮合并:

若有几块铜皮重叠但是没有形成一块,可以合并,但它们必须是同一网络且同一类型<动态或静态铜皮),点击Shape→Mergeshape,点击要合并的铜皮即可。

删除孤岛:

工具栏Shape→DeleteIslands,Options中会显示孤岛数量,点击DeleteAllonlayers删除所有孤岛,右击Done。

不同电层的孤岛要在不同层分别删除,在Options中选择即可。

隐藏铜皮:

就是不显示铜皮,只显示铜皮边框。

工具栏Setup→UserPreference→Display→Shape_file→勾选no_shape_fill,一般要点击View→Refresh或图标

刷新一下。

查看报告、数据库检查:

查看报告:

工具栏Tools→Reports或QuickReports,常用的右未连接引脚UnconnectedPinsReport,动态铜皮状态<是否smooth状态)ShapeDynamicstate,没有指定网络的铜皮Shapenonet,孤岛ShapeIslands,DRC错误DesignRulesCheckReport。

数据库检查<在铺铜、DRC等各种检查之后进行):

Tools→DatabaseCheck,3个都勾选上,如下图,点击Check,然后点击Viewlog查看结果,根据报告修改错误,一般是没有错误没有警告。