EDA实验讲义.docx

《EDA实验讲义.docx》由会员分享,可在线阅读,更多相关《EDA实验讲义.docx(27页珍藏版)》请在冰豆网上搜索。

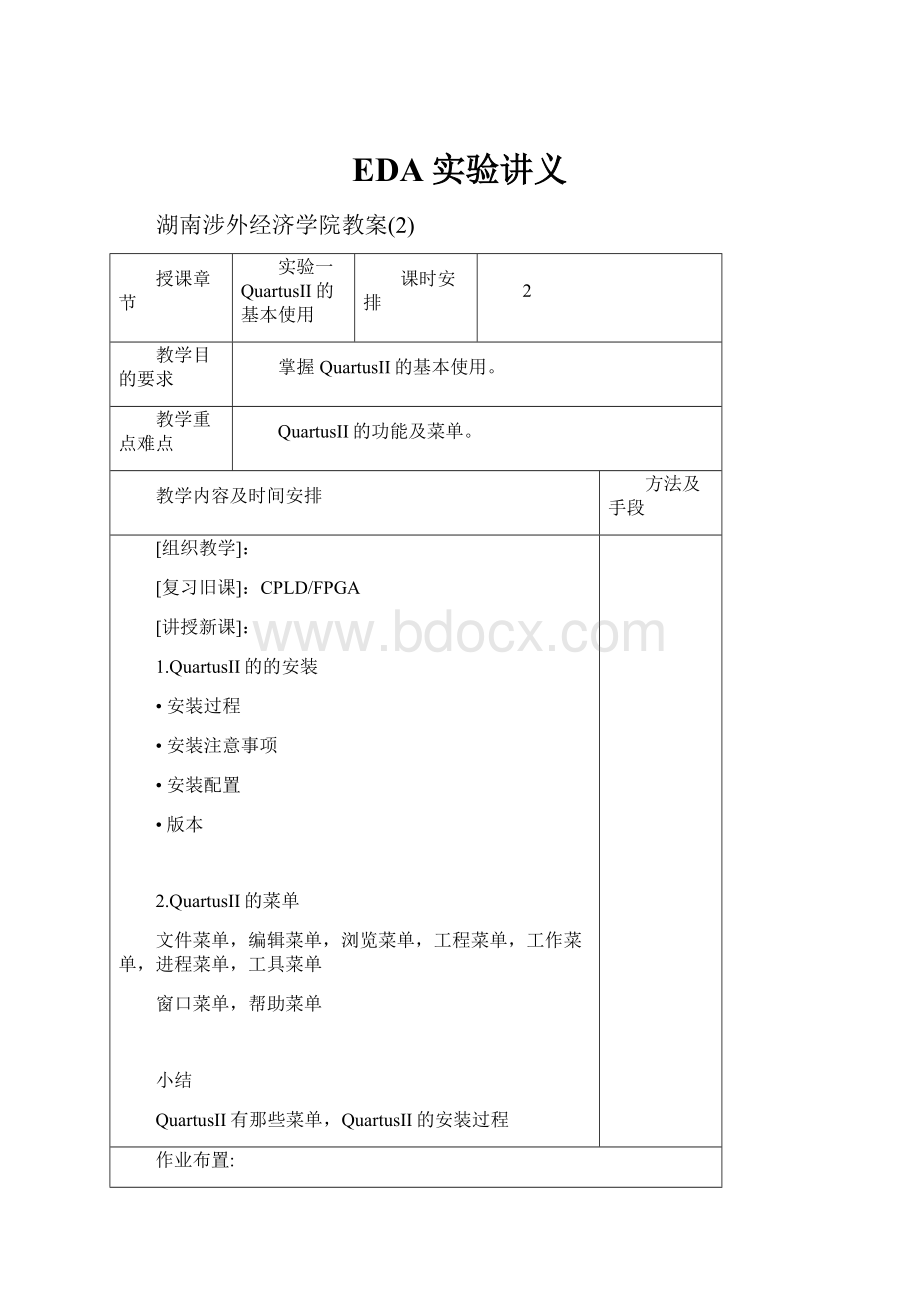

EDA实验讲义

湖南涉外经济学院教案

(2)

授课章节

实验一QuartusII的基本使用

课时安排

2

教学目的要求

掌握QuartusII的基本使用。

教学重点难点

QuartusII的功能及菜单。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

CPLD/FPGA

[讲授新课]:

1.QuartusII的的安装

•安装过程

•安装注意事项

•安装配置

•版本

2.QuartusII的菜单

文件菜单,编辑菜单,浏览菜单,工程菜单,工作菜单,进程菜单,工具菜单

窗口菜单,帮助菜单

小结

QuartusII有那些菜单,QuartusII的安装过程

作业布置:

备注:

湖南涉外经济学院教案(4)

授课章节

实验二QuartusII的图形式输入

课时安排

2

教学目的要求

掌握QuartusII的图形式输入。

教学重点难点

原理图的绘制。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.半加器的图形输入方式

新建工程,新建图形文件,输入原理图,编译

2.二选一数据选择器的图形输入

新建工程,新建图形文件,输入原理图,编译

小结

作业布置:

备注:

湖南涉外经济学院教案(6)

授课章节

实验三QuartusII的语言式输入

课时安排

2

教学目的要求

掌握QuartusII的文本输入。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

QuartusII的原理图输入

[讲授新课]:

1.QuartusII的VHDL输入设计

创建源文件和工程文件

选择目标器件

综合方式选择

综合方式选择

开始综合

查看综合结果

其他操作

小结

作业布置:

备注:

湖南涉外经济学院教案(8)

授课章节

实验四基本逻辑的VHDL描述

课时安排

2

教学目的要求

掌握基本逻辑的VHDL描述。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.门电路的VHDL描述

与门,或门

非门

异或门,同或门

与非门,或非门

2.触发器的VHDL描述

JK触发器

D触发器

T触发器

小结

作业布置:

备注:

湖南涉外经济学院教案(10)

授课章节

实验五QuartusII的使用-3/8译码器

课时安排

2

教学目的要求

掌握3/8译码器的VHDL设计。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.源代码

libraryieee;

useieee.std_logic_1164.all;

--实体说明

entitydecoderis

port(ADDR:

instd_logic_vector(7downto0);

G1,G2A,G2B:

instd_logic;--三八译码器使能输入

C,B,A:

instd_logic;--译码输入端

Y:

outstd_logic_vector(7downto0)--译码输出端

);

enddecoder;

--结构体说明

architecturehavofdecoderis

signalcom:

std_logic_vector(2downto0);

begin

com<=C&B&A;

process(com,G1,G2A,G2B)

begin

if(G1='1'andG2A='0'andG2B='0')then--此条件成立时译码器输出有?

casecomis

when"000"=>Y<="11111110";

when"001"=>Y<="11111101";

when"010"=>Y<="11111011";

when"011"=>Y<="11110111";

when"100"=>Y<="11101111";

when"101"=>Y<="11011111";

when"110"=>Y<="10111111";

when"111"=>Y<="01111111";

whenothers=>Y<="11111111";

endcase;

else

Y<="11111111";

endif;

endprocess;

endhav;

小结

作业布置:

备注:

湖南涉外经济学院教案(12)

授课章节

实验六QuartusII的使用-7段LED显示译码器

课时安排

2

教学目的要求

掌握7段LED显示译码器的VHDL设计。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.源代码

process(knum)

begin

caseknumis

when"0000"=>seg<="00111111";

when"0001"=>seg<="00000110";

when"0010"=>seg<="01011011";

when"0011"=>seg<="01001111";

when"0100"=>seg<="01100110";

when"0101"=>seg<="01101101";

when"0110"=>seg<="01111101";

when"0111"=>seg<="00000111";

when"1000"=>seg<="01111111";

when"1001"=>seg<="01101111";

when"1010"=>seg<="01110111";

when"1011"=>seg<="01111100";

when"1100"=>seg<="00111001";

when"1101"=>seg<="01011110";

when"1110"=>seg<="01111001";

when"1111"=>seg<="01110001";

whenothers=>seg<="00000000";

endcase;

endprocess;

小结

作业布置:

备注:

湖南涉外经济学院教案(14)

授课章节

实验七QuartusII的使用-60进制计数器

课时安排

2

教学目的要求

掌握60进制计数器的VHDL设计。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.源代码

核心进程

process(CLK)

begin

if(CLK’eventandCLK=’1’)then

if(Q=”01100000”)thenQ<=”00000000”;

elsif(Q(3downto0)=”1001”)thenQ<=Q+7;

elseQ<=Q+1;

endif;

endprocess;

小结

作业布置:

备注:

湖南涉外经济学院教案(16)

授课章节

实验八LED动态扫描电路的设计

课时安排

2

教学目的要求

掌握LED动态扫描电路的VHDL设计。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.源代码

核心进程

process(clk2)

begin

ifclk2'eventandclk2='1'then

--clk500<=notclk500;

ifcount<5then

count<=count+1;

else

count<="000";

endif;

endif;

endprocess;

ledw<=count;

knum<=s1(3downto0)whencount=0else

s1(7downto4)whencount=1else

m1(3downto0)whencount=2else

m1(7downto4)whencount=3else

h1(3downto0)whencount=4else

h1(7downto4);

ledd<="00111111"whenknum=0else

"00000110"whenknum=1else

"01011011"whenknum=2else

"01001111"whenknum=3else

"01100110"whenknum=4else

"01101101"whenknum=5else

"01111101"whenknum=6else

"00000111"whenknum=7else

"01111111"whenknum=8else

"01101111"whenknum=9else

"01110111"whenknum=10else

"01111100"whenknum=11else

"00111001"whenknum=12else

"01011110"whenknum=13else

"01111001"whenknum=14else

"01110001"whenknum=15else

"00000000";

小结

作业布置:

备注:

湖南涉外经济学院教案(18)

授课章节

实验九4位加法器的设计

课时安排

2

教学目的要求

掌握4位加法器的EDA实现。

教学重点难点

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.源代码

底层程序

--一位全加器

libraryieee;

useieee.std_logic_1164.all;

entityadderis--实体说明

port(A:

instd_logic;--定义输入即加数

B:

instd_logic;

Cin:

instd_logic;--低位进位信号输入

Co:

outstd_logic;--进位输出

S:

outstd_logic);--和输出

endadder;

architecturehavofadderis--结构体说明

signaltmp1,tmp2:

std_logic;

begin--全加器逻辑描述

tmp1<=AxorB;

tmp2<=tmp1andCin;

S<=tmp1xorCin;

Co<=tmp2or(AandB);

endhav;

顶层程序

--多位加法器

libraryieee;

useieee.std_logic_1164.all;

entityadderNis

--generic(n:

integer:

=3);--类属参数说明

port(ADDR:

instd_logic_vector(7downto0);

l:

instd_logic_vector(6downto0);

a:

instd_logic_vector(3downto0);--四位加法器

b:

instd_logic_vector(3downto0);

cin:

instd_logic;--低位进位信号

nco:

outstd_logic;--进位输出

led:

outstd_logic_vector(7downto0);--和

ledw:

outstd_logic_vector(2downto0)

);

endadderN;

architecturehavofadderNis

componentadder--调用元件说明

port(a:

instd_logic;

b:

instd_logic;

cin:

instd_logic;

co:

outstd_logic;

s:

outstd_logic);

endcomponent;

signalcarr:

std_logic_vector(2downto0);

signals:

std_logic_vector(3downto0);

signalco:

std_logic;

begin

nco<=notco;

label1:

--元件例化生成

foriin0to3generate

label2:

if(i=0)generate

adderx:

adderportmap(a(i),b(i),cin,carr(i),s(i));

endgeneratelabel2;

label3:

if(i=3)generate

adderx:

adderportmap(a(i),b(i),carr(i-1),co,s(i));

endgeneratelabel3;

label4:

if((i/=0)and(i/=3))generate

adderx:

adderportmap(a(i),b(i),carr(i-1),carr(i),s(i));

endgeneratelabel4;

endgeneratelabel1;

process(s)

begin

casesis--和译码显示到数码管上

when"0000"=>led<="00111111";ledw<="000";

when"0001"=>led<="00000110";ledw<="000";

when"0010"=>led<="01011011";ledw<="000";

when"0011"=>led<="01001111";ledw<="000";

when"0100"=>led<="01100110";ledw<="000";

when"0101"=>led<="01101101";ledw<="000";

when"0110"=>led<="01111101";ledw<="000";

when"0111"=>led<="00000111";ledw<="000";

when"1000"=>led<="01111111";ledw<="000";

when"1001"=>led<="01101111";ledw<="000";

when"1010"=>led<="01110111";ledw<="000";

when"1011"=>led<="01111100";ledw<="000";

when"1100"=>led<="00111001";ledw<="000";

when"1101"=>led<="01011110";ledw<="000";

when"1110"=>led<="01111001";ledw<="000";

when"1111"=>led<="01110001";ledw<="000";

whenothers=>led<="00000000";ledw<="000";

endcase;

endprocess;

endhav;

小结

作业布置:

备注:

湖南涉外经济学院教案(20)

授课章节

实验十电子钟设计

课时安排

2

教学目的要求

掌握电子钟的VHDL设计。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]:

1.源代码

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

entitytclkis

port(addr:

instd_logic_vector(7downto0);

clk1,clk2:

instd_logic;--CLK1为1Hz,CLK2为1KHz

ms1,ms2,ms3:

instd_logic;--ms1,ms2为调时调分键,ms3为调时调分使能键

ledw:

outstd_logic_vector(2downto0);

ledd:

outstd_logic_vector(7downto0);--显示输出

alarm:

outstd_logic--蜂鸣器

);

endtclk;

architecturehavoftclkis

signalh1,m1,s1:

std_logic_vector(7downto0);

signalknum:

std_logic_vector(3downto0);

signalcount:

std_logic_vector(2downto0);

begin

process(clk1)

begin

if(clk1'eventandclk1='1')then

if(ms3='1')then--ms=1时计数

if(h1="00100011"andm1="01011001"ands1="01011001")then--23:

59:

59时变为00:

00:

00

h1<="00000000";m1<="00000000";s1<="00000000";

elsif(h1="000010001"andm1="01011001"ands1="01011001")then--9:

59:

59时小时加7为10:

00:

00

h1<=h1+7;m1<="00000000";s1<="00000000";

elsif(m1="01011001"ands1="01011001")then--*:

59:

59时小时加1,分秒变为0

h1<=h1+1;m1<="00000000";s1<="00000000";

elsif(m1="00001001"ands1="01011001")then--*:

9:

59时分加7变为*:

10:

00

m1<=m1+7;s1<="00000000";

elsif(s1="01011001")then--59秒时分加1秒为0

m1<=m1+1;s1<="00000000";

elsif(s1(3downto0)="1001")then--秒加1

s1<=s1+7;

elses1<=s1+1;

endif;

elsif(ms1='0')then--当ms3=0,ms1=0时调时

if(h1="00100011")then

h1<="00000000";

elsif(h1(3downto0)="1001")then

h1<=h1+7;

elseh1<=h1+1;

endif;

elsif(ms2='0')then--当ms3=0,ms2=0时调分

if(m1="01011001")then

m1<="00000000";

elsif(m1(3downto0)="1001")thenm1<=m1+7;

elsem1<=m1+1;

endif;

endif;

endif;

endprocess;

process(clk2)

begin

ifclk2'eventandclk2='1'then

--clk500<=notclk500;

ifcount<5thencount<=count+1;

elsecount<="000";

endif;

endif;

endprocess;

ledw<=count;

knum<=s1(3downto0)whencount=0else

s1(7downto4)whencount=1else

m1(3downto0)whencount=2else

m1(7downto4)whencount=3else

h1(3downto0)whencount=4else

h1(7downto4);

ledd<="00111111"whenknum=0else

"00000110"whenknum=1else

"01011011"whenknum=2else

"01001111"whenknum=3else

"01100110"whenknum=4else

"01101101"whenknum=5else

"01111101"whenknum=6else

"00000111"whenknum=7else

"01111111"whenknum=8else

"01101111"whenknum=9else

"01110111"whenknum=10else

"01111100"whenknum=11else

"00111001"whenknum=12else

"01011110"whenknum=13else

"01111001"whenknum=14else

"01110001"whenknum=15else

"00000000";

alarm<=count

(1)whenm1="01011001"ands1(7downto4)="0101"else--整点报时

count(0)whenm1="00000000"ands1="00000000"else'0';

endhav;

小结

作业布置:

备注:

湖南涉外经济学院教案(22)

授课章节

实验十一键盘扫描电路设计

课时安排

2

教学目的要求

掌握键盘扫描电路的VHDL设计。

教学重点难点

文本输入方式。

教学内容及时间安排

方法及手段

[组织教学]:

[复习旧课]:

[讲授新课]: