已看ISE指导韩芸推荐.docx

《已看ISE指导韩芸推荐.docx》由会员分享,可在线阅读,更多相关《已看ISE指导韩芸推荐.docx(34页珍藏版)》请在冰豆网上搜索。

已看ISE指导韩芸推荐

ISE的使用说明

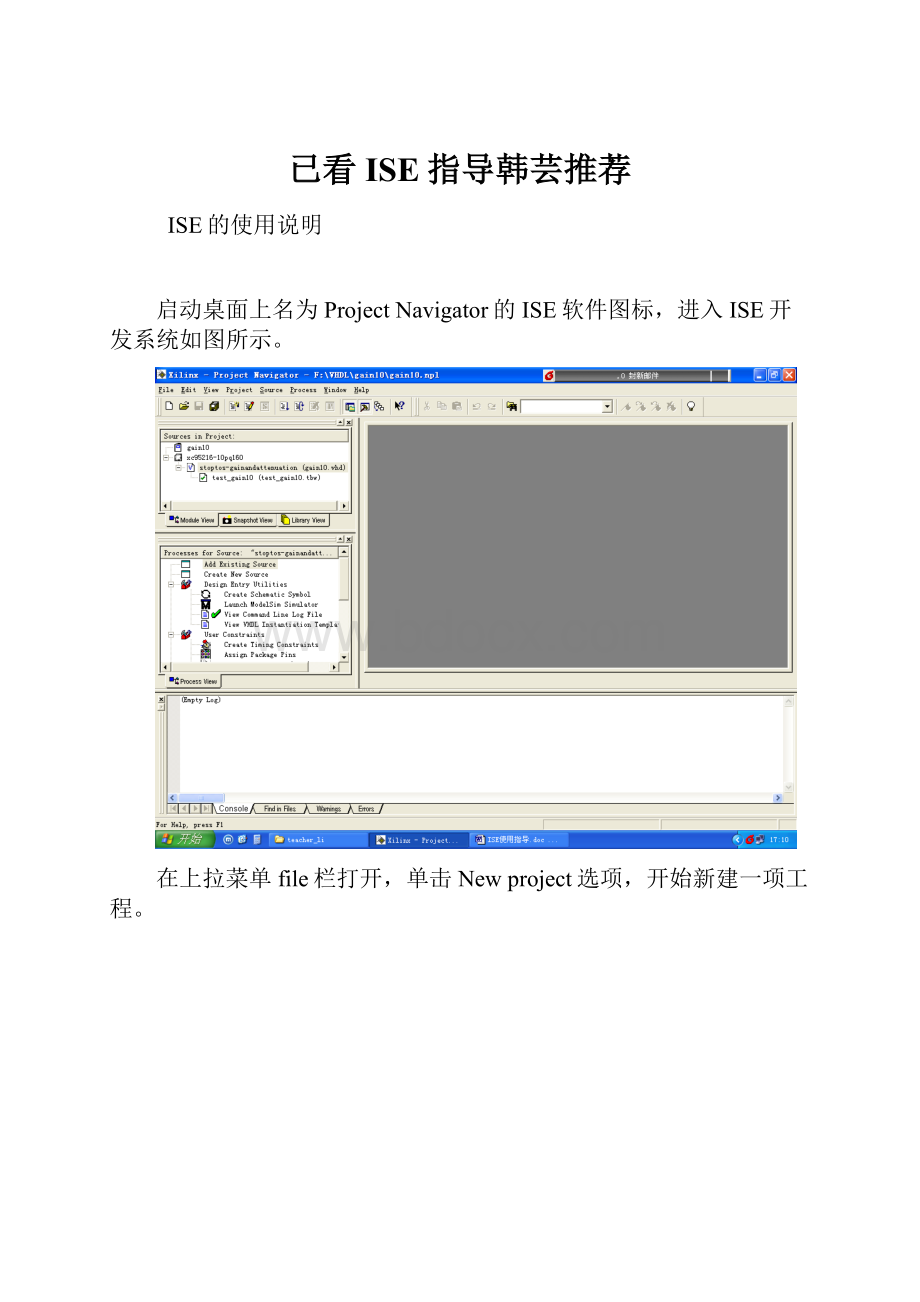

启动桌面上名为ProjectNavigator的ISE软件图标,进入ISE开发系统如图所示。

在上拉菜单file栏打开,单击Newproject选项,开始新建一项工程。

如果想打开已有的ISE工程文件(文件格式为*.npl),则单击openproject选项。

下面我们将以一个包括了24进制和60进制计数器的复合计数器的VHDL程序为例,来说明ISE的具体使用。

首先单击Newproject选项,出现如图所示对话框:

在Projectname一栏填上工程文件名,我们在此工程名命名为counter,放在目录F:

\teacher_li下。

下一步,进行可编程器件型号的选择以及设计流程的设置。

在器件型号栏有Devicefamily,Device(型号),封装,speedgrade,可以根据实验平台所用的可编程逻辑器件分别设置相应选项。

对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了NewProjectInformation的设置。

如图所示:

单击“完成”按钮,进入到如下对话框:

在SourceinProject一栏,选择菜单ModuleView选项,在工程名counter的图标位置单击右键,出现如下对话框。

NewProject:

新建一项文件,单击newProject图标,出现的对话框包括了以下选项:

新建IP核,电路设计,状态机,新建测试波形,用户文档,Verilog编写文件,Verilog测试文件,VHDL库,VHDL编写文件,VHDL包,VHDL测试平台。

AddSource:

添加一项已经存在的文件。

本例中,首先选择VHDLModule项,我们filename命名为count。

下一步,进行管脚信号名称,位数和方向的设置。

如下所示:

设置好相关管脚后,下一步:

单击“完成”。

上面对话框就是VHDLModule的编写界面,我们在此文档编写了如下的VHDL代码:

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

--Uncommentthefollowinglinestousethedeclarationsthatare

--providedforinstantiatingXilinxprimitivecomponents.

--libraryUNISIM;

--useUNISIM.VComponents.all;

entitycountis

Port(reset:

instd_logic;

flag:

instd_logic;

clk:

instd_logic;

counter:

outstd_logic_vector(5downto0));

endcount;

architectureBehavioralofcountis

signalcount:

std_logic_vector(5downto0);

signalflag1:

std_logic;

begin

counter<=count;

process(reset,clk)

begin

ifreset='1'then

count<="000000";

flag1<='0';

elsifclk'eventandclk='1'then

flag1<=flag;

--flag状态切换时,将计数器清零;

if(flag='0'andflag1='1')or(flag='1'andflag1='0')then

count<="000000";

elsifflag='0'andflag1='0'then--flag='0',则进行24进制计数

ifcount<23then

count<=count+1;

elsifcount>=23then

count<="000000";

endif;

elsifflag='1'andflag1='1'then--flag='1',则进行60进制计数

ifcount<59then

count<=count+1;

elsifcount>=59then

count<="000000";

endif;

endif;

endif;

endprocess;

endBehavioral;

在界面的ProcessesforSource一栏,是一系列综合工具。

SynthesizeXST工具一般可以分析代码的语法错误,查看错误报告和RTL级的电路设计图。

单击ViewSynthesis,出现如图所示对话框:

单击ViewRTLSchemetic:

双击设计原理图,功能模块示意图:

在双击某一功能模块,可以得到RTL级的电路:

用XST工具综合分析无误后,在工程名counter图标处单击右键,在弹出的对话框选择管脚约束文件ImplementationConstraintsFile选项,我们将该文件命名为counter_pin。

下一步,出现如下对话框:

单击“完成”,我们可以看到在名为counter的工程图标下多了一个名为counter_pin.ucf的图标,这就是我们刚才新建的管脚约束文件。

双击图标“counter_pin.ucf”,进入芯片管脚锁定界面:

在界面左半部分的DesignObjectList-I/OPins栏进行管脚约束。

在本例中,我们采用的芯片型号是Spartan-IIlXC2S200,封装pq208,对照该芯片对管脚的说明,

也可以在EditConstraints(text)文件夹按照如下格式书写管脚约束文件:

#PACE:

StartofConstraintsgeneratedbyPACE

#PACE:

StartofPACEI/OPinAssignments

NET"clk"LOC="p77";

NET"counter<0>"LOC="p57";

NET"counter<1>"LOC="p58";

NET"counter<2>"LOC="p59";

NET"counter<3>"LOC="p60";

NET"counter<4>"LOC="p61";

NET"counter<5>"LOC="p62";

NET"flag"LOC="p63";

NET"reset"LOC="p67";

#PACE:

StartofPACEAreaConstraints

#PACE:

StartofPACEProhibitConstraints

#PACE:

EndofConstraintsgeneratedbyPACE

然后单击工程counter下的子目录count-Behavioral(count.vhd),接着在界面的ProcessesforSource一栏选择ImplementDesign,进行布局布线的综合:

然后工程名counter上单击右键,弹出对话框,选择新建TestBenchWaveform,在file命名为test_counter。

然后下一步,默认设置,直到完成。

出现如下对话框:

在本例中,选择20MHZ时钟作为系统单一的主时钟,上升沿触发有效。

完成时钟的设置后,进入如下对话框,可以设置相关输入信号(时钟信号除外)的状态:

设置好仿真波形test_counter.tbw后,记住保存。

然后单击工程目录下的子目录test_counter(test_counter.tbw),在ProcessesforSourc出现仿真的一系列流程。

按照从上到下的顺序依次进行行为级仿真,布线前仿真,布线后仿真。

首先我们进行行为级仿真,双击simulatebehavioralmodel,

出现如下对话框:

查看wave-default:

如果想查看中间信号的仿真波形,可以打开Structure文件,在uut一栏添加Dataflow,

然后就看到中间信号的仿真波形了:

如法炮制,我们接着可以按部就班地进行后面几步仿真。

全部仿真都通过的话,就可以进行程序的下载和可编程芯片的实际测试了。

下载流程

下载过程使用的软件为:

Xilinx公司开发平台ISE6.1i(或者5.1i以及更高版本均可),硬件为Xilinx公司的并口或串口下载线(由下载线出来的跟接口板相连的线必须是分开的)。

连好线后,将接口板通上电源,然后运行软件ISE6.1i的组件iMPACT,软件自动进入OperationModeSelection界面,此时选择ConfigurationDevices(缺省的也是该项),点击下一步;接着进入ConfigureDevices界面,此界面选择Boundary-ScanMode(缺省的也是该项),点击下一步;接着进入Boundary-ScanModeSelection界面,此时选择AutomaticallyconnecttocableandidentifyBoundary-Scanchain(缺省的也是该项),然后点击完成;软件会自动搜索到两个器件。

为左面的器件分配下载文件,然后下载即可完成下载任务。

1.流程图

2.各阶段详细叙述

(1)连接下载线:

接口板上跟每个下载芯片PromXc18v02有对应的6个单排插针,插针从左到右功能依次为:

TDI,DMS.TCK.TDO,VCC,GND,将对应的下载线插到插针上即可。

(2)接口板上电:

给接口板加上+5V电源,方法可以是从+5V和GND的测试口分别引出线,然后接到外部电源上。

(3)运行ISE,具体步骤如下:

Ø打开ISE组件iMPACT,如图

Ø然后软件自动进入OperationModeSelection界面,此时选择ConfigurationDevices(缺省的也是该项),点击下一步。

如图

接着进入ConfigureDevices界面,此界面选择Boundary-ScanMode(缺省的也是该项),点击下一步。

如图

Ø接着进入Boundary-ScanModeSelection界面,此时选择AutomaticallyconnecttocableandidentifyBoundary-Scanchain(缺省的也是该项),然后点击完成

(4)为芯片分配配置文件:

进入配置文件分配界面,如图所示,

(5)点击确定。

然后在左面的芯片图标上点鼠标右键。

弹出菜单,然后点击AssignNewConfigurationFile…如下图所示。

找到对应的下载文件,选中后打开(这里以IC7的下载文件IC7.EXO为例),如下图图所示。

(6)下载:

在刚分配完下载文件的芯片(左面的芯片)上点鼠标右键,然后在弹出的菜单上点击Program….如下图。

(7)然后弹出新窗口,在新窗口中点击OK,如下图所示:

之后软件开始往芯片里面下载文件,窗口如下图所示,图中的蓝色条应该在往前走动。

(8)是否下载成功:

若上图的蓝色条走到头,然后在窗口里出现字样“Programmingsucceeded.就说明下载成功了。

如图所示:

若出现红色的ProgrammingFailed,则需要重新在芯片上点右键选择Program…重新下载,直到下载成功。