CD4013中文资料.docx

《CD4013中文资料.docx》由会员分享,可在线阅读,更多相关《CD4013中文资料.docx(15页珍藏版)》请在冰豆网上搜索。

CD4013中文资料

CD4013:

双D触发器中文资料

CD4013由两个相同的、相互独立的数据型触发器构成。

每个触发器有独立的数据、置位、复位、时钟输入和Q及Q输出,此器件可用作移位寄存器,且通过将Q输出连接到数据输入,可用作计算器和触发器。

在时钟上升沿触发时,加在D输入端的逻辑电平传送到Q输出端。

置位和复位与时钟无关,而分别由置位或复位线上的高电平完成。

838电子 新艺图库

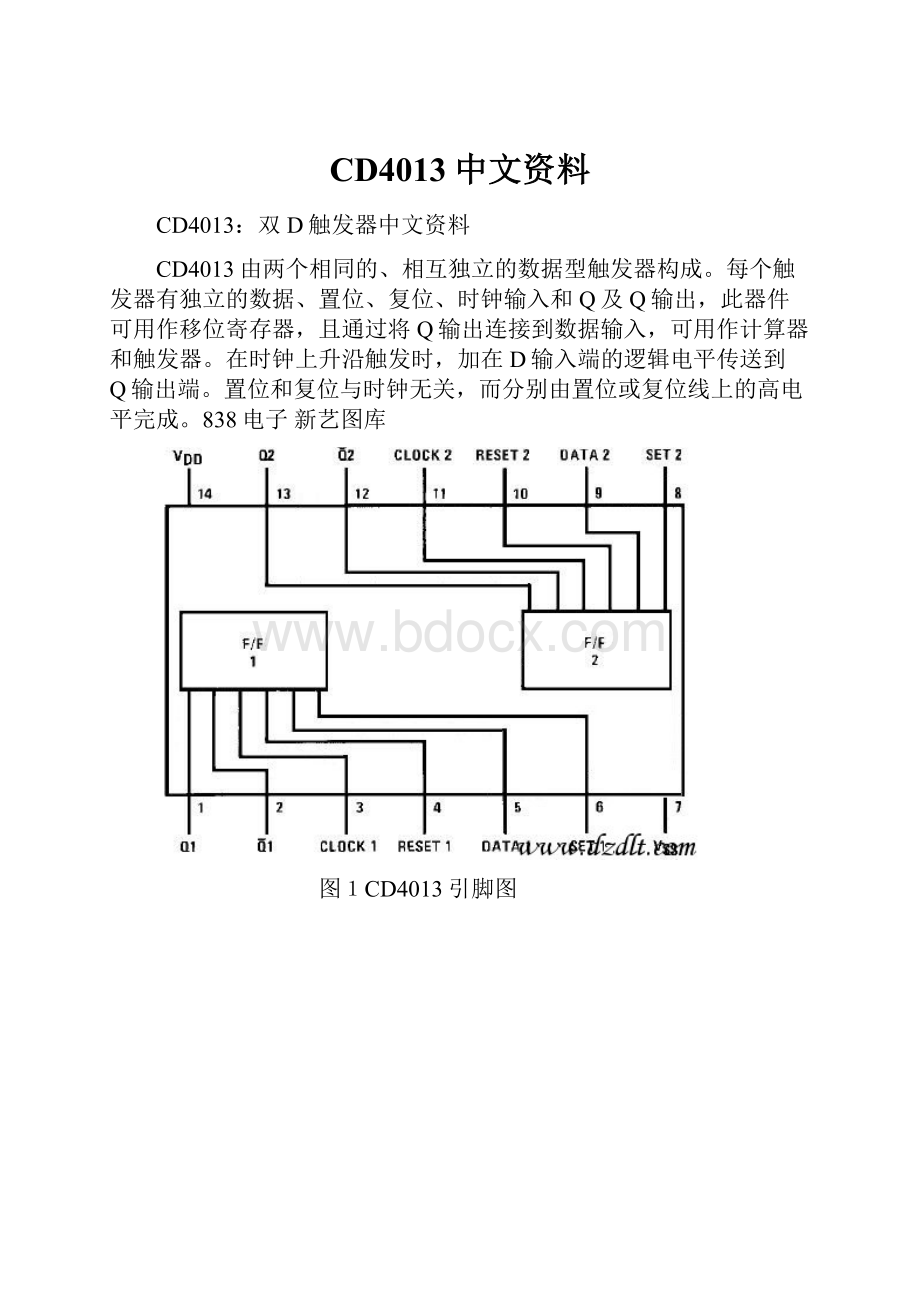

图1CD4013引脚图

图2 CD4013内部电路图

图3CD4013逻辑图

TruthTable真值表功能:

Symbol符号

Parameter参数

Conditions条件

-40℃

+25℃

+85℃

Units单位

最小

最大

最小

典型

最大

最小

最大

IDD

QuiescentDeviceCurrent静态电流

VDD=5V,VIN=VDDorVSS

4.0

4.0

30

μA

VDD=10V,VIN=VDDorVSS

8.0

8.0

60

VDD=15V,VIN=VDDorVSS

16.0

16.0

120

VOL

LOWLevelOutputVoltage低电平输出电压

|IO|<1.0μA

VDD=5V

0.05

0.05

0.05

V

VDD=10V

0.05

0.05

0.05

VDD=15V

0.05

0.05

0.05

VOH

HIGHLevelOutputVoltage输出高电平电压

|IO|<1.0μA

VDD=5V

4.95

4.95

4.95

V

VDD=10V

9.95

9.95

9.95

VDD=15V

14.95

14.95

14.95

VIL

LOWLevelInputVoltage输入低电平电压

|IO|<1.0μA

VDD=5V,VO=0.5Vor4.5V

1.5

1.5

1.5

V

VDD=10V,VO=1.0Vor9.0V

3.0

3.0

3.0

VDD=15V,VO=1.5Vor13.5V

4.0

4.0

4.0

VIH

HIGHLevelInputVoltage输入高电平电压

|IO|<1.0μA

VDD=5V,VO=0.5Vor4.5V

3.5

3.5

3.5

V

VDD=10V,VO=1.0Vor9.0V

7.0

7.0

7.0

VDD=15V,VO=1.5Vor13.5V

11.0

11.0

11.0

IOL

LOWLevelOutputCurrent输出低电平电流(Note4)

VDD=5V,VO=0.4V

0.52

0.44

0.88

0.36

mA

VDD=10V,VO=0.5V

1.3

1.1

2.25

0.9

VDD=15V,VO=1.5V

3.6

3.0

8.8

2.4

IOH

HIGHLevelOutputCurrent输出高电平电流(Note4)

VDD=5V,VO=4.6V

-0.52

-0.44

-0.88

-0.36

mA

VDD=10V,VO=9.5V

-1.3

-1.1

-2.25

-0.9

VDD=15V,VO=13.5V

-3.6

-3.0

-8.8

-2.4

IIN

InputCurrent输入电流

VDD=15V,VIN=0VVDD=15V,VIN=15V

-0.30.3

-10-510-5

-0.30.3

-1.01.0

μA

CL(Note1)

D

R

S

Q

Q

↑

0

0

0

0

1

↑

1

0

0

1

0

↓

x

0

0

Q

Q

x

x

1

0

0

1

x

x

0

1

1

0

x

x

1

1

1

1

AbsoluteMaximumRatings绝对最大额定值:

DCSupplyVoltage直流供电电压(VDD)

-0.5VDCto+18VDC

InputVoltage输入电压(VIN)

-0.5VDCtoVDD+0.5VDC

StorageTemperatureRange储存温度范围(TS)

-65℃to+150℃

PowerDissipation功耗(PD)

Dual-In-Line普通双列封装

700mW

SmallOutline小外形封装

500mW

LeadTemperature(TL)(Soldering,10seconds)焊接温度

260℃

RecommendedOperatingConditions建议操作条件:

DCSupplyVoltage直流供电电压(VDD)

+3VDCto+15VDC

InputVoltage输入电压(VIN)

0VDCtoVDDVDC

OperatingTemperatureRange工作温度范围(TA)

-40℃to+85℃

DCElectricalCharacteristics直流电气特性:

ACElectricalCharacteristics交流电气特性:

65 120

tTHL,tTLH

TransitionTime过渡时间

VDD=5V

100 200 ns

VDD=10V

50 100

VDD=15V

40 80

tWL,tWH

MinimumClockPulseWidth最小时钟脉冲宽度

VDD=5V

100 200 ns

VDD=10V

40 80

VDD=15V

32 65

tRCL,tFCL

MaximumClockRiseandFallTime最大时钟上升和下降时间

VDD=5V

15 msVDD=10V 10VDD=15V 5

tSU

MinimumSet-UpTime最低设置时间

VDD=5V

20 40 ns

VDD=10V

15 30

VDD=15V

12 25

fCL

MaximumClockFrequency最大时钟频率

VDD=5V

2.5 5 MHz

VDD=10V

6.2 12.5

VDD=15V

7.6 15.5

SETANDRESETOPERATIONSET和复位操作

tPHL(R),tPLH(S)

PropagationDelayTime传递延迟时间

VDD=5V

150 300 ns VDD=10V 45130 VDD=15V 6590

tWH(R),tWH(S)

MinimumSetandResetPulseWidth最低限度和复位脉冲宽度

VDD=5V

90 180 nsVDD=10V 40 80VDD=15V 2550

CIN

AverageInputCapacitance平均输入电容

AnyInput

5 7.5 pF

图4切换时间波形

应用电路:

置位和复位电路

图5(左)和图(右)中的CD4013是CMOS双D触发器,这类电路置位和复位信号是高电平有效,由于开关闭合时电容可视为短路而产生高电平,使RD=1,Q=0;若将此信号加到SD,则SD=1,Q=1;置位、复位过后,电容充电而使RD(SD)变为0,电路可进入计数状态。

图5

cd4013

百科名片

在电子技术中,N/2(N为奇数)分频电路有着重要的应用,对一个特定的输入频率,要经N/2分频后才能得到所需要的输出,这就要求电路具有N/2的非整数倍的分频功能。

CD4013是双D触发器,在以CD4013为主组成的若干个二分频电路的基础上,加上异或门等反馈控制,即可很方便地组成N/2分频电路。

结构组成

工作原理

N/2分频电路

特性

编辑本段

结构组成

图1是3/2分频电路。

IC1、IC2均接成二分频器,所以该电路是由四分频电路与反馈控制电路组成,计数脉冲由异或门F1输出。

fi既作为分频信号又作为时钟脉冲接入异或门的一个输入端,从四分频电路的IC2的Q2输出端引出反馈信号作F1的另一输入端。

输出信号fo从IC1的Q1端输出。

图2是其工作波形。

编辑本段

工作原理

设电路初始状态均在复位状态,Q1、Q2端均为低电平。

当fi信号输入时,由于输入端异或门的作用(附表是异或门逻辑功能表),其输出还受到触发器IC2的Q2端的反馈控制(非门F2是增加的一级延迟门,A点波形与Q2相同)。

在第1个fi时钟脉冲的上升沿作用下,触发器IC1、IC2均翻转。

由于Q2端的反馈作用使得异或门输出一个很窄的正脉冲,宽度由两级D触发器和反相门的延时决定。

当第1个fi脉冲下跳时,异或门输出又立即上跳,使IC1触发器再次翻转,而IC2触发器状态不变。

这样在第1个输入时钟的半个周期内促使IC1触发器的时钟脉冲端CL1有一个完整周期的输入,但在以后的一个输入时钟的作用下,由于IC2触发器的Q2端为高电平,IC1触发器的时钟输入跟随fi信号(反相或同相)。

本来IC1触发器输入两个完整的输入脉冲便可输出一个完整周期的脉冲,现在由于异或门及IC2触发器Q2端的反馈控制作用,在第1个fi脉冲的作用下得到一个周期的脉冲输出,所以实现了每输入一个半时钟脉冲,在IC1触发器的Q1端取得一个完整周期的输出。

编辑本段

N/2分频电路

图3是5/2分频电路。

IC1、IC2、IC3三级D触发器级联为8分频电路,电容C起滤波作用,输出信号fo从IC2的Q2端输出。

电路中有Q1、Q3两个反馈控制。

从图4工作波形可知,Q1的反馈信号中每两个反馈信号中就有一个受到Q3反馈波形的影响,所以在A点仅能形成几百毫微秒宽的脉冲。

由于电容C的作用,Q1的反馈信号(即一窄脉冲)被滤除掉,如图4波形A的虚线所示。

最后在Q2端输出fo信号。

fo每变化一个周期,对应于输入信号fi的两个半周期,即fo的频率为fi的2/5。

图5是7/2分频电路。

该电路与图3相似,区别在于电路中一个反馈信号在图3中是从Q1端引出的,而图5是从Q2端引出的,fo信号从Q2端输出。

电路有Q2、Q3两级反馈,由于Q2反馈信号受Q3反馈的影响,在A点仅能形成几百毫微秒宽的窄脉冲,此窄脉冲被电容C滤除掉,因此Q2反馈不起作用,电路实际上只有一个Q3反馈,因而使得fo输出信号每变化一个周期,对应于fi输入信号的三个半周期,即fo的频率为fi的2/7。

其工作波形如图6所示。

上面介绍的N/2分频电路仅限于N≤7,当N≥7时,可根据分频N值的大小,相应增加二分频级数,并恰当引接反馈信号走线,便可得到N≥7的分频电路。

下面仅介绍一例9/2分频电路,如图7所示。

图8是其工作波形。

IC1~IC4四级D触发器组成16分频电路,fo信号从Q3输出,电路有Q1、Q4两级反馈。

其工作原理与上述有关分频电路相似,波形图上A点虚线脉冲表示为电容C滤除掉的Q1反馈信号。

从图8中可知,只要fi输入四个半周期的时钟信号,就输出一个周期信号fo,即fo的频率为fi的2/9。

编辑本段

特性

从以上几个N/2分频电路可得到如下几个特性:

1.电路工作原理是,在第n个周期,末级两分频器的输出为高电平时,输入时钟脉冲的上升沿使分频电路工作;在第n+1个周期,末级两分频器的输出为低电平时,输入时钟脉冲的下降沿使分频电路工作。

2.电路采用的是异步触发形式,各触发器的初始状态不会影响到分频的功能。

如果要求初始状态为“0”状态,可以将D触发器的复位端R引出,接至复位控制电路。

3.输入信号fi的最高工作频率fimax除受到CMOS元件fM的限制外,还受到D触发器、反馈门翻转延迟和电容C滤波频率特性的影响,所以应尽可能提高fi的值。

一般情况下,最高工作频率fimax在几百千赫以下。

▲用CD4013双D触发器做的脉冲4分频器

-----------------------------

. ┌─────────────┐ .

. │ ┌─────┐ │ .

. │ ┏━━━┻━━━┓ │ │ .

. │ ┃ R ┃ │ │ .

. └─┫D Q┣─┼─┼─┐ .

. ┃ ┃ │ │ │ .

.[CP>───┫CP -Q┣─┼─┘ │ .

. ┃ S ┃ │ │ .

. ┗━━━┳━━━┛ │ │ .

. └─────● │ .

. │ │ .

. 用CD4013双D触发器 ┷ │ .

. 做脉冲4分频电路。

GND │ .

. §文本逻辑电路图№1§ │ .

. ┌────────────────┘ .

. │┌─────────────┐ .

. ││ ┌─────┐ │ .

. ││ ┏━━━┻━━━┓ │ │ .

. ││ ┃ R ┃ │ │ .

. │└─┫D Q┣─┼─┼─[CP/4> .

. │ ┃ ┃ │ │ .

. └──┫CP -Q┣─┼─┘ .

. ┃ S ┃ │ ┌────┐ .

. ┗━━━┳━━━┛ │ │版权没有│ .

. └─────● │欢迎翻版│ .

. 中国家电维修联盟成员 │ │无限拷贝│ .

. 杨真人 制作 ┷ │请勿涂改│ .

. 2001.10.18 GND └────┘