cpu工作 原理.docx

《cpu工作 原理.docx》由会员分享,可在线阅读,更多相关《cpu工作 原理.docx(28页珍藏版)》请在冰豆网上搜索。

cpu工作原理

一.CPU动作讲解

IC:

8088/80286

一.概论:

CentralityProcessorUnit—中央处理单元

1.CPU:

中央系统单元是整个系统的核心,是整个系统的最高执行单位,负责整个系统资料的处理,执行,控制,运算的功能,整个系统资料处理速度的快慢,取决于CPU的工作频率.

2.CPU内含CU&ALU二部分

CU:

ControlUnit负责控制指挥协调CPU内外各单元之执行,暂存,堆叠,运算,解码,交换,为电脑的控制中心.

ALU:

Arithmetic&Logicalunit执行算术及逻辑运算.

3.利用内容之ALU(Arithmetic&Logicalunit)算术/逻辑单元处理送进来资料,包含算术处理(加.减.乘.除)与逻辑运算(比较.AND.OR.NOR),并将处理后之资料由控制单元(ControlUnit)送至主记忆体或外部存放.

4.为加速ALU执行速度,CPU使用了一特定的高速暂存器,用以暂时存放待处理或已处理资料,以加快CPU处理速度.

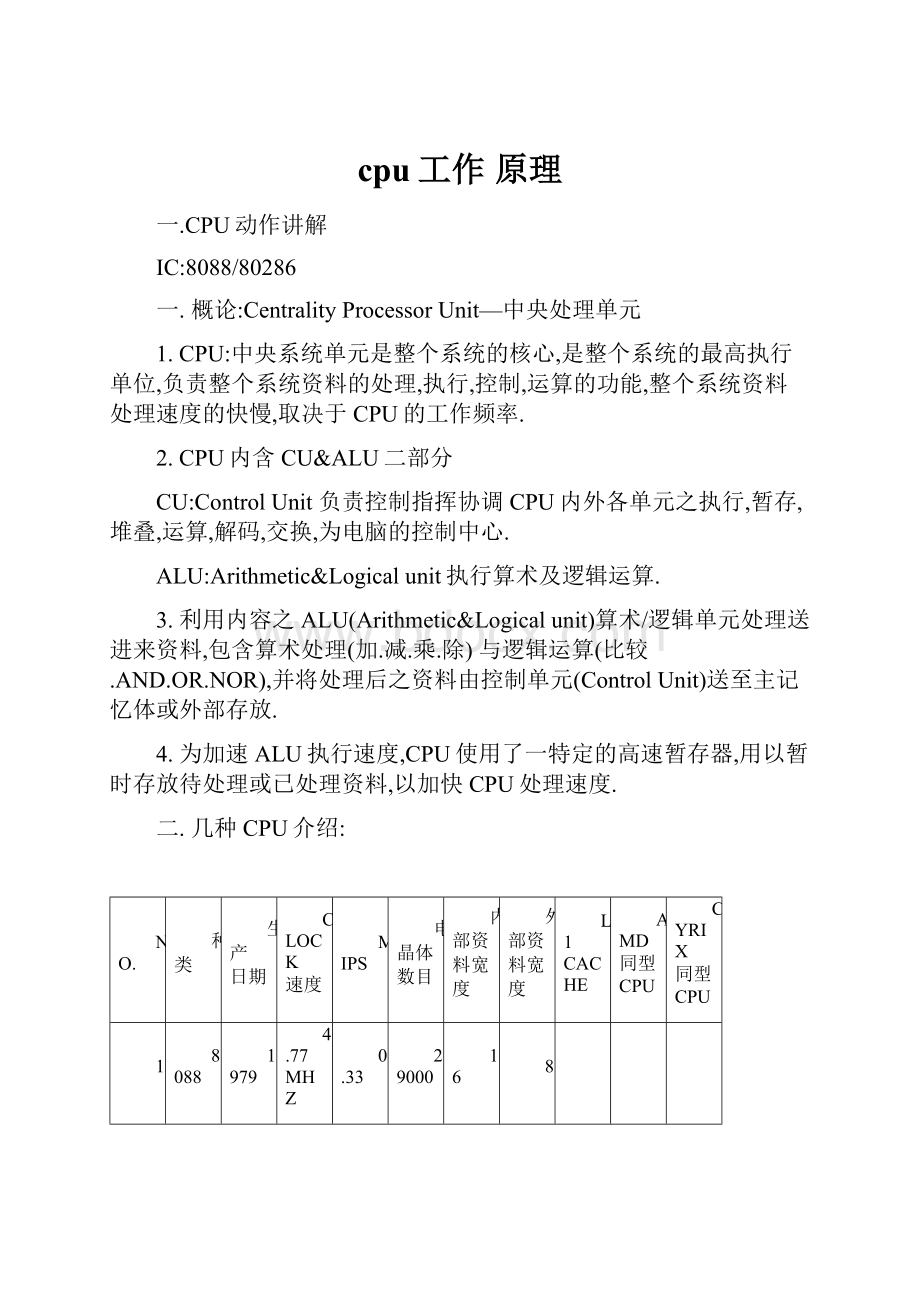

二.几种CPU介绍:

NO.

种类

生产

日期

CLOCK

速度

MIPS

电晶体

数目

内部资

料宽度

外部资

料宽度

L1

CACHE

AMD

同型CPU

CYRIX

同型CPU

1

8088

1979

4.77MHZ

0.33

29000

16

8

2

80286

1982

8-20MHZ

1.2

134000

16

16

3

80386DX

1985

25-33MHZ

6

275000

32

16

386-40

4

80486DX

1989

33-100MHZ

20

1.2M

32

32

5K86-133

5

80486DX2

1992

33-100MHZ

40

1.2M

32

32

8-16KB

6

Pentium1

1993

60-266MHZ

112

3.1M

64

32

16KB

K5

6x86

7

PentiumMMX

1996

166-266MHZ

64

32

32KB

K6

6x86mx

8

PentiumII

1996

233-455MHZ

64

64

32KB

K6-11

9

Celeron

10

PentiumIII

1999

450-750MHZ

9.6M

64

64

64KB

K6-111

Athlon

VIA

Cyrix

III

11

Coppermine

1999

500_733MHZ

2.8M

64

64

在80486以后CPU增加三项技术1.采取内,外频技术,亦就是每一CPU有其倍频系数.

内频(主频)=外频*倍频系数.

2.将Co-Processor包含入CPU中,以增加运行速度.

3.增加CacheRAM(称L1Cache)以作高速运作时暂作资料摆放

种类

主频

外频

倍频

电压

L1

CACHE

L2

CACHE

架构

1

Pentium166MMX

166MHZ

66MHZ

2.5

2.8V

32KB

256KB

SOCKET7

2

Pentium200MMX

200MHZ

66MHZ

3

2.8V

32KB

256KB

SOCKET7

3

Pentium233MMX

233MHZ

66MHZ

3.5

2.8V

32KB

256KB

SOCKET7

4

Pentium266MMX

266MHZ

66MHZ

4

2.8V

32KB

256KB

SOCKET7

5

6

PentiumII233

233MHZ

66MHZ

3.5

2.0V

32KB

512KB

SLOT1

7

PentiumII266

266MHZ

66MHZ

4

2.0V

32KB

512KB

SLOT1

8

PentiumII300

300MHZ

66MHZ

4.5

2.0V

32KB

512KB

SLOT1

9

PentiumII333

333MHZ

66MHZ

5

2.0V

32KB

512KB

SLOT1

10

PentiumII350

350MHZ

100MHZ

3.5

2.0V

32KB

512KB

SLOT1

11

PentiumII400

400MHZ

100MHZ

4

2.0V

32KB

512KB

SLOT1

12

PentiumII450

450MHZ

100MHZ

4.5

2.0V

32KB

512KB

SLOT1

13

14

Celeron300A

300MHZ

66MHZ

4.5

2.0V

32KB

128KB

SOCKET370

15

Celeron333

333MHZ

66MHZ

5

2.0V

32KB

128KB

SOCKET370

16

Celeron366

366MHZ

66MHZ

5.5

2.0V

32KB

128KB

SOCKET370

17

Celeron400

400MHZ

66MHZ

6

2.0V

32KB

128KB

SOCKET370

18

Celeron433

433MHZ

66MHZ

6.5

2.0V

32KB

128KB

SOCKET370

19

Celeron466

466MHZ

66MHZ

7

2.0V

32KB

128KB

SOCKET370

20

Celeron533

533MHZ

66MHZ

8

2.0V

32KB

128KB

SOCKET370

21

22

PentiumIII450

450MHZ

100MHZ

4.5

2.0V

64KB

512KB

SLOT1

23

PentiumIII500

500MHZ

100MHZ

5

2.0V

64KB

512KB

SLOT1

24

PentiumIII550

550MHZ

100MHZ

5.5

2.0V

64KB

512KB

SLOT1

25

PentiumIII600

600MHZ

100MHZ

6

2.0V

64KB

512KB

SLOT1

26

PentiumIII650

650MHZ

100MHZ

6.5

2.0V

64KB

512KB

SLOT1

27

PentiumIII750

750MHZ

100MHZ

7

2.0V

64KB

512KB

SLOT1

28

PentiumIII850

850MHZ

29

PentiumIII860

860MHZ

30

PentiumIII1000

1000MHZ

133MHZ

7.5

256KB

31

32

PentiumIIIIXXX

33

34

35

36

二.CO-PROCESSOR动作讲解

典型IC:

8087/80287

基本概念:

CO-Processor—数学运算处理器

由于CPU主要负责逻辑运算,不擅长数学运算,特别制作出一数学运算处理器以辅助之.

动作方式:

1.此一数学运算处理器系专门作数学运算用,内部大大增加算数处理位元与暂存器长度,以提高计算精确度与加快内部资料传递速度

2.此一数学运算处理器与CPU并联使用,当同时工作,数学运算处理器与CPU将自动判定是否为数学运算指令,若为真,则CPU将无法处理,暂时停顿,数学运算处理器将依汇流排要求/同意法则,向CPU要求汇流排控制权并同意后,执行该运算处理指令.

3.当运算处理指令执行完毕后,数学运算处理器将运算结果存入记忆体后自动将汇流排控制权交还给CPU.

4.CPU恢复汇流排控制权与接收数学运算后之值.

最新发展:

486后CPU以将CO-Processor制作加入CPU中,以加快整体运作速度.

CLK动作讲解

典型IC:

8284A

基本概念:

ClockGeneratorct—时脉产生器

产生各系统元件所需之时脉,及各系统间之同步讯号,是各元件运作的动力.为使CPU有一稳定时脉(CLOCK)与备妥(READT)同步讯号与重置(RESET)逻辑,特别制作出单一时脉产生器IC,以简化线路并提长系统稳定度.

动作方式:

1.8284A外接受能力4.318MHZ石英振荡器本身作除频动作.分别以1/3频(4.7MHZ)33%DutyCycle提供给CPU,及1/6频(2.386MHZ)50%DutyCycle给周边装置.

2.8284A外接一POWERGOOD讯号并同步CLOCK记号以送出RESET讯号.

三.BUSCTRL动作讲解

典型IC:

8288

基本概念:

BUSController---汇流排控制器

接受CPU的命令,执行CPU所要传送的各种控制信号,如位址控制信号(ALE),资料控制信号(DEN),资料方向控制信号(DT/R)以及代替CPU下达各种命令,如对记忆体下达读写命令(MEMR,MEMW)对I/O下达读命令(-IOR,-IOW),对中断控制器(8259)下达INTA命令等,它也是一个执行单位为使控制讯号输出精确特别制作出单一汇流排控制IC,以将CPU的命令转换为适切控制讯号以供汇流排控制所需.

动作方式:

1.8288外接CPU产生/SO,/S1,/S2讯号并配合CLK,/KEN,CEN,IOB讯号输入,以产生以下控制讯号.

2.命令输出接脚功能:

/MRDC,/MWTC,/AMWC,/IORC,/IORC,/IOWC,

3.控制讯号输出接脚:

DT/R,DEN,ALE,MCE/PDEN

名词解释:

CLK=CPU时脉(CLOCK)

/AEN=位址置能,LOW动作,若输入为HI时,8288输出之接脚皆呈浮动状态.

CEN=类似AEN,HI动作,但输入为LOW时,8288输出之接脚皆不工作状态.(反向ACTION输出)

四-IRQ动作讲解

典型IC:

8259

基本概念:

InterruptIRQ—中断要求与服务

8259是介于CPU与外面各种周边设备沟通的桥梁,当外界的周边设备要请求CPU来处理资料时候必须经过中断控制器8259来通知CPU处理,而且每次只能安排一种周边设备,目前使用的通道有IRQ0-IRQ15共有16种,如软碟,硬碟,键盘,印表机等,这些通道有些是专属的,有的是大家公用的,同时要求处理时,中断控制器还会比大小,权位高的优先,权位低的要让权位高的.由于周边元件(K/B,FDD,MOUSE)并非随时都在工作,CPU若采取轮询法或等待法将造成效率低落,故由周边元件主动提出中断服务要求,CPU再视实际情况服务以提升工作效率.

运作方式:

1.周边元件透过IRQ0-IRQ7(IRQ0权位较高)讯号向中断控制器提出中断服务要求.

2.中断控制器依权位比重判定是否接受要求.

3.中断控制器若接受周边要求,则向CPU送出INT—要求中断服务要求讯号.

4.CPU将视状况(无DMA工作,无不可遮幕中断工作),在下一工作周期结束时送出INTA—中断认可讯号,准备执行中断服务.

5.中断控制器接获INTA讯号后,则向CPU送出中断向量值在资料汇聚排上.

6.CPU接获中断向量值后自动计算出中断服务程式位置,并跳至该位置执行起.

7.执行完中断服务程式后,CPU继续原先未完成之工作.

IRQ分配表一般设定)

IRQ编号

装置名称

主要用途

IRQ-0

Timer

电脑系统计时器专用

IRQ-1

Keyboard

键盘专用

IRQ-2

2nd8259

接收第二个SLAVE8259代表IRQ8-IRQ15所接的周边设备通知CPU

IRQ-3

COM2

设定给数据机

IRQ-4

COM1

设定给滑鼠

IRQ-5

LPT2

设定给音效卡

IRQ-6

FDD

软碟机传输控制专用

IRQ-7

LPT1

印表机传输控制专用

IRQ-8

CMOSAlarm

时钟闹玲

IRQ-9

RedirectIRQ2

与IRQ2相接,可设定给其他介面卡使用

IRQ-10

Reversed

通常设定给网路卡使用

IRQ-11

Reversed

保留或IDE3

IRQ-12

PS/2mouse

连接PS/2mouse使用

IRQ-13

FPU

CO-PROCESSOR使用

IRQ-14

PrimaryIDE

第一组硬式磁碟机传输控制专用

IRQ-14

SecondaryIDE

第二组硬式磁碟机传输控制专用

IRQ优先顺序:

IRQ0->IRQ1->IRQ2->IRQ8->IRQ9->IRQ10->IRQ11->IRQ12->IRQ13->IRQ14->IRQ15->IRQ3->IRQ4->IRQ5->IRQ6->IRQ7

五.DMA动作讲解

典型IC:

8237

基本概念:

DirectMemoryAccessDMA—直接记忆体存取.

由周边元件或记忆体直接对系统之记忆体直接作存入或取出动作而无需透过CPU之运作以提升效率.但是要做DMA的控制以前,必须先获得CPU的同意,整个系统的汇流排控制权交给DMA控制器(8237)来接管.目前作DMA的周边,有软碟,新型IDE界面有ULTRADMA33,ULTRADMA66快速硬碟SCSI硬碟,SCSI光碟,音效卡,印表机等周边设备.

动作方式:

1.由周边元件透过DRQ0-DRQ3(DRQ0权位较高)讯号向DMA控制器提出直接存取记忆体要求.

2.DMA控制器依权位比重判定是否接受要求.(若同时有多个DMA要求或工作时,DMA控制器将依权位比重判定是否接受要求.)

3.DMA控制器若接受周边要求,则向CPU送出IRQ—要求汇流排要求讯号.

4.CPU将在下一工作周期结束时送出HLDA—同意汇流排讯号,并放弃汇流排使用权.

5.DMA控制器向周边元件送出相对应之DACK0-DACK3(DMA要求认可讯号.

6.在DACKx讯号为HI期间,DMA控制器以IOR及IOW对周边元件作资料取出与存入动作,并以MEMR与MEMW对记忆体作存取。

7.DMA动作结束,DMA控制器将HRQ与DACKx讯号拉为LOW,并将汇流排控制权交回。

8.CPU继续原先未完成之工作.

DRQ分配表一般设定)

DRQ1:

音效卡DRQ2:

磁碟机专用DRQ3:

保留

DRQ4:

由第一个8237DMA控制器串接到DRQ.DRQ5:

声霸卡使用

DRQ6:

一般SCSI卡DRQ0:

保留DRQ7:

保留(网路卡/MPEGCARD)

六-RTC动作讲解

典型IC:

146818

基本概念:

RealTimeClock—真时时钟

为使系统可随时知道,日期与时间,特别制作出一即(真)时时钟,以随时作计时工作.该计时电路内含本身使用RTC电池,提供该电路在PC未开机下仍然工作.(PC若在开机下,则对RTC电池进行充电工作,以保持RTC电池之电量.)

运作方式:

1.IC146818使用-32.768MHz振荡器做为其CLOCK来源,计时之值(时,分,秒,年,月,日)存于武之CMOS记忆体内,以供系统作读取之用.

2.使用者可透过”SET-UP”或”DATE”及”TIME”对RTC值作修改.

系统自动开机自我测试无误后,将向RTC调时间,日期资料,配合IRQ-0中断动作,自行再作一CLOCK时钟使用.(配合8253TimerIC产生精确之18MHz频率作计时使用。

七-CMOS动作讲解

典型IC:

146818

基本概念:

CMOS—静态记忆器

CMOSSRAM(静态RAM),它内部有64/128/256BYTE的SRAM,储存我们所设定的周边设备的组态,日期,时间,硬碟的TYPE,磁碟的大小等重要的资料,其他有BIOS的设定,晶片组的设定,电源管理的设定,磁碟的自动侦测设定等.当我们一开机时,系统BIOS会检查CMOS设定的内容与电脑实际的设备是否相符合,假如不符合,则会停住,会叫我们重新设定RUNSETUP.

为使系统随时保有目前设定值与使用配备规格参数等,特别制作一段记忆空间以供存入.该电路使用与RTC相同之电池,提供该电路在PC未开机下仍然工作---保有记忆值资料.(PC若在开机下,则对RTC电池进行充电工作,以保持RTC电池之电量.)

动作方式:

1.使用者可透过”SET-UP”动作查看CMOS设定,或修改..

2.透过I/OPort70,71可直接对CMOS进行读取或写入动作.

重要CMOS地址与存放资料:

1.00H-0DH:

RTC即时日期,时间与闹铃设定值存放区.

2.10H:

FDD型式(360K,1.2M,720,1.44M)

3.12H:

HDD型式代号/

4.15H-18H:

记忆体大小.

5.19H-1AH:

HDDC,D扩展位元组.

6.2EH-2FH:

Checksum值存放区,若10H-20H加总之值与2EH,2FH不符,则视同”Checksumfail”(也许有安置不同设备.)系统将停下,要求使用者作”SETUP”工作.

CPU开机自我测试无误后,将向CMOS调资料,以了解目前周边使用情形,再依所设定方式进行工作.(测试记忆体,作萤幕显示,作HDD,FDD读取….)

八-TIMER动作讲解

典型IC:

8253A

基本概论:

TIMER–可程式计时/计数器

因为系统电路有若干固定工作在固定时间内执行,例如:

DRAMRefresh工作,系统计时工作(非RTC计时)。

为减轻CPU负担,所以制作出一外部计时器,并以程式设定其计数值,待计时时间到达,再以中断方式,通知CPU执行特定之工作。

工作方式:

1.8253A外接一1.19MHz系统提供之Clock源作计数依据。

2.选择并设定为何种Model及计数/计时值。

(计数或计时)。

3.将Timer计数/计时器开启,Timer开始计数or计时。

4.到达计数or计时值时,产生OUT输出,接8259A,以产生中断。

实际使用:

8253A内含三组Timer,其设定为:

1.Timer_0:

55ms产生一时脉,接8259IRQ_0对CPU中断,以更新系统计时器使用。

2.Timer_1:

15us产生一时脉,接至NMI不右遮幕中断,产生Refresh讯号以作为DRAM刷新用,以保持DRAM内资料不至于消失。

3.Timer_2:

产生各种音频时脉,推动Speaker以产生各种音调。

九-BIOS动作讲解

典型IC:

28FS040

基本概论:

BIOS–BASICINPUT/OUTPUTSYSTEM基本输入输出系统。

1.控制整个系统基本的输入/输出系统,它是一相韧体(硬体+软体)的结构,是整个电脑系统的灵魂,电脑开机后,CPU将自动向其读取指令,然合作主机才依其指令做不同的运作,例如:

系统的自我测试,CMOS设定检查…等等。

2.一般将其内容存在FreshRom(例:

28FS040)中,若有需要程式更新,可配合ShadowRam与RefreshBIOS程式作up-date.

3.因为BIOSIC传输速度较慢,所以在线路安排上均其摆放在ISABUS上,已免拖累系统速度。

SHADOWRAM说明:

什么叫记忆体的SHADOWSRAM,由于在主机板内有各种不同的记体,有的记体传送速度较快,有的传送速度较慢其中RAM的速度就比ROM的速度快,主记忆体RAM的速度一般为50至70ns,而ROM的速度则在150至200ns,所以在主机系统的BIOS SETUP,就设定有所谓SHADOWRAM的程式,一开机时,系统就会把主机系统的BIOSRAM或VGACARD上的VIDEOBIOSROM的程式,全部拷贝载入RAM中,并且将这些程式的区域改为唯读状态。

凡是以后CPU要执行系统BIOS的程式或VIDEOBIOS的程式,都会自动转至速度较快的SHADOWRAM中执行,如此即可加快CPU的处理速度以及影像画面的显示。

十-DRAM动作讲解

典型IC:

41256-10

基本概论:

1.可存取记忆体大概分SRAM&DRAM二种。

2.SRAM构造类似为正反器(Flip-Flop)具有将资料锁住,达到记忆之功能,其优点为存取速度快,缺点为较占体积且价格昂贵。

3.DRAM构造类似电容器充电后保有其电荷一样保有或记忆资料般之功能,由于此电容相当小(约1PF)且有自我放电特性,所以须定时充电(Re-flash),其资料才不至于失落,因为如此,相对的其存取速度变慢,但其优点为所需面积小,单位面积不可大量提升其记忆容量。

4.一般均为DRAMIC组合焊接在RAMModule以灵活插配使用。

名词解释:

1.ROM:

ReadOnlyMemory唯读记忆体

2.RAM:

RandomAcessMemory可随机读取记忆体。

3.DRAM:

DynamicRAM.动态可读记忆体

4.SRAM:

StaticRAM静态可读记忆体

5.SDRAM:

SynchronousDRAM.同步型DRAM,采取Clock作为输入输出同步用,一般有PC100,PC133(100MHz&133MHz)二种,在RAMModule上一般均含一SPDEEPROM(SerialPresenceDetect)配件,记录此一RAMModule存取的各项参数,供系统先行读取后,作为对联一RAMModule作资料存取之速度参数设定。

(每秒传输量:

PC100=800MB,PC133=1067MB)

6.RDRAM:

RAMBUSDRAM(每秒传输量:

PC800=1.6GB)

7.DDRRAM:

(每秒传输量:

PC266=2.1GB)

8.MDRAM:

MagnetricDRAM可磁化动态