此处以容量为64Mbit位宽为16位的SDRSDRAM为例.docx

《此处以容量为64Mbit位宽为16位的SDRSDRAM为例.docx》由会员分享,可在线阅读,更多相关《此处以容量为64Mbit位宽为16位的SDRSDRAM为例.docx(14页珍藏版)》请在冰豆网上搜索。

此处以容量为64Mbit位宽为16位的SDRSDRAM为例

第一章绪论

随着工艺尺寸的缩小,当代ASIC与CPU的性能突飞猛进,然而存储器的核心频率任然只有100~200MHz左右,SDR/DDR/DDR2/DDR3等旨在提高数据吞吐率的接口协议应运而生。

当下,设计良好的存储控制器,已成为充分发挥系统带宽潜能、降低系统功耗的有力保障。

本章内容:

首先,将分三部分简要介绍DRAM存储器:

前SDRAM时代的DRAM、SDRAM带来的机遇与挑战、后SDRAM时代的DRAM;然后,将介绍本课题的内容,给出论文结构。

1前SDRAM时期的DRAM

1.1DRAM的发明

1966年RobertDennard博士在IBM的ThomasJ.Watson研究中心发明了DRAM存储器,其中的存储单元采用了1T1C的结构。

RobertDennard获得了美国专利,专利号为3,387,286。

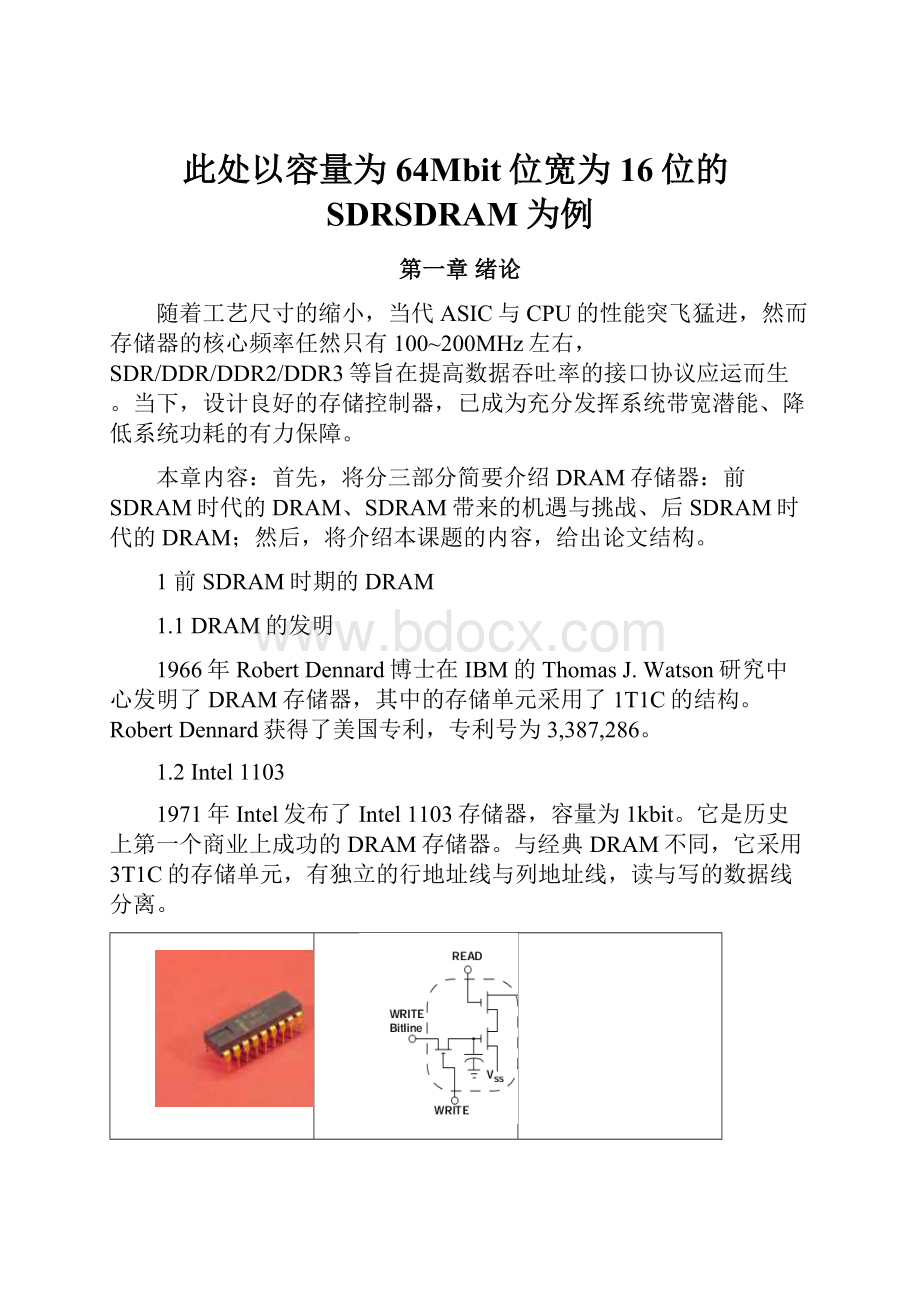

1.2Intel1103

1971年Intel发布了Intel1103存储器,容量为1kbit。

它是历史上第一个商业上成功的DRAM存储器。

与经典DRAM不同,它采用3T1C的存储单元,有独立的行地址线与列地址线,读与写的数据线分离。

1.3MostekMK4096

1973年Mostek发布了MostekMK4096存储器,容量为4k,由RobertProebsting设计。

它是历史上第一个复用行列地址线的DRAM。

行列地址线的复用,减少了封转管脚,降低了成本,这个传统延续至今。

在鼎盛时期,Mostek曾占有3/4的市场份额。

1.4典型的传统异步DRAM

在1970年代中期,占据主流的是异步接口的DRAM,那时的的“ClockedDRAM”仅仅昙花一现。

这种经典异步接口,与课本《数字集成电路设计透视》中的叙述十分吻合。

每次读写前,必须分别进行行选通与列选通,即便读写同一行里的数据,也不能省略任何步骤。

一张典型的时序图如下:

1.5PageMode、FastPageMode(FPM)、Nibblemode的出现

在异步DRAM的时代,出现过许多改进极富有特点的接口改进。

PageMode的出现是一个里程碑。

PageMode的DRAM可以把一整行数据保存在集成于片上的灵敏放大器整列中,这访问同一行时,就不必重复进行行选通。

PageMode的操作,利用了访问的空间局部性,从而提升了系统的性能。

行缓冲的思想,一直延续到了当代的DRAM。

FastPageMode出现于1980年代早期,直到1990年代早期任然属于主流。

FastPageMode中,只要RAS_B有效,就打开列地址缓冲,从而可以在CAS_B发起前锁存列地址,这样就提高了读写效率。

Nibblemode是TI对FPMDRAM的一种改进,添加了类似于4位突发传送的功能。

1.6ExtendedDataOutput(EDO)与BurstEDO的出现

在1990年代中期,出现了ExtendedDataOutput的DRAM。

它增加了OE_B信号,来代替CAS_B去控制输出缓冲。

于是,在CAS_B上升后,数据可以保持更多时间,故名“ExtendedDataOutput”。

EDO允许CAS_B下降沿与数据交叠,缩短了pagemode下的读写周期,故效率比FPM更高。

BurstEDO增加了列地址自动增加的功能,进一步简化了操作,提高了效率。

几种异步模式的时序对比如下图:

上图摘自ICE公司的《Memory1997》

2SDRAM带来的机遇与挑战

SDRAM,意为同步的DRAM,其数据和指令都与时钟上升沿对齐。

最早的样品,由三星在1993年生产。

在1996-2002年期间,SDRAM逐步取代了异步的FPMDRAM、EDODRAM,称雄PC内存市场。

在2003年之后,逐渐被DDRSDRAM取代。

它与前代异步DRAM的不同包括:

同步时钟、多Bank机制、流水线化的操作、Burst读写的引入。

由于每个时钟周期,只在上升沿传送一次数据,它也被称为SDRSDRAM,以便与DDRSDRAM区别。

2.1SDRAM基本硬件参数

SDRAM的常见容量包括:

16Mbit、64Mbit、128Mbit、256Mbit、512Mbit。

其中,除了16Mbit分为2个Bank外,其他容量的SDRAM都分为4个Bank。

SDRAM的常见数据位宽包括:

4bit、8bit、16bit、32bit。

如果系统位宽64bit,用16个512Mbit容量4bit位宽的SDRAM并联,可以实现8Gbit的存储空间;而如果用2个512Mbit容量32bit位宽的SDRAM并联,只能实现1Gbit的存储空间。

SDRAM的BurstLength,即读写突发传送的周期数,一般可设置为1、2、4、8以及FullPage,在初始化时通过写模式寄存器来设置。

需要注意的是,如果列读写时,地址没有与BL对齐,SDRAM会自行Wrap地址,导致意外的结果。

SDRAM的CasLatency,即从发送列读取指令到有效数据出现的延时,一般为2或3个时钟周期,少数器件可以为1个周期,在初始化时通过写模式寄存器来设置。

一般CL=3时,tAC参数(即时钟上升沿到有效数据出现的延时)较小,从而使器件可以工作在较高的频率。

SDRAM的常见速度等级包括:

100MHz(T=10ns)、125MHz(T=8ns)、133MHz(T=7.5ns)、143MHz(T=7ns)、166MHz(T=6ns)、183MHz(T=5.5ns)、200MHz(T=5ns)。

速度等级一般对应CL=3时的最高工作频率。

器件的最高工作频率越高,表示其AC延时参数越小。

2.2SDRAM的三维地址空间

(上图摘自Micron公司的SDRAM器件手册)

当代SDRAM的地址空间由Bank、Row、Column三个维度。

64Mbit及以上容量的SDRAM一般分为4个Bank。

为了与内存模组中PhysicalBank(Rank)的概念区别,SDRAM的Bank有时也叫LogicBank。

每个Bank都是一个Row与Column构建的阵列;阵列的每个单元都是一组数据,这组数据的位宽与SDRAM数据接口位宽一致。

例如,一个容量64Mbit位宽16bit的SDRAM地址空间为:

4bank*(2^12)Row*(2^8)Column*16bit=64Mbit,器件手册一般写为4*1M*16bit=64Mbit。

2.3芯片规格与SDRAM芯片组的容量

关于SDRAM芯片寻址的术语——Bank、Row、Column已在上一节给出了解释。

下面解释几个SDRAM芯片组中常用的术语。

Rank:

又叫PhysicalBank,指的是一组被同时操作的DRAM芯片。

通常,它们的数据总线被合并,以提供系统所需要的数据位宽,如Intel处理器要求的64bit。

Page:

一般指同一个Rank中Bankadddress、Rowaddress相同的空间。

可以认为将Rank中所有SDRAM芯片中的RowBuffer合并在一起,就组成了Rank中的PageBuffer。

关于RowBuffer、PageBuffer对DRAM访问的影响将在下一节讲述。

以64bit位宽的系统为例,综合列出不同规格SDRAM的3维地址空间,以及组成Rank后的特性:

ChipSize

ChipDQ/

Fab

BankNum

RowNum

ColNum

RowBufSize

64bitPageSize

64bitRankSize

16Mb

16ISSI

2

2048

256

4kb

16kb

64Mb

64Mb

32Micron

4

2048

256

8kb

16kb

128Mb

16Micron

4

4096

256

4kb

16kb

256Mb

8Micron

4

4096

512

4kb

32kb

512Mb

4Micron

4

4096

1024

4kb

64kb

1Gb

128Mb

32Micron

4

4096

256

8kb

16kb

256Mb

16Micron

4

4096

512

8kb

32kb

512Mb

8Micron

4

4096

1024

8kb

64kb

1Gb

4Micron

4

4096

2048

8kb

128kb

2Gb

256Mb

32ISSI

4

4096

512

16kb

32k

512Mb

16Micron

4

8192

512

8kb

32kb

1Gb

8Micron

4

8192

1024

8kb

64kb

2Gb

4Micron

4

8192

2048

8kb

128kb

4Gb

512Mb

32ISSI

4

8192

512

16kb

32kb

1Gb

16Micron

4

8192

1024

16kb

64kb

2Gb

8Micron

4

8192

2048

16kb

128kb

4Gb

4Micron

4

8192

4096

16kb

256kb

8Gb

注:

其中Micron64Mb:

x32的芯片虽然是2048行,计算刷新周期时要按4096行算。

而ISSI16Mb:

x16的芯片也是2048行,刷新时确实按2048行算。

关于刷新的原理见后文。

2.4RowBuffer对SDRAM读写的影响。

SDRAM的每个Bank都有一个RowBuffer,其实就是一排灵敏放大器(SenseAmplifier)。

每次激活(Activate)一个Row地址后,就打开RowBuffer把整个Row的数据保存在其中;Precharge指令可以关闭指定Bank的RowBuffer,PrechargeAll可以关闭所有Bank的RowBuffer;我们称RowBuffer关闭的Bank为空闲(Idle)的Bank。

由于RowBuffer的存在,SDRAM的访问分为如下三种情况:

(1)当前访问的Row所在的bank中,rowbuffer关闭。

此时,需要先激活Row,再发读写指令和Column地址。

此情况,读写延时中等。

(2)当前访问的Row,正好保存在相应bank的rowbuffer里。

此时,不需要激活Row,直接发读写指令和Column地址,就可以访问。

此情况,读写延时最小。

(3)当前访问的Row所在的bank中,rowbuffer打开,存的是另一个Row的数据。

此时,必须先发送Precharge或PrechargeAll指令关闭rowbuffer,再激活Row,最后发读写指令和Column地址。

此情况,读写延时最大。

2.5SDRAM的新天地

SDRAM带来的最大机遇就是它流水线化、并行化的接口设计,只要不违反管脚、时序延时的限制,多个Bank可以并肩工作。

恰如ScottRixner在ISCA2000上指出的,“得益于当代存储器件的三维特性,重新排列存储操作顺序以分时访问DRAM大有好处。

这样的优化,就好比超标量处理器乱序调度算数错做一样。

”

围绕着访问请求重排、SDRAM指令乱序执行、地址映射、RowBuffer关闭策略,各种优化方法层出不穷,从简单的多bank交错操作,到包含自适应机制的RowBuffer管理策略,不胜枚举。

针对视频处理、多核、通信等不同应用,设计SDRAM控制器时还需要根据“实时性”的限制,在低延时和高带宽利用率之间有所取舍。

所有这些开启了DRAM控制系统的一个新篇章。

3后SDRAM时代的DRAM

SDRAM之后,依次出现了DDR、DDR2、DDR3这几代DRAM。

和SDRSDRAM一样,它们也采用多bank流水线化操作的同步架构,其内部半导体存储单元的核心频率也任然在100~200MHz之间。

DDR、DDR2、DDR3相对于SDRSDRAM最大的区别在于使用了多bit预取的技术。

从DDR开始,同时在上升沿和下降沿对数据进行采样。

从DDR2开始,I/O接口的频率开始高于存储单元的核心频率。

下图对SDR、DDR、DDR2、DDR3的SDRAM做了对比:

不过,也正是多bit预取技术,使得DDRSDRAM的最小BurstLength为2而DDR2SDRAM的最小BurstLength为4,DDR3略有不同,最小BurstLength为4。

另一方面,从SDR、DDR、DDR2到DDR3,指令延时略有差异,SDR访问的优化算法也可用于DDR、DDR2到DDR3,但需要更具参数的相对关系重新调整,不能生搬硬套。

3.1DDRSDRAM引入的其他重要特新

差分时钟CK和CK_B。

差分时钟可以抑制温度、电阻等因素对时钟精度的影响。

在CK上升沿和CK_B下降沿的交叉点采样对指令信号采样;把CK和CK_B的所有交叉点作为数据采样的参考点。

数据采样脉冲DQS。

DDRSDRAM使用Source-Synchronous接口,以确保搞数据传送率下的信号完整性。

DQS是一个双向端口,写数据时,DQS为DDRSDRAM的输入,其上升沿和下降沿分别与两个数据各自的中心对齐;读数据时,DQS为DDRSDRAM的输出,其上升沿和下降沿分别与两个数据各自的起始边沿对齐。

片上DLL。

随着数据传送频率的提升,时钟树延时(ClockInsertionDelay)变得更加严重,使得片上DLL成为了必需。

片上DLL可以通过模式寄存器来开启和关闭,使用时通常会开启DLL。

3.2DDR2SDRAM引入的其他重要特性

PostCAS。

为提高带宽利用率而作的接口时序改进。

在SDR和DDRSDRAM的时代,行选通、列读取之间必须满足tRCD延时;DDR2接口中可以在行选通后直接进行列读取,而有效数据出现相对于行选通的延时不变。

这样可以避免不同bank间的行选通、列读取指令碰撞,提高效率。

ODT(On-DieTermination)。

终端电阻起着平衡信号完整性和电压摆幅的作用。

在SDR和DDRSDRAM的时代,终端电阻是作在电路板上的,而DDR2使用了片上终端电阻(ODT),从而提高了配置的灵活性,降低了电路板的设计难度与成本。

内存控制器通过写EMR寄存器来设定或更新ODT的值。

OCD(Off-ChipDriver)校准。

DDR2SDRAM引入了片外驱动校准,以提高信号完整性。

校准时,调整的是片内上拉、下拉电阻的等级。

由于DDR2还引入了差分的数据选取脉冲,基本已满足了信号完整性的要求,所以OCD也只在高端场合应用过。

目前Micron等公司的DDR2SDRAM已经不再支持OCD了。

3.3DDR3SDRAM引入的其他重要特性

RESET_B管脚。

DDR3SDRAM增加了RESET_B管脚,使得存储芯片可以很容易地进入初始化状态。

当RESET_B有效时,存储芯片内部时钟关闭,处于低功耗的状态;RESET_B从有效变为无效后,存储芯片自动进入初始化阶段。

Burst-Chop与On-The-Fly技术。

DDR3SDRAM采用8n-bit预取,从DDR、DDR2的情况推测应该只支持长度为8的突发传送。

但是,DDR3SDRAM支持Burst-Chop,可以实现长为4的突发传送。

可以通过模式寄存器设置突发传送长度,也使用On-The-Fly技术通过A12地址为在发起读写时确定突发传送长度。

需要注意的是Burst-Chop,只相当于一个Mask操作,不能节约总线时间。

ZQ校准。

DDR3SDRAM的ZQ校准提供了更加有效的可控阻抗机制。

长校准使DRAM能在初始化时最小化驱动电路工艺偏差的影响;正常操作时的短校准可以减小电压、温度漂移带来的阻抗变化。

最终,ZQ校准为良好的信号完整性提供了保障。

动态片上终端电阻(DynamicODT)。

片上终端电阻(ODT)可以减小当前模组的时钟抖动以及其他模组引起的信号反射。

确保信号完整性,就可以提供可预测的有效数据窗口(dataeye)。

动态片上终端电阻技术,就是可以根据是否进行写操作而在标准电阻、写电阻之间自动切换,免去了像在DDR2SDRAM中那样更改模式寄存器的麻烦。

AutoSelf-Refresh。

JEDEC标准中的可选特性,如果实现并被启用,SDRAM会根据自身的温度决定自刷新的频率以降低功耗。

PartialArraySelf-Refresh。

JEDEC标准中的可选特性,如果实现并被启用,可一只刷新SDRAM中有必要刷新的Bank,以降低功耗。

4本课题的内容

本课题研究SDRAM内存控制器的设计。

从SDRAM的结构与基本操作入手,分析各种优化策略,然后给出基于ClosePagePolicy的内存控制器设计方案,并将其集成到Altera的SOPC系统中。

整个设计流程包括:

Spec编写、模块划分与时序设计,RTL级的verilog设计,RTL级的ModelSIM仿真,Quartus综合,后仿真,静态时序分析,FPGA测试。

SOPC集成的工作包括:

Avalon-MMSlaveWrapper的编写,Avalon-MMMasterBFM仿真测试,基于JtagtoAvalonMasterBridge的FPGA硬件测试。

5论文结构

第一章:

绪论。

第二章:

SDRAM基本操作与优化策略。

第三章:

基于ClosePagePolicy的内存控制器后端设计。

第四章:

SDRC_Lite内存控制器的仿真、综合与硬件测试。

第五章:

SDRC_Lite内存控制器的SOPC集成与测试。

第六章:

尾声与致谢。

6本章参考文献

[1]S.Rixner,W.J.Dally,U.J.Kapasi,P.Mattson,andJ.D.Owens.Memoryaccessscheduling.ISCA2000:

p128–138

[2]JEDEC.JEDECstandardNo.21-C.2012

[3]JEDEC.JEDECstandardJESD79F.2008

[4]JEDEC.JEDECstandardJESD79-2F.2009

[5]JEDEC.JEDECstandardJESD79-3E.2010

[6]ComputerHistoryMuseum.puterhistory.org

[7]ISSI.

[8]Micron.

[9]Micron.64Mbx4,x8,x16SDRSDRAM.2012

[10]Micron.TN4605GeneralDDRSDRAMFunctionality.2001

[11]Micron.TN4605DDR2OffersNewFeaturesandFunctionality.2005

[12]Micron.TN4102DDR3ZQCalibration.2008

[13]Micron.TN4104DDR3DynamicOn-DieTermination.2008

[14]Elpida.E0678E10DDR2SDRAMTechnology.2005

[15]Elpida.E1503E10NewFeaturesofDDR3SDRAM.2009

[16]IntegratedCircuitEngineeringCorporation.Memory1997.1997:

Ch7DRAMTechnology

[17]JanM.Rabaey,A.Chandrakasan,B.Nikolic.DigitalIntegratedCircuits(2ndEdition).2003:

Ch12DesigningMemoryandArrayStructures

[18]BrentKeeth,R.J.Baker,B.Johnson,FengLin.DRAMCircuitDesign:

FundamentalandHigh-SpeedTopics.2007:

Ch01AnIntroductiontoDRAM

[19]BruceJacob,SpencerNg,DavidWang.MemorySystems:

Cache,DRAM,Disk.2007:

Ch7OverviewofDRAMs