同或门版图课程设计报告.docx

《同或门版图课程设计报告.docx》由会员分享,可在线阅读,更多相关《同或门版图课程设计报告.docx(9页珍藏版)》请在冰豆网上搜索。

同或门版图课程设计报告

合肥工业大学

课程设计

设计题目:

CMOS结构同或门版图

学生姓名:

陈鑫欣

学号:

20074791

专业班级:

微电子学07-02班

指导老师:

汪涛易茂祥杨依忠

2010年12月15日

一、电路逻辑功能

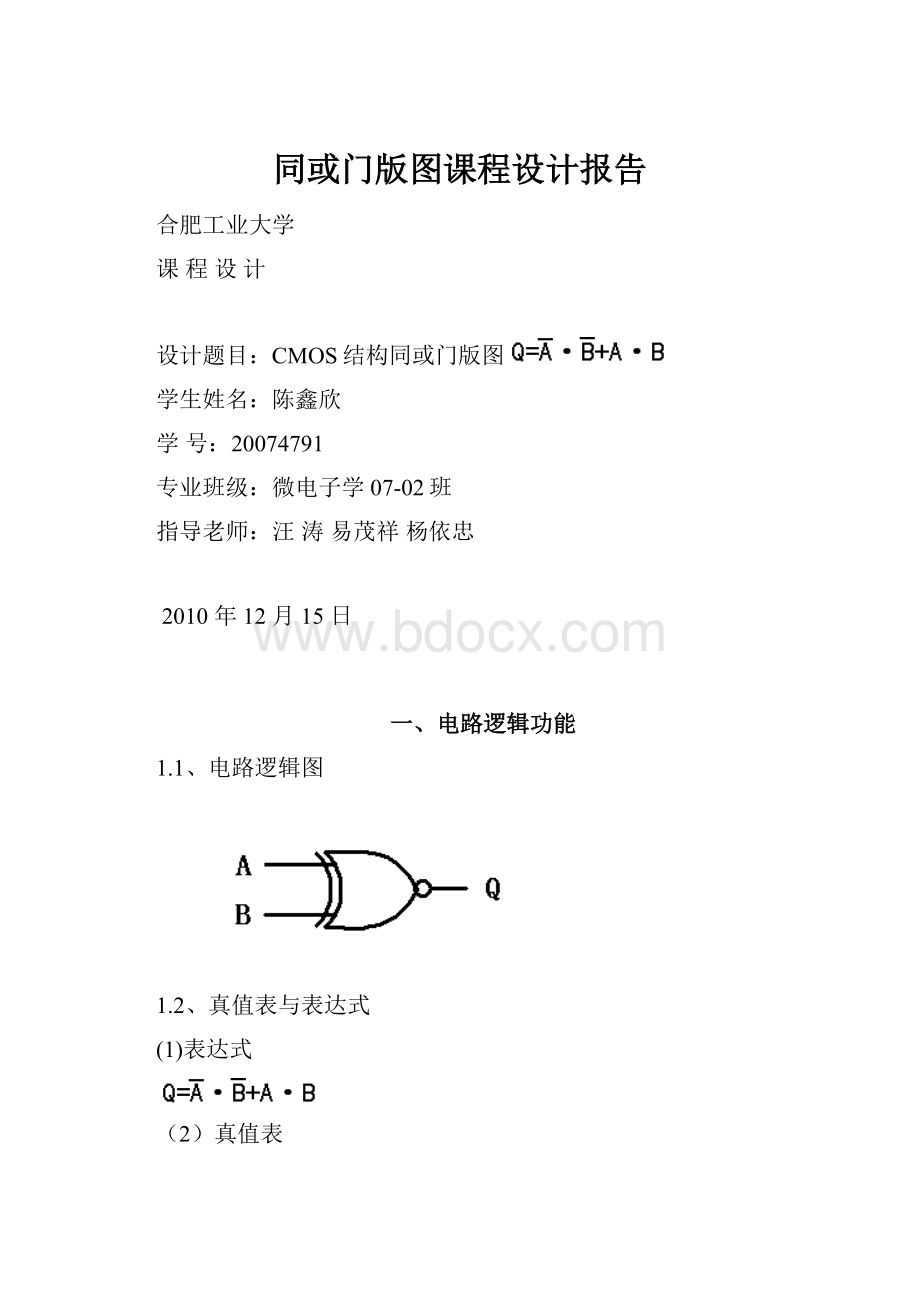

1.1、电路逻辑图

1.2、真值表与表达式

(1)表达式

(2)真值表

A

B

Q

1

1

1

0

0

1

1

0

0

0

1

0

1.3、线路图

1.4、ERC验证

ERC:

ElectricalRulesCheck电气规则检查,主要是对电路原理图的电学法则进行测试,通常是按照用户指定的物理、逻辑特性经行。

通常在电路原理设计完成之后,网表文件生成之前,设计者需要进行电气法测试。

其任务是利用软件测试用户设计的电路,以便找出人为的疏忽,测试完成之后,系统还将自动生成各种可能错误的报告,同时在电路原理图的相应位置上记号,以便进行修正。

通过电路逻辑图设计与之功能一样的电路图如图2.2所示,然后将此电路图通过九天软件绘制出来,电路图连接好后,再对其进行标注,如输入、输出端口,然后进行ERC验证直到没有错误为止,如图2.3所示,然后对其进行网表生成。

二、版图设计

2.1、总体版图以及DRC验证

当给定电路原理图设计其版图时,必须根据所用的工艺设计规则,时刻注意版图同一层上以及不同层间的图形大小及相对位置关系。

然而对于版图设计初学者来说,第一次设计就能全面考虑各种设计规则是不可能的。

为此,需要借助版图设计工具的在线设计规则检查(DRC)功能来及时发现存在的问题。

根据电路逻辑图以及线路图在九天软件上绘制与之对应的版图,,将基本的版图绘制好之后,再对版图里的输入、输出端口进行标注,以及电源线和地线,一切就绪之后再对版图进行验证,查找其中的错误,并对其进行修改直到没有错误为止如附录所示。

2.2、Cmos反相器

当输入电压为高时,PMOS因其栅压栅压等于0而截止,而NMOS导通,此时输出电压为低电平而接近0.相反,当输入电压为低时,NMOS和PMOS管分别关断和导通。

产生高电平输出电压。

不论那种逻辑状态,串联在高电平和地之间的这两个晶体管中总有一个处于非导通状态。

(

)

2.3、版图制作说明

宽度规则

多边形的最小宽度(在制版时,所有的线形都会转换为多边形)是一关键尺寸,它定义了制造工艺的极限尺寸。

若宽度小于某一特定值,那么制造工艺就无法保证可靠地制造连续的连接和连线,就有可能在该层上产生开路现象。

间距规则

间距规则指的是两个多边形之间的最小距离。

一般来说,间距规则可以用来避免在两个多边形之间形成短路。

间距规则不但应用于同一层上的多边形,也应用于不同层之间和不同情况下的多边形和结构。

交叠规则

交叠规则为一个多边形与另一个多边形之间相交叠或相包裹的最小尺寸限制。

例如,金属层与通孔或接触孔交叠。

使用不同层上的多边形来制造某种结构,放置多边形的预期位置与实际位置之间就很可能会出现偏差。

对某些分层来说,多边形间的偏差可能会导致电路连接出现不希望有的开路或短路。

三、同或门版图设计的LVS验证

LVS检查即LayoutVersusSchematics。

是一种用使版图和逻辑图相对照,检查各项连接和设计是否与原理图一致。

从几何描述提取电路信息的方式称作电路提取或CircuitExtraction,电路提取软件将集成电路的几何定义文件扩展为一层一层的几何图形和其布局的描述,经过对此描述的扫描可找出所有晶体管和电路的连接。

电路提取程序的结果是一个网表。

网表是一组语句,用这些语句来定义电路的元件(如晶体管或门)和它们的连接。

单独的晶体管则只列出与其相连的节点。

更重要的是,通过这样提取的电路还可与设计者原始设计的电路进行比较,以发现不同之点,一旦有差异存在,就必定存在着错误。

在进行三输入与或门版图设计的LVS验证之前,必须保证版图设计的ERC、DRC验证没有错误,才能进行验证,验证之前先将LDC对话框里程序的几行命令根据自己前面所做的版图以及电路图进行一定的修改:

1.第43行,要将之改为版图名,即画版图前所命的名。

2.第62行,将之改为库名。

3.第63行,将之改为网表名,即画好电路图后,生成网表,并且确定的名字,如lzq.cdl;

4.第64行,将之改为电路图名,将此4处改正确后,再将程序最末尾处END后的几行程序删掉。

所有的一切改完之后,点击运行得到下图结果。

若没有提示“Noerror”,则表明二者不一致,需要不断检查版图和电路图,发现错误并改正。

保存之后运行。

四、同或门版图设计问题讨论

实验电路还是比较简单的。

在软件中画图也没有出现太大的问题。

在进行版图设计的时候还是要对版图设计和设计验证有一定的了解。

所以在进行实验之前要熟悉软件的使用。

版图设计是指创建工程制图(或网表)的精确的物理描述的过程,即在确定晶体管的尺寸和相互连接之后,将其转换成几何多边形的过程;而这一物理描述遵守制造工艺、设计流程、通过仿真显示为可行的性能要求所带来的约束。

最终目的是找到晶体管或单元包括电气连接所需要的最小硅面积的几何排列,这个过程就是版图设计。

对于复杂的版图设计,一般把版图设计分成若干个子步骤进行:

1、划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。

2、版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。

3、布线完成模块间的互连,并进一步优化布线结果。

4、压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。

可以从不同角度对版图设计方法进行分类。

如果按设计自动化程度来分,可将版图设计方法分成手工设计和自动设计2大类。

如果按照对布局布线位置的限制和布局模块的限制来分,则可把设计方法分成全定制(fullcustom)和半定制(semicustom)2大类。

而对于全定制设计模式,目前有3种CAD工具服务于他:

几何图形的交互图形编辑、符号法和积木块自动布图。

在进行版图设计的时候对版图的布局也是实验过程中应当注意的地方。

布局又包括初始布局和迭代改善两个步骤:

①初始布局的作用是提高布局质量及减少下一步迭代改善时的迭代次数。

②迭代改善则是对初始布局的设计结果进行优化的过程,它是决定布局质量的关键。

布局的目的有:

1、确保布线器能够完成布线。

2、最小化关键网络的延迟。

3、提高芯片的密集度。

4、最小化功耗。

5、最小化信号间的串扰。

6、使估计的互连总长度最小。

7、符合关键网络的时序要求8、使互连得拥塞最小。

根据LVS的结果可以看出un-matched为0,说明不匹配的没有。

rewiced也为0,sizeerror也为0说明尺寸也没问题。

pruned同样为0,active为6,说明有6个器件,与实验电路图一致。

NMOS逻辑块电路的设计:

根据NMOS逻辑块“与串或并”的规律构成N逻辑块电路。

PMOS逻辑块电路的设计:

根据PMOS逻辑“或串与并”的规律构成P逻辑块电路。

从而结合电路得到

。

五、结论

第一次尝试在电脑上进行版图的设计,有很多地方都不了解,都要通过自己对软件的学习才能顺利的进行实验。

在选取了2输入同或门电路的同时,我亲自将其棍图和版图画了一遍有助于在电脑上的操作,在画晶体管图式要注意电源和地的连接,不然会出现错误。

在实现了晶体管图后从而进行了版图的设计。

版图的设计相对于晶体管图来的复杂了一点,当我经过几天的版图实验后,发现其实都是那么简单。

熟能生巧,理解才是硬道理。

在画版图的时候还是出现了很多操作上的不规范和细节的处理不当,导致实验一开始并不顺利,不过在同学的指导纠错下还是顺利将版图完成并无错误。

会画版图也是一种本领,也是拿得出手的技术,实验不仅锻炼了我们的动手能力也让我们对版图设计有了初步的认识。

总的来说,实验简单,过程是最难的。

不管结果如何,在实验的过程中至少能学到很多东西,虽然这次实验我们顺利完成,但是要更深入的问题我们还是有很多不明白的,学无止境。