中规模集成电路的应用实验报告.docx

《中规模集成电路的应用实验报告.docx》由会员分享,可在线阅读,更多相关《中规模集成电路的应用实验报告.docx(16页珍藏版)》请在冰豆网上搜索。

中规模集成电路的应用实验报告

实验题目

中规模集成电路的应用

(一)

实验时间

2019年10月30日

一、实验目的

1.74ls13874ls13974ls148功能验证;

2.用74ls13874ls139实现全加器、全减器

二.实验环境

(1)+5V直流电源

(2)逻辑电平开关(3)逻辑电平显示器(4)MultisimISIS

(5)集成芯片74ls138,74ls139,74ls148,74ls20、74ls00(6)直流数字电压表

三、实验内容与步骤

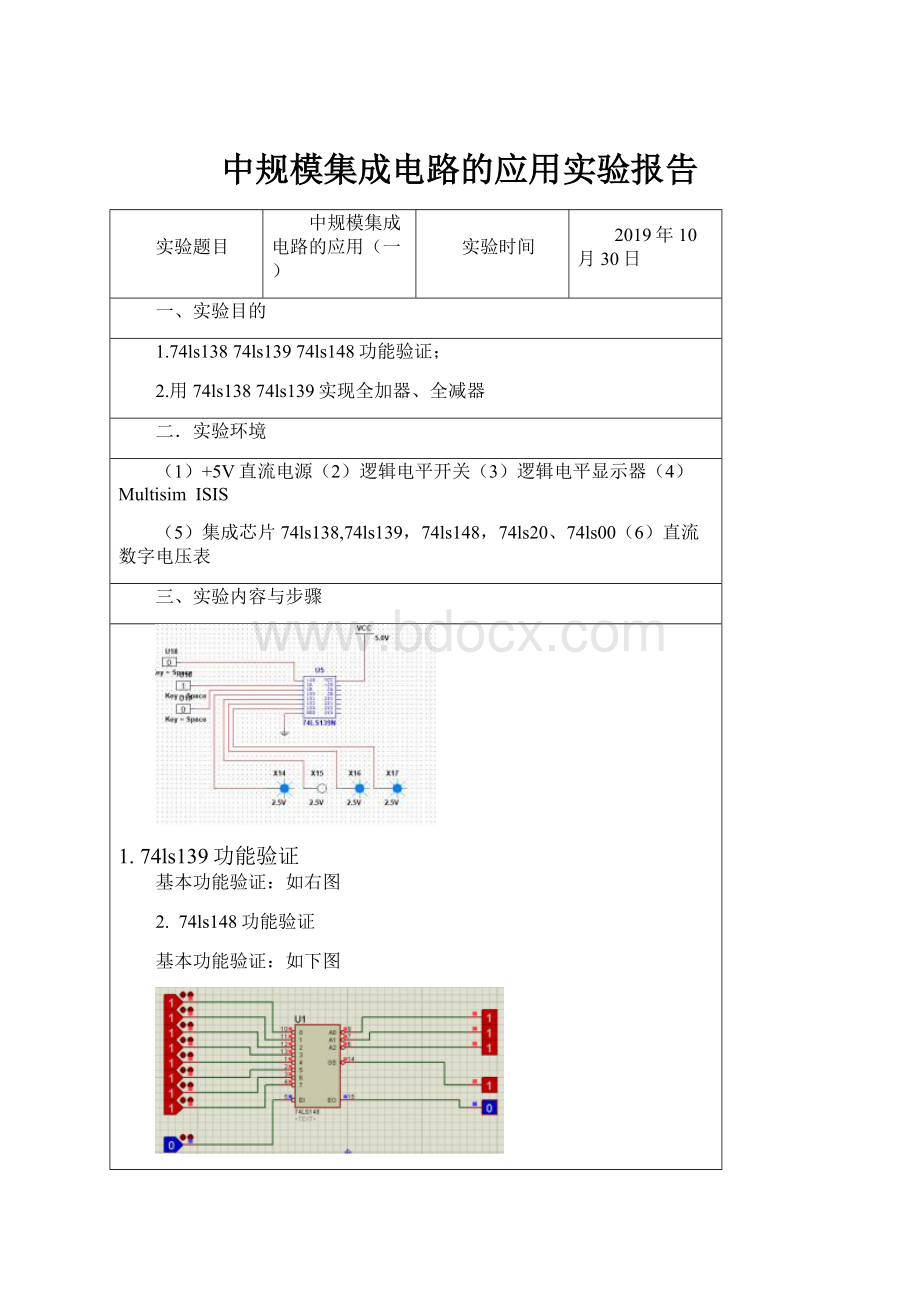

1.74ls139功能验证

基本功能验证:

如右图

2.74ls148功能验证

基本功能验证:

如下图

3.用74ls138以及74ls00实现全加器、全减器

(1)实验分析:

74ls138三个输入对应8个输出,意思就是一个3位的二进制输入对应一个10进制的一位例如ABC输入111那他那边的Y就会输出对应的一个位置如果ABC译码为8那Y里面就有一个位被弄为低电平。

74ls138就是38译码器,是TTL系列的,也就是74系列,有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0~Y7,工作电压一般的5V。

(2)用74ls138、74ls00实现全加器电路图如下:

(4)全减器真值表:

用74LS138、74LS00实现全减器电路图如下:

四、实验总结

通过本次课程设计对全加器器的设计和实现,确实积累和总结了不少的经验,锻炼了我的独立工作和实际动手能力,加深了对全加器工作原理的认识,提高了对复杂的综合性实践环节具有分析问题、解决问题、概括总结的实际工作能力。

经过这次短暂的实验报告,使我从中学到了不少的道理,真正的理解到,理论与实践之间还是有很大的距离,这必将有利于我们以后的学习。

使我明白,在以后的学习中,要不断的完善自己的知识体系结构,注意理论与实践的结合,学知识关键是要学活,而不能死记死搬书本上的知识,关键是要会灵活应用,这样所学到的东西才真正的学以致用,才达到了学习的真正目的!

实验题目

中规模集成电路的应用

(二)

实验时间

2019年11月6日

一、实验目的

(1)74LS24774LS24874LS8574LS283基本功能验证。

(2)用74LS283实现8421码转为余3码。

二.实验环境

(1)+5V直流电源

(2)逻辑电平开关(3)集成块74LS248(4)MultisimISIS

三、实验内容与步骤

1.74ls247是4线——七段译码器/驱动器(BCD输入,OC,15V)

2.74LS248是4线—七段译码器/驱动器(BCD输入,有上拉电阻),输出端(a-g)为低电平有效,可直接驱动指示灯或共阴极LED。

3.74ls85两个位数相同的二进制数进行比较

4.74ls283可进行两个4位二进制数的加法运算,每位有和输出∑1~∑4,进位由第四位得到C4.

四.实验过程与分析

74ls247验证

如右图

74ls248验证

如下图

74ls85验证

如下图

74ls283将8421码转为余3码(如右图)

J1端为输入8421码端。

灯X1、X2、X3、X4分别代表余三循环码的四位高低电平,灯亮代表高电平1,灯灭代表低电平0.(如下图)

输入为8421码制的0111时输出为相对应的余三码制的应为1111,结果如下图:

五、实验总结

实验前一定要做好预习工作,在具体的实验操作过程中一定要细心,比如在引脚设定时一定要做到“对号入座”,曾经自己由于管脚插反了,耗费了很多时间。

实验中遇到的各种大小问题基本都应自己独立排查解决,这对于自己独立解决问题的能力也是一个极大地提高和锻炼。

实验题目

计数器的应用

(一)

实验时间

2019年11月27日

一、实验目的

用74LS7474LS112组成异步4位二进制加法和减法计数器

二.实验环境

MultisimISIS

三、实验内容与步骤

1.74LS74加法器(左图)

74LS74减法器

(左图)

74LS112加法器(下图)74LS112减法器(下图)

四、实验过程与分析

(1)用74ls74构成4位加法计数器:

首先需要4个d触发器,然后将d触发器接成t’触发器,即把q’接到d。

同时把q’在接到下一个d触发器的脉冲上。

也就是说只有第一个d触发器要接外来脉冲,其他三个d触发器的脉冲都来自于上一个d触发器的q’,接外来脉冲的那个d触发器的输出是最低位。

(2)用74ls74做4位减法计数器:

同样将4个d触发器接成t’触发器,只不过这回是将q接到下一个d触发器的脉冲上。

(3)用74ls112做4位加法计数器:

74ls112是jk触发器,它做4位加法计数器的思路和d触发器一样,就是先把自己连成t’触发器,也就是只保留翻转功能,所以把每个jk触发器的j,k都输入为1。

同样需要4个jk触发器,但是jk触发器的脉冲是下降沿有效,所以和就和前面相反了,q接脉冲才是加法器,q’接脉冲是减法器。

五、实验总结

1.实验设计选择电路芯片时,应该先了解芯片的构造,原理,主要用途。

像本实验要求用74LS74和74ls112芯片。

通过了解可知道到74LS74是D触发器,74ls112是JK触发器。

做实验设计时,应该按步骤设计:

列真值表→根据真值表列出逻辑函数表达式并化简→根据化简了的逻辑表达式画出逻辑电路图,选择适当的电路芯片合理布线设计实验线路。

实验题目

计数器的应用

(二)

实验时间

2019年12月4日

一、实验目的

74ls16174ls160基本功能验证,用74ls16174ls160分别构成模12,模7计数器

二.实验环境

MultisimISIS

三、实验内容与步骤

74ls160:

1.用于快速计数的内部超前进位2.用于n位级联的进位输出3.同步可编程序

4.有置数控制线5.二极管箝位输入6.直接清零

同步计数74ls160是十进制计数器,也就是说它只能记十个数从0000-1001(0-9)到9之后再来时钟就回到0,首先是clk,这是时钟。

之后是rco,这是输出,MR是复位低电频有效(图上接线前面花圈的都是低电平有效)load是置数信号,当他为低电平时,在始终作用下读入D0到D3。

为了使161正常工作ENP和ENT接1另外D0到D3是置数端Q0到Q3是输出端。

这种同步可预置十进计数器是由四个D型触发器和若干个门电路构成,内部有超前进位,具有计数、置数、禁止、直接(异步)清零等功能。

74ls160功能验证

右图

74LS161:

74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端,可以串接计数器使用。

各引出端的逻辑功能如下。

1脚为清零端/RD,低电平有效。

2脚为时钟脉冲输入端CP,上升沿有效(CP↑)。

3~6脚为数据输入端A0~A3,可预置任意四位二进制数。

7脚和10脚分别为计数控制端EP和ET,当其中有一脚为低电平时计数器保持状态不变,当均为高电平时为计数状态。

9脚为同步并行置数控制端/LD,低电平有效。

11~14脚为数据输出端QQ30~。

15脚为进位输出端RCO,高电平有效。

74ls161为四位二进制,74ls160为2-10进制;且都为同步可预置计数器。

74ls161是4位二进制同步计数器(直接清除),74ls160是4位十进制同步计数器(直接清除)。

74LS161M=7,M=12计数器

原理:

74LS161是M=16计数器,可以转换为任意16以内的计数器,如果大于16,可以用多

片74LS161串行级联,构成M=n的计数器,n片74LS161可以构成M=16^n的计数器。

下图是74LS161M=7计数器,使用的是反馈置零法模7.计数与置数端无关所以输入接多少都可以。

(右图)

下图是74LS161,M=12计数器,原理和M=7一样,只是反馈置0从7变成了12,12的二进制数是1100,所以将Q3,Q2接入二输入与非门接到MR置0即可。

(下图)

74LS160M=7,M=12计数器

原理:

和74LS161一样,只是基础模值变为了10。

N片的模值为10^n。

同样是反馈置0法M=7计数,由于7<10,所以接法和74LS161一样,结果也是一样的。

(下图)

接着用74LS160做M=12计数,由于12>10,所以得用两片74LS160组成M=100计数器,输入端都不用接,计数输出与输入端无关,左边是个位,右边是十位,个位使能端全部接1,十位使能端一个接1,一个接个位进位输出,当个为满10,RCO变为高电平,十位使能端变为1,1开始计数十位进一之后,ENP又变为低电平,十位保持,个位一直在计数。

M=12,就让个位Q1,和十位Q0接二输入与非门到两个的MR,运行仿真,当数码管变为11时,下一位就转为00。

(下图)

五、实验总结

在整个设计的过程中,关键在于时序电路的连接及电路的细节设计上,连接时要特别注意分清各个管脚,要分析原理以及可行的原因,是整个电路可稳定工作。

从中我感觉到每个实验都是要反复实跋,其过程可能相当繁琐,但总会有所收获的

实验题目

计数器的应用(三)

实验时间

2019年12月11日

二、实验目的

验证74ls90的功能

利用74ls90构成模7计数器。

二.实验环境

ISIS

三、实验内容与步骤

74LS90模7;

8421(BCD)置零法:

循环圈:

0000—0001—0010—0011—0100—0101—0110—0000

8421(BCD)置九法:

循环圈:

0000—0001—0010—0011—0100—0101—1001—0000

5421(BCD)置零法:

循环圈:

0000—0001—0010—0011—0100—1000—1001—0000

5421(BCD)置九法:

循环圈:

0000—0001—0010—0011—0100—1000—1100—0000

74LS908421BCD计数

(右图)

74LS90=5421BCD计数下图

用74LS90分别用4种方法构成模7计数器:

8421(BCD)置零法:

(右图)

8421(BCD)置九法:

(下图)

5421(BCD)置零法:

(下图)

5421(BCD)置九法:

(下图)

五、实验总结

1.芯片使用存在功能好坏

2.电源连接不正确,接地点接到-5V上或接到模拟电子实验箱的电源上,非常危险,上电后芯片可能烧毁。

3逻辑开关电平前的发光二极管不亮,检查进入数字实验箱的电源连接线断

4.实验箱电源连接正确,电路自查确定无误后,电路验证还是不正确的情况下进行下面的排错检查:

(1)检查芯片的电源和地的电平是否正确(注意电源和地的引脚号)

(2)芯片的置数端和清零端是否连接正确

(3)时钟信号输入是否正确。

(4)从输出端按逻辑功能状态往前一步一步排查

实验题目

寄存器的应用

实验时间

2019年12月18日

一、实验目的

熟悉移位寄存器74LS194的逻辑功能及使用方法;

熟悉4位移位寄存器的应用。

验证74ls194的功能

利用74ls194构成环形计数器和扭环形计数器。

二.实验环境

ISIS

三、实验内容与步骤

将CLK与CP连接,MR高电平有效,连接电路,得出下图:

当CP=X,CR-=0,S1=S0=X时,它的功能是清除。

如下图:

当CP为上升沿有效,CR-=1,S1=S0=0时,它的功能是送数,即Q3Q2Q1Q0=D3D2D1D0,如下图:

当CP为上升沿有效,CR-=1,S1=1,S0=0时,它的功能是左移,如下图:

当CP为上升沿有效,CR-=1,S1=S0=0时,它的功能是保持,如下图:

利用74ls194做环形计数器,把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图所示。

设初态为Q3Q2Q1Q0=1000,则在CP作用下,模式设为右移,输出状态依次为:

利用74ls194做扭环形计数器,电路图如下:

扭环形计数器的实验原理是从初始值0000,开始,首先变为0001,再到0011,一直变化到1111,在变化为1110直到变为初始值0000,总共进行了八次变化得到,如图二与图三所示,每一次都是向左移位进行变化。

环形计数器与扭环形计数器的不同在于扭环行计数器是加了一个74LS04与非门而来。

环形计数器是在脉冲CP的作用下,从Q0移动到Q3左移位,其缺点是死循环太多,有2*n-n个状态没有用。

扭环形计数器是在清0信号作用下,初始状态为0,在计数器脉冲CP的作用下输入八个脉Q4输出一个对称方波,其若有n个触发器可以构成2n个触发器。

五、实验总结

我们用到了移位寄存器在本次试验中,移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。

既能左移又能右移的称为双向移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。

根据移位寄存器存取信息的方式不同分为:

串入串出、串入并出、并入串出、并入并出四种形式。

我们主要用到的集成块为74ls194,它是一个四位双向移位寄存器,其中:

D0~D1为并行输入端;Q0~Q3为并行输出端;SR-右移串引输入端;SL-左移串引输入端;S1、S0-操作模式控制端;/CR-为直接无条件清零端;CP-为时钟脉冲输入端。

为了提高环形计数器电路状态利用率,改变反馈函数为D0=D2',则得到如上所示逻辑电路图,称为扭环形计数器。

扭环形计数器的有效状态是:

000→100→110→111→011→001→000……(环形计数器是100→010→001→100→…),如此循环,工作时,首先用STA置电路为全0,然后加CP。

n个触发器组成的扭环形计数器2n个有效状态,有效状态利用率比环形计数器增加一倍。