eda电子路标二 课程设计.docx

《eda电子路标二 课程设计.docx》由会员分享,可在线阅读,更多相关《eda电子路标二 课程设计.docx(25页珍藏版)》请在冰豆网上搜索。

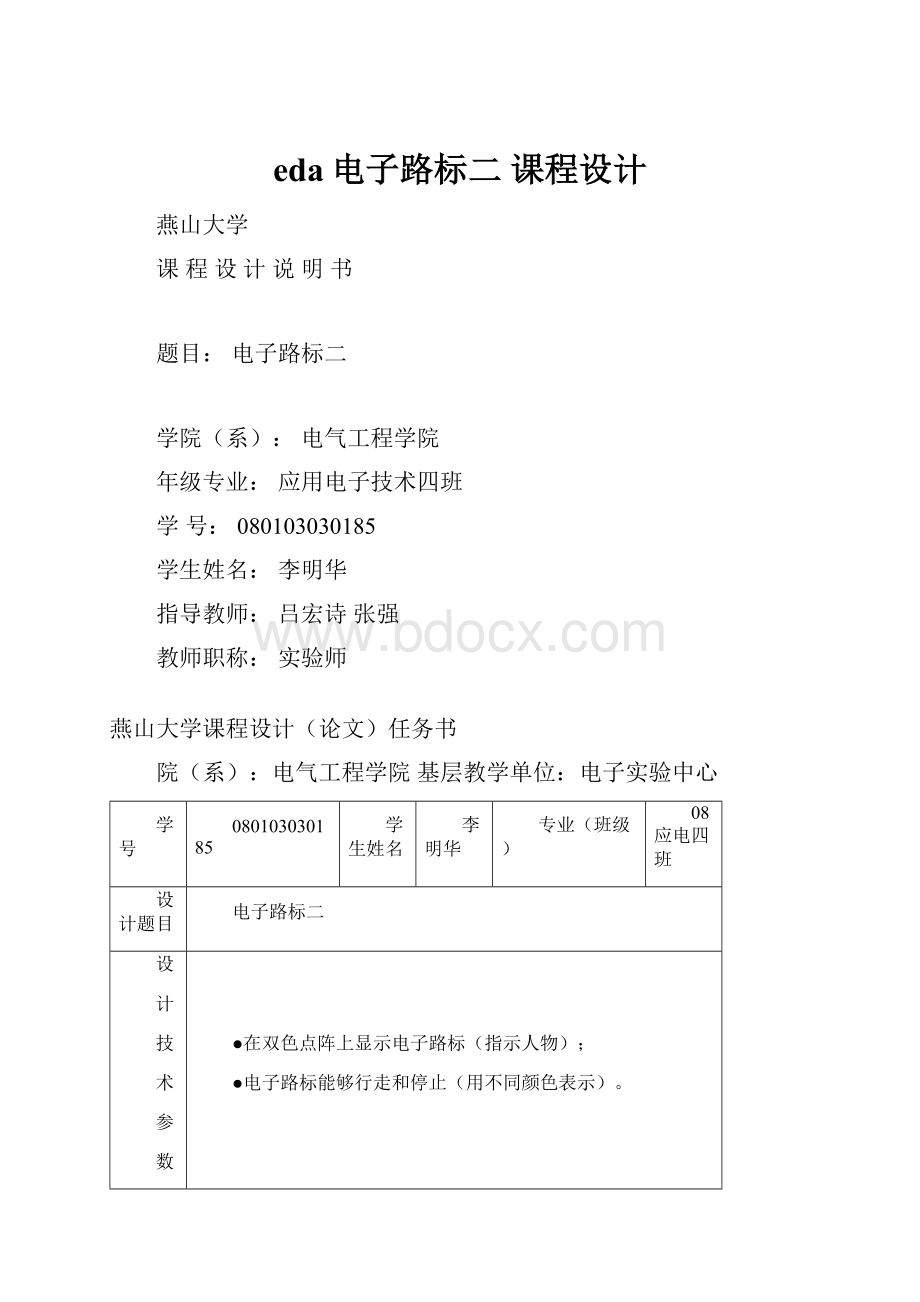

eda电子路标二课程设计

燕山大学

课程设计说明书

题目:

电子路标二

学院(系):

电气工程学院

年级专业:

应用电子技术四班

学号:

080103030185

学生姓名:

李明华

指导教师:

吕宏诗张强

教师职称:

实验师

燕山大学课程设计(论文)任务书

院(系):

电气工程学院基层教学单位:

电子实验中心

学号

080103030185

学生姓名

李明华

专业(班级)

08应电四班

设计题目

电子路标二

设

计

技

术

参

数

●在双色点阵上显示电子路标(指示人物);

●电子路标能够行走和停止(用不同颜色表示)。

设

计

要

求

●用双色点阵发光管显示电子路标;

●用频率组模块作为频率信号发生器。

工

作

量

●学会使用Max+PlusII软件、VerilogHDL语言和实验箱;

●独立完成电路设计,编程下载、连接电路和调试;

●参加答辩并书写任务书。

工

作

计

划

1.了解EDA的基本知识,学习使用软件Max+PlusII,下发任务书,开始电路设计;

2.学习VerilogHDL语言,用VerilogHDL进行程序设计

3.学习使用实验箱,继续电路设计;

4.完成电路设计;

5.编程下载、连接电路、调试和验收;

6.答辩并书写任务书

参

考

资

料

《数字电子技术基础》.阎石主编.高等教育出版社.

《EDA课程设计A指导书》.郑兆兆等编.

指导教师签字

吕宏诗张强

基层教学单位主任签字

金海龙

2011年1月14日

目录

第1章设明说明…………………………………………………………………………3

第2章verilogHDL设计源程序………………………………………………………5

第3章波形仿真…………………………………………………………………………13

第4章管脚锁定及硬件连线……………………………………………………………16

第5章总结………………………………………………………………………………18

第6章参考文献…………………………………………………………………………19

第1章设计说明

1.1设计思路

本设计“电子路标二”实现在双色8*8点阵上显示电子路标(指示人物),人物能够行走和停止。

行走时人物呈绿色,停止时人物呈红色。

具体显示效果见下图1.1-a,1.1-b,1.1-c三图,也可以加入橙灯闪动作为缓冲。

1.1-a1.1-b

1.1-c

要实现人物的“行走”,需要两幅画面交替循环显示,即图1.1-a,图1.1-b两幅图。

停止状态人物画面需要显示较长时间,可以通过自身循环显示实现。

在本设计中使用了频率组模块作为频率信号发生器。

本设计采用了两个频率,即低频率组中的2Hz和低频率组中的256Hz。

2Hz频率用来进行画面的切换,即人物行走时图1.1-a和图1.1-b画面的交替循环显示和人物停止时图1.1-c画面自身的循环显示。

8*8点阵一次只能点亮一行或一列,为了使人感觉各行或各列是同时点亮,需要较高频率的扫描,256Hz的频率信号就是扫描信号,在本次设计中采用逐行扫描,因为点阵是行共阴,列共阳,所以逐行扫描采用每个钟上升沿点亮一行,依次循环点亮各行,即各行依次循环置0,各列输出显示的图形。

`

1.2模块介绍

本次设计只采用了一个模块来实现设计的要求。

其中clk1,clk2为输入端口,row是一个八位输出端口,lineg为一个六位输出端口,liner为一个四位输出端口。

在模块中设置了变量j,用来对时钟脉冲clk1时钟脉冲进行计数,j=0时输出显示图1.1-a的画面,j=1时输出显示图1.1-b的画面,j=2时输出显示图1.1-a的画面,j=3时输出显示图1.1-b的画面,这样可以实现人物的行走状态。

j=4,5,6,7时输出显示图1.1-c的画面,这样可以实现人物的停止状态。

在j=7的下一个clk1的时钟上升沿,j的值被重新置0。

这样就可以实现行走和停止两种状态的交替显示。

通过更改clk1的输入时钟频率还可以变化交替间隔时间。

模块中的另一个时钟信号clk2用来实现逐行扫描。

通过如下语句实现一个画面的显示。

if(j==0)

begin

case(a)//显示图1.1-b所示图形

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b001100;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b001100;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001100;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b001100;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b001100;liner=4'b0000;end

endcase

a=a+1;

if(a>7)

begina=0;end

end

end

其中的变量a对clk2进行计数,每个clk2的上升沿a的值加1,通过case语句输出显示一行。

a的值大于7时被重新置0,从而实现逐行扫描。

由于要求实现双色显示,所以用到两个输出lineg和liner,分别接绿色和红色二极管阳极端口。

模块中在点亮一种颜色的二极管时封锁另一色二极管,从而避免出现色彩显示的错误。

第2章VerilogHDL设计源程序

本次课程设计的VerilogHDL源程序如下:

modulelubiao(clk1,clk2,lineg,liner,row);

outputlineg,liner,row;

inputclk1,clk2;

reg[7:

0]row;

reg[6:

1]lineg;

reg[5:

2]liner;

reg[2:

0]a,b,c,d,e;

reg[3:

0]j;

always@(posedgeclk1)//变量j从0到6循环

begin

j=j+1;

if(j>7)

begin

j=0;

end

end

always@(posedgeclk2)

begin

if(j==0)//j=0时显示图1.1-a所示图形

begin

case(a)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b001100;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b001100;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001100;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b001100;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b001100;liner=4'b0000;end

endcase

a=a+1;

if(a>7)

begina=0;end

end

elseif(j==1)//j=1时显示图1.1-b所示图形

begin

case(b)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b011110;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b101101;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001110;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b010010;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b100010;liner=4'b0000;end

endcase

b=b+1;

if(b>7)

beginb=0;end

end

elseif(j==2)//j=2时显示图1.1-a所示图形

begin

case(c)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b001100;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b001100;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001100;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b001100;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b001100;liner=4'b0000;end

endcase

c=c+1;

if(c>7)

beginc=0;end

end

elseif(j==3)//j=3时显示图1.1-b所示图形

begin

case(d)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b011110;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b101101;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001110;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b010010;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b100010;liner=4'b0000;end

endcase

d=d+1;

if(d>7)

begind=0;end

end

else

begin

case(e)//j=4,5,6,7时都显示图1.1-c所示图形

0:

beginrow=8'b11111110;liner=4'b0110;lineg=6'b000000;end

1:

beginrow=8'b11111101;liner=4'b0110;lineg=6'b000000;end

2:

beginrow=8'b11111011;liner=4'b1111;lineg=6'b000000;end

3:

beginrow=8'b11110111;liner=4'b1111;lineg=6'b000000;end

4:

beginrow=8'b11101111;liner=4'b1111;lineg=6'b000000;end

5:

beginrow=8'b11011111;liner=4'b0110;lineg=6'b000000;end

6:

beginrow=8'b10111111;liner=4'b0110;lineg=6'b000000;end

7:

beginrow=8'b01111111;liner=4'b0110;lineg=6'b000000;end

endcase

e=e+1;

if(e>7)

begine=0;end

end

end

endmodule

(附)后来又加入了橙色人形闪动的画面,扩展后的源程序为:

modulelubiao(clk1,clk2,lineg,liner,row);

outputlineg,liner,row;

inputclk1,clk2;

reg[7:

0]row;

reg[6:

1]lineg;

reg[5:

2]liner;

reg[2:

0]a,b,c,d,e,f,g,h,m,n,o;

reg[3:

0]j;

always@(posedgeclk1)

begin

j=j+1;

if(j>13)

begin

j=0;

end

end

always@(posedgeclk2)

begin

if(j==0)

begin

case(a)

0:

beginrow=8'b11111110;liner=4'b0110;lineg=6'b001100;end

1:

beginrow=8'b11111101;liner=4'b0110;lineg=6'b001100;end

2:

beginrow=8'b11111011;liner=4'b1111;lineg=6'b011110;end

3:

beginrow=8'b11110111;liner=4'b1111;lineg=6'b011110;end

4:

beginrow=8'b11101111;liner=4'b1111;lineg=6'b011110;end

5:

beginrow=8'b11011111;liner=4'b0110;lineg=6'b001100;end

6:

beginrow=8'b10111111;liner=4'b0110;lineg=6'b001100;end

7:

beginrow=8'b01111111;liner=4'b0110;lineg=6'b001100;end

endcase

a=a+1;

if(a>7)

begina=0;end

end

elseif(j==1)

begin

case(b)

0:

beginrow=8'b11111110;liner=4'b0000;lineg=6'b000000;end

1:

beginrow=8'b11111101;liner=4'b0000;lineg=6'b000000;end

2:

beginrow=8'b11111011;liner=4'b0000;lineg=6'b000000;end

3:

beginrow=8'b11110111;liner=4'b0000;lineg=6'b000000;end

4:

beginrow=8'b11101111;liner=4'b0000;lineg=6'b000000;end

5:

beginrow=8'b11011111;liner=4'b0000;lineg=6'b000000;end

6:

beginrow=8'b10111111;liner=4'b0000;lineg=6'b000000;end

7:

beginrow=8'b01111111;liner=4'b0000;lineg=6'b000000;end

endcase

b=b+1;

if(b>7)

beginb=0;end

end

elseif(j==2)

begin

case(c)

0:

beginrow=8'b11111110;liner=4'b0110;lineg=6'b001100;end

1:

beginrow=8'b11111101;liner=4'b0110;lineg=6'b001100;end

2:

beginrow=8'b11111011;liner=4'b1111;lineg=6'b011110;end

3:

beginrow=8'b11110111;liner=4'b1111;lineg=6'b011110;end

4:

beginrow=8'b11101111;liner=4'b1111;lineg=6'b011110;end

5:

beginrow=8'b11011111;liner=4'b0110;lineg=6'b001100;end

6:

beginrow=8'b10111111;liner=4'b0110;lineg=6'b001100;end

7:

beginrow=8'b01111111;liner=4'b0110;lineg=6'b001100;end

endcase

c=c+1;

if(c>7)

beginc=0;end

end

elseif(j==3)

begin

case(d)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b001100;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b001100;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001100;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b001100;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b001100;liner=4'b0000;end

endcase

d=d+1;

if(d>7)

begind=0;end

end

elseif(j==4)

begin

case(e)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b011110;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b101101;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001110;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b010010;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b100010;liner=4'b0000;end

endcase

e=e+1;

if(e>7)

begine=0;end

end

elseif(j==5)

begin

case(f)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b11111101;lineg=6'b001100;liner=4'b0000;end

2:

beginrow=8'b11111011;lineg=6'b001100;liner=4'b0000;end

3:

beginrow=8'b11110111;lineg=6'b001100;liner=4'b0000;end

4:

beginrow=8'b11101111;lineg=6'b001100;liner=4'b0000;end

5:

beginrow=8'b11011111;lineg=6'b001100;liner=4'b0000;end

6:

beginrow=8'b10111111;lineg=6'b001100;liner=4'b0000;end

7:

beginrow=8'b01111111;lineg=6'b001100;liner=4'b0000;end

endcase

f=f+1;

if(f>7)

beginf=0;end

end

elseif(j==6)

begin

case(g)

0:

beginrow=8'b11111110;lineg=6'b001100;liner=4'b0000;end

1:

beginrow=8'b1111110