LPMADDSUB1.docx

《LPMADDSUB1.docx》由会员分享,可在线阅读,更多相关《LPMADDSUB1.docx(10页珍藏版)》请在冰豆网上搜索。

LPMADDSUB1

LPM_ADD_SUB模块的应用

该模块为参数化的加/减法器,是参数化的宏功能模块库的一部分,功能为;既可以设计加法器,也可以设计减法器。

步骤如下:

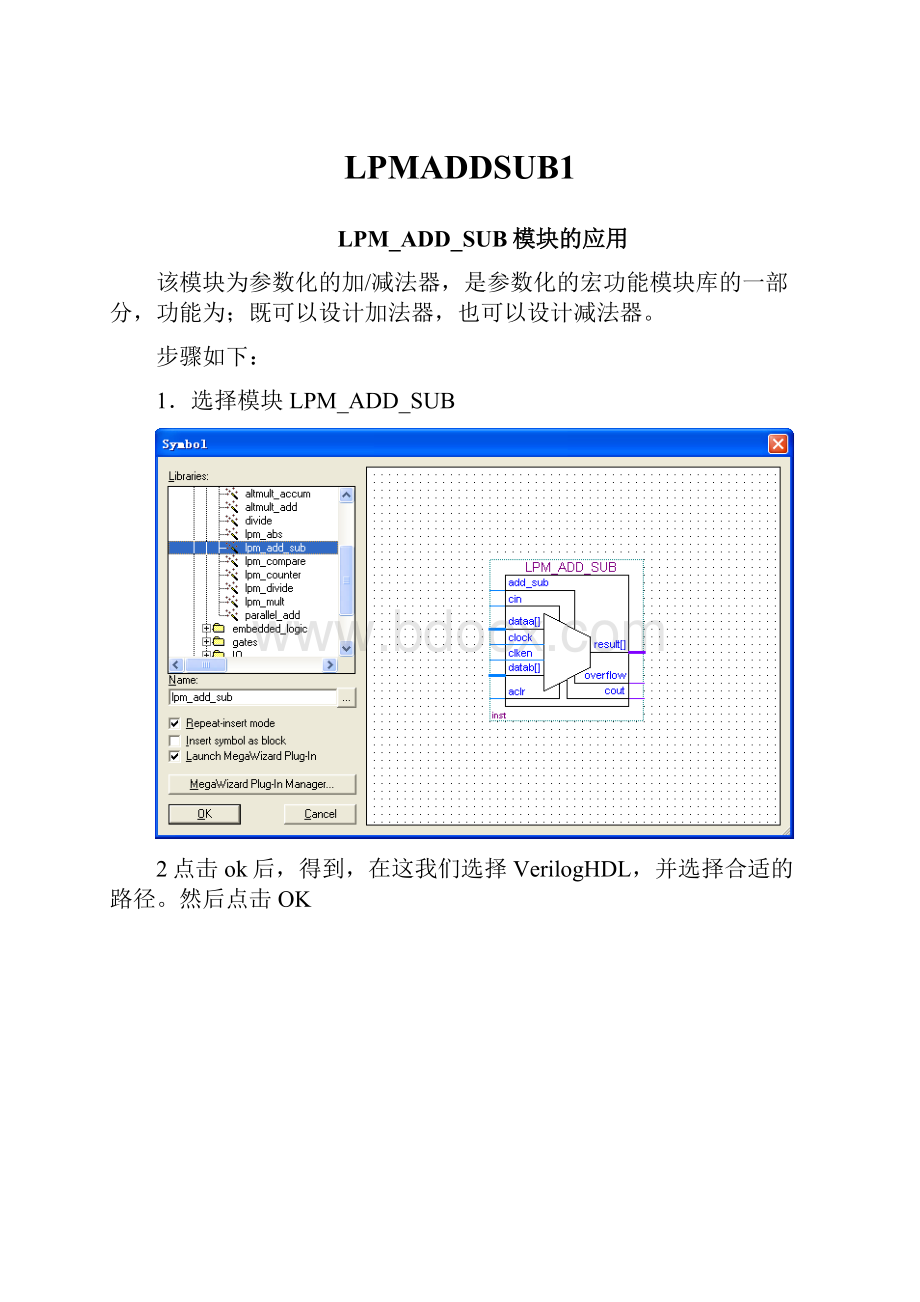

1.选择模块LPM_ADD_SUB

2点击ok后,得到,在这我们选择VerilogHDL,并选择合适的路径。

然后点击OK

3.进入属性编辑。

根据自己设计的要求,进行编辑!

这儿我们选择Cuclone设备!

输入、输出管脚选择4个!

并选择加、减功能!

然后点击OK

4..设置管脚的默认值!

我们不设置!

使用A、B管脚的输入值!

5.添加输入输出的管脚!

我们添加输入借进位管脚,添加输出借进位管脚和溢出管脚。

6.设置pipelinethefunction。

我们这儿选NO!

!

!

进入下一步!

7.点击OK结束设置!

8.放置该模块

9.按照基本操作步骤添加引脚,并进行编译,排除错误。

10..双击引脚标识,修改对话框中的内容,获得总线连接方式

11..使用tools/option,修改相应的仿真时间属性,从而达到理想的效果。

12按照常规的方法建立仿真文件,调入引脚,设置仿真时间,设置信号属性,

13.对仿真文件的输入信号设定仿真值和修改地址总线的值

14.编译成功后,仿真,获得仿真结果:

观察仿真结果

上图过小,放大结果如下:

图1

注:

从左到右,分别记为1~4次运算,且为加法运算!

图2

注:

从左到右,分别记为5~8次运算,且为减法运算!

对仿真结果的分析

1次运算为1010+0000结果为1010,没有产生进位,也没有产生溢出!

2次运算为0000+0101结果为0101,没有产生进位,也没有产生溢出!

3次运算为0111+0111结果为1110,没有产生进位,产生溢出!

4次运算为1111+0001结果为0001,产生进位,没有产生溢出!

1次运算为0111-1100=1011结果为1011,产生进位,产生溢出!

1次运算为1101-0001=1100结果为1010,没有产生进位,也没有产生溢出!

1次运算为0000-0011=1101结果为1010,产生进位,也没有产生溢出!

1次运算为1101-0100=1000结果为1010,没有产生进位,也没有产生溢出!

溢出为带符号位的数相加减,若结果超出范围则为溢出!

否则不是溢出!

对于加法易得以上结果!

对于减法它的输入、输出借位为相反的,即为高电平时,数值为0;当为低电平时,数着为1;

用以上的规则易得结果!