《数字电子技术》复习题.docx

《《数字电子技术》复习题.docx》由会员分享,可在线阅读,更多相关《《数字电子技术》复习题.docx(11页珍藏版)》请在冰豆网上搜索。

《数字电子技术》复习题

《数字电子技术》复习题

一、填空题

1、(110111)2=()16=()10=()8421BCD

2、(39.45)10=()2=()16

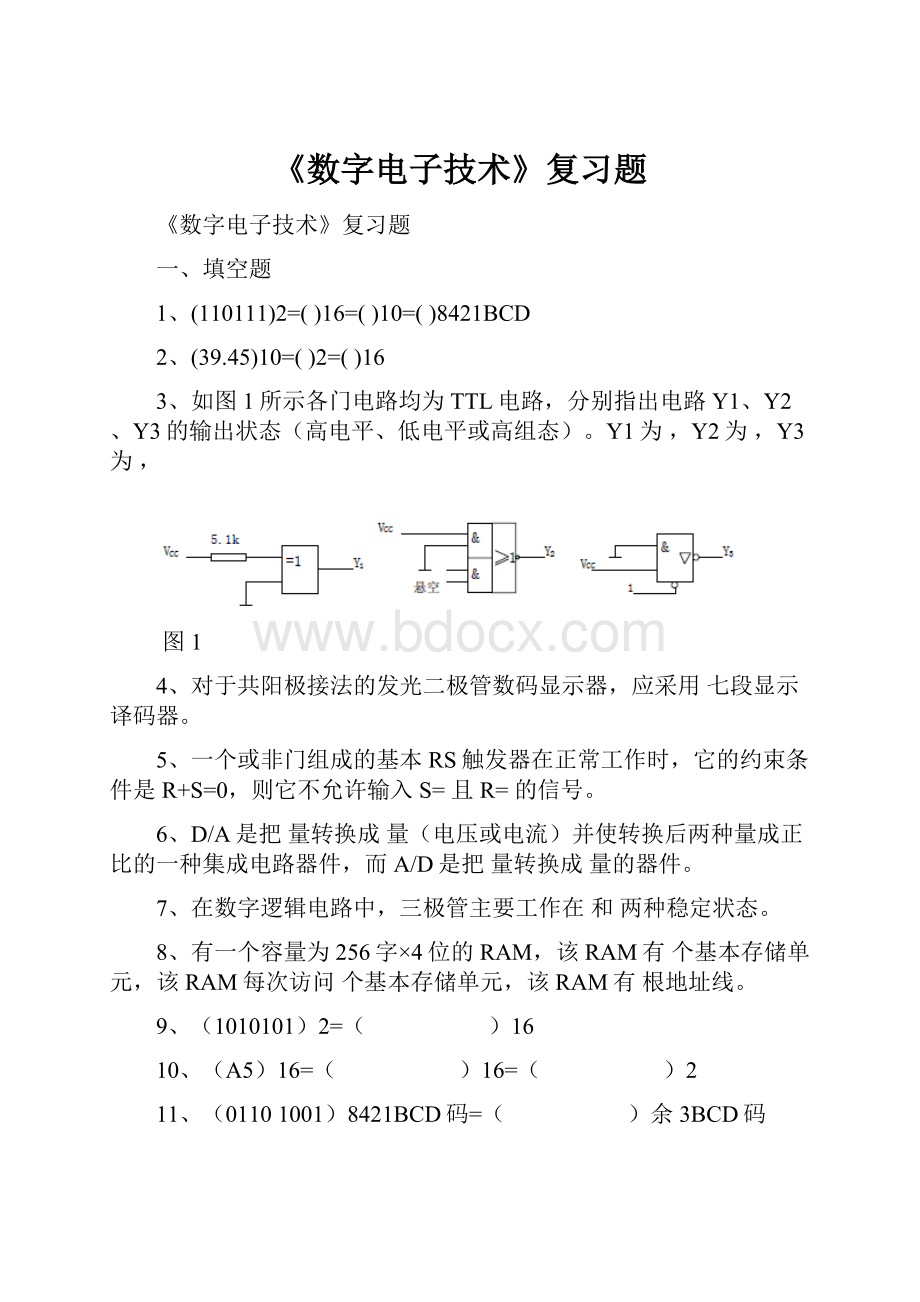

3、如图1所示各门电路均为TTL电路,分别指出电路Y1、Y2、Y3的输出状态(高电平、低电平或高组态)。

Y1为,Y2为,Y3为,

图1

4、对于共阳极接法的发光二极管数码显示器,应采用七段显示译码器。

5、一个或非门组成的基本RS触发器在正常工作时,它的约束条件是R+S=0,则它不允许输入S=且R=的信号。

6、D/A是把量转换成量(电压或电流)并使转换后两种量成正比的一种集成电路器件,而A/D是把量转换成量的器件。

7、在数字逻辑电路中,三极管主要工作在和两种稳定状态。

8、有一个容量为256字×4位的RAM,该RAM有个基本存储单元,该RAM每次访问个基本存储单元,该RAM有根地址线。

9、(1010101)2=( )16

10、(A5)16=( )16=( )2

11、(01101001)8421BCD码=( )余3BCD码

12、写出下列逻辑函数电路的输出逻辑函数表达式:

L1= ;

L2=

13、若各门电路的输入均为A和B,且A=0,B=1;则与门的输出为( ),与非门的输出为( ),或门的输出为( ),异或门的输出为( ),同或门的输出为( )。

14、触发器组成的电路如图,Q1=( );Q2=( );Q3=( );

Q4=( );

15、由或非门组成的基本RS触发器的输入信号R和S不得同时为( ),而由与非门组成的基本RS触发器的输入信号

和

不得同时为( );否则他们的状态将( )。

16、二极管具有( )特性,它的两个重要参数IS称为( ),tre称为反向恢复时间。

17、施密特触发器是一种电平触发的双稳态电路,电路两个稳态之间的翻转都取决于触发电平值。

从第一个稳态翻转到第二个稳态和从第二个稳态翻转到第一个稳态的触发电平不同,其差值称为。

施密特触发器的电压传输特性具有滞回特性的曲线,利用滞回特性可以实现、和幅值鉴别等。

18、(11010011)2=( )10=( )8421BCD码

19、(5CE)16=( )2

20、一个或非门组成的基本RS触发器在正常工作时,它的约束条件是R+S=0,则它不允许输入S=且R=的信号。

21、D/A是把量转换成量(电压或电流)并使转换后两种量成正比的一种集成电路器件,而A/D是把量转换成量的器件。

22、有一个容量为256字×4位的RAM,该RAM有个基本存储单元,该RAM每次访问个基本存储单元,该RAM有根地址线。

23、若各门电路的输入均为A和B,且A=0,B=1;则与门的输出为( ),与非门的输出为( ),或门的输出为( ),异或门的输出为( ),同或门的输出为( )。

二、选择题

1、在何种输入情况下,“与非”运算的结果是逻辑0。

()

A.全部输入是0B.任意输入是0C.仅一输入是0D.全部输入是1

2、以下电路中常用于线与的门电路是()

A.TTL门B.集电极开路门C.异或门D.CMOS与非门

3、以下各电路中,可以作为定时器用的电路()。

A.多谐振动器B.单稳态触发器C.施密特触发器D.石英晶体多谐振动器

4、欲使D触发器按Qn+1=1工作,应使输入D为()。

A.0B.1C.QD.Q反

5、在下列逻辑电路中,不是组合逻辑电路的有().

A.译码器B.编码器C.全加器D.寄存器

6、同步计数器和异步计数器比较,同步计数器的显著优点是()

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟CP控制

7、8位移位寄存器,串行输入时经多少个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.8

8、随机存取存储器RAM中的内容,当电源断掉后又接通,存储器中的内容()。

A.全部改变B.全部为1C.不确定D.保持不变

9、以下代码中为相邻两个码字之间只有一位码有差异的是()。

A.8421BCD码B.自然二进制码C.余3码D.格林吗

10、一个容量为1K*8的存储器有多少个存储单元()。

A.8B.1024C.1000D.8192

11、在不影响逻辑功能的情况下,TTL与非门的多余端可()。

A.接高电平B.接低电平 C.悬空D.不确定

12、在不影响逻辑功能的情况下,CMOS或非门的多余端可()。

A.接高电平B.接低电平 C.悬空D.不确定

13、能够通过并联输出端实现线与的门电路是()。

A.集电极开路门B.普通与非门C.三态门D.异或门

14、由四个触发器构成十进制计数器,其无效状态有()。

A.四个B.五个C.六个D.七个

15、选择一个电路分别完成下列功能。

现有电路:

A.施密特触发器B.单稳态触发器 C.多谐振动器D.触发器

(1)欲存储二进制代码,应采取( )。

(2)欲将三角波转换成矩形波,应采取( )。

(3)欲从幅度不等的脉冲信号中挑出幅度大于某一确定值的信号,并将其整形成标准幅度的脉冲信号,应采取()。

(4)欲将幅度不等、宽度也不等的脉冲信号整形成标准幅度、标准宽度的脉冲信号,应采取( )。

(5)欲将输入的时钟脉冲上升沿延迟一定的时间间隔,应采取( )。

(6)欲获得一个数字系统的时钟源,应采取( )。

16、逻辑函数

的最简式为()

A.

B.B C.0 D.1

17、以下电路中常用于线与的门电路是()

A.TTL门B.集电极开路门C.异或门D.CMOS与非门

18、欲使D触发器按Qn+1=1工作,应使输入D为()。

A.0B.1C.QD.Q反

19、在下列逻辑电路中,不是组合逻辑电路的有().

A.译码器B.编码器C.全加器D.寄存器

20、以下代码中为相邻两个码字之间只有一位码有差异的是()。

A.8421BCD码B.自然二进制码C.余3码D.格林吗

21、由四个触发器构成十进制计数器,其无效状态有()。

A.四个B.五个C.六个D.七个

22、四变量逻辑函数F(ABCD)的最小项m8为()

A.ABC

B.

BC

C.A

D.ABCD

23、555定时器构成施密特触发器时,其回差电压为()

A.Vcc/3B.Vcc/2C.2Vcc/3D.Vcc

24、已知函数F=AB+

,其最简与或式为()

A.AB+CB.

C.

D.AB+D

25、由与非门构成的基本RS触发器,要使Qn+1=Qn,则输入信号应为()

A.SD=RD=1B.SD=RD=0C.SD=1,RD=0D.SD=0,RD=1

三、名词解释

1.竞争冒险现象

2.最简与或表达式

3.D/A转换器的分辨率

4.单稳态触发器

5.时序逻辑电路

6.半加

7.组合逻辑电路

8.高电平噪声容限

9.三态输出门

10.正逻辑

11.时序逻辑电路

12.全加

13.单稳态触发器

14.负逻辑

15.三态输出门

四、简答题

1、将逻辑函数

展开成最小项之和的形式。

2、用公式法化简函数

为最简与或表达式。

3、现有JK触发器和非门电路,请将JK触发器转换成D触发器。

4、填写SR触发器的状态表。

写出约束条件表达式。

a)

5、分析

是否存在冒险现象,如何消除冒险。

6、用卡诺图化简函数表达式:

7、根据下列逻辑电路图写出逻辑函数表达式,填写卡诺图,列出真值表和逻辑函数最小项表达式。

i.

8、用代数法化简

为最简与或式。

9、已知逻辑函数

用卡诺图化简为最简与或式。

10、简述由真值表写函数表达式的步骤。

11、画出用D触发器和异或门实现的T触发器。

12、已知上升沿触发的JK触发器的输入端JK的波形,画出Q端的波形。

设触发器初态为0。

13、分析电路,说明是几进制计数器。

14、现有JK触发器和非门电路,请将JK触发器转换成D触发器。

15、用卡诺图化简函数表达式:

16、简述由真值表写函数表达式的步骤。

17、已知D触发器,画出在CP和D作用下,输出端Q的波形,设初态为0。

18、根据下列逻辑电路图写出逻辑函数表达式,填写卡诺图,列出真值表和逻辑函数最小项表达式。

五、其他题型(论述题、案例(阅读)分析题、计算题、证明题、填图题等)

1、用两块74LS160通过同步反馈预置数法,把它接成24进制计数器,画出它的连线图。

2、为提高报警信号的可靠性,在有关部位安置了3个同类型的危险报警器A、B、C,只有当3个危险报警器中至少有两个指示危险时,才实现报警操作F。

试列出真值表,写出逻辑表达式并化简,并画出具有该功能的逻辑电路。

3、设计一个三人表决逻辑电路,要求:

三人A、B、C各控制一个按键,按下为“1”,不按为“0”。

多数按下为通过。

通过时L=1,不通过L=0。

用与非门实现。

4、时序电路如图,写出

(1)驱动方程;

(2)状态方程;(3)列状态表;(4)画状态图。

5、组合逻辑电路输入A、B、C和输出L0、L1的波形如图,写出最简与或表达式。

6、用两块74LS160通过同步反馈预置数法,把它接成24进制计数器,画出它的连线图。