半导体制造工艺教案.docx

《半导体制造工艺教案.docx》由会员分享,可在线阅读,更多相关《半导体制造工艺教案.docx(14页珍藏版)》请在冰豆网上搜索。

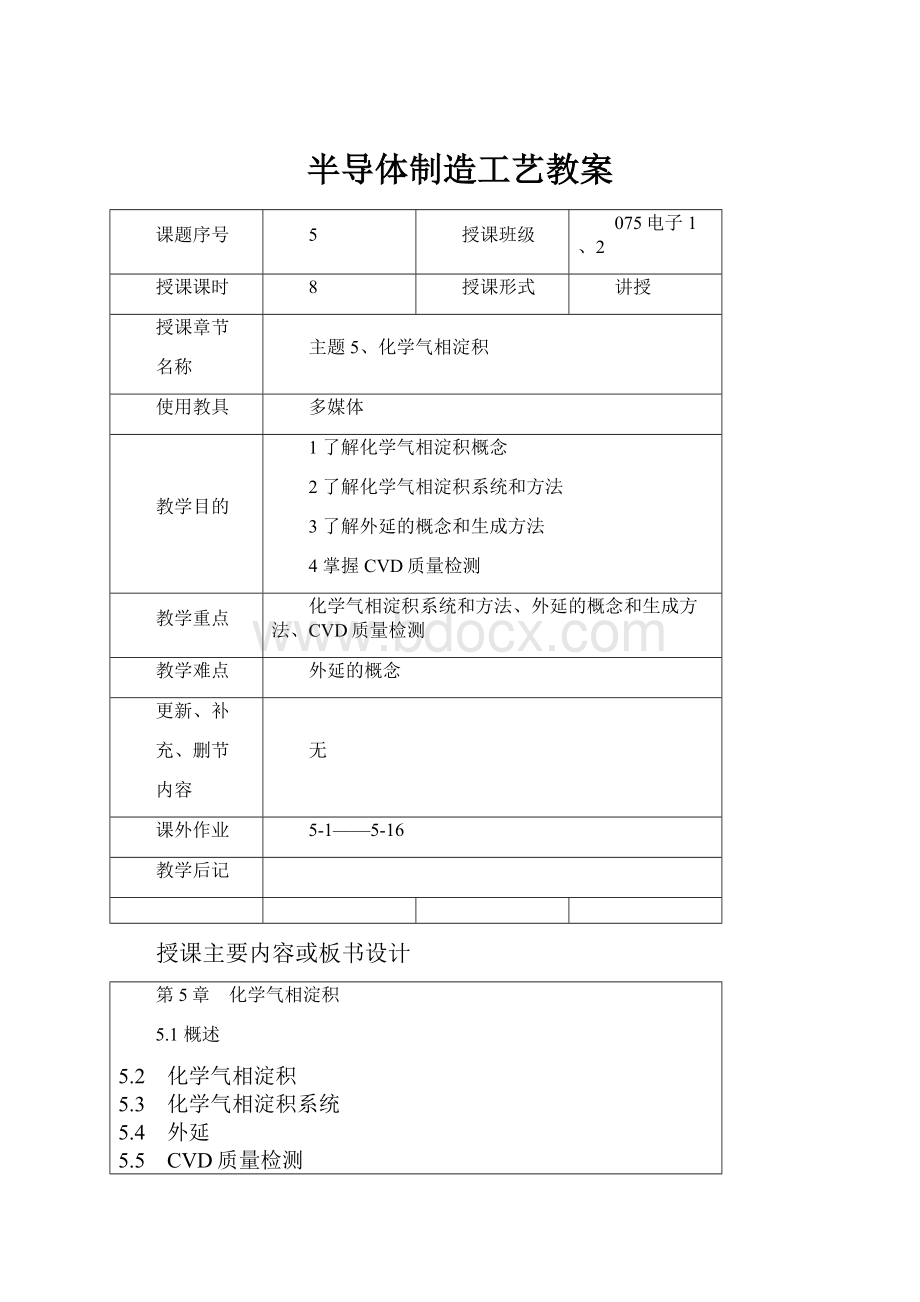

半导体制造工艺教案

课题序号

5

授课班级

075电子1、2

授课课时

8

授课形式

讲授

授课章节

名称

主题5、化学气相淀积

使用教具

多媒体

教学目的

1了解化学气相淀积概念

2了解化学气相淀积系统和方法

3了解外延的概念和生成方法

4掌握CVD质量检测

教学重点

化学气相淀积系统和方法、外延的概念和生成方法、CVD质量检测

教学难点

外延的概念

更新、补

充、删节

内容

无

课外作业

5-1——5-16

教学后记

授课主要内容或板书设计

第5章 化学气相淀积

5.1概述

5.2 化学气相淀积

5.3 化学气相淀积系统

5.4 外延

5.5 CVD质量检测

课堂教学安排

教学过程

主要教学内容及步骤

5.1引言

5.1.1 薄膜淀积的概念

所谓薄膜,是指一种在硅衬底上生长的薄固体物质。

薄膜与硅片表面紧密结合,在硅片加工中,通常描述薄膜厚度的单位是纳米(nm)。

半导体制造中的薄膜淀积是指在硅片衬底上增加一层均匀薄膜的工艺。

在硅片衬底上淀积薄膜有多种技术,主要的淀积技术有化学气相淀积(CVD)和物理气相淀积(PVD),其他的淀积技术有电镀法、旋涂法和分子束外延法。

化学气相淀积(CVD)是通过混合气体的化学反应生成固体反应物并使其淀积在硅片表面形成薄膜的工艺。

而物理气相淀积(PVD)是不需通过化学反应,直接把现有的固体材料转移至硅片表面形成薄膜的工艺。

电镀法是制备铜薄膜时主要采用的淀积技术。

旋涂法采用的设备是标准的旋转涂胶机,比CVD工艺更经济,通常用于制备低k(k指介电常数)绝缘介质膜。

分子束外延法是一种制备硅外延层的较先进的淀积技术。

5.1.2常用的薄膜材料 在半导体制造中所包含的薄膜材料种类很多,早期的芯片大约含有数十种,而随着集成电路结构和性能的发展,芯片中薄膜材料种类也越来越多,如图5⁃1所示,这些薄膜材料在器件中都起到了非常重要的作用。

总的来说,薄膜材料的种类可分为金属薄膜层、绝缘薄膜层和半导体薄膜层三种。

图5-1 早期和现代MOS结构中的各层薄膜

1)金属薄膜层在半导体制造中的应用主要是制备金属互连线。

2)常见的绝缘薄膜材料有二氧化硅(SiO2)、掺杂二氧化硅(如PSG、BPSG)、氮化硅(Si3N4)等。

3)半导体薄膜材料主要有多晶硅、外延硅层等。

5.1.3半导体制造中对薄膜的要求 在图5⁃1中给出了制作一个早期NMOS管所需的淀积层。

图中器件的特征尺寸远大于。

由于特征高度的变化,硅片上的各层薄膜并不平坦,质量不高。

这成为超大规模集成电路时代所需的多层金属、高密度芯片制造的限制因素。

随着硅片加工向更高的芯片密度发展,特征尺寸缩小到0.18μm甚至更小,而且需要用到6层甚至更多层金属来做连接。

这使得在硅片上可靠地沉积符合要求的薄膜材料至关重要。

1.良好的台阶覆盖能力

2.填充高的深宽比间隙的能力

图5-2 薄膜的台阶覆盖

图5-3 高深宽比通孔填充效果比较

3.良好的厚度均匀性

4.高纯度和高密度

5.高度的结构完整性和低的膜应力

图5-4 薄膜中晶粒的成核与生长过程

图5-5 膜应力导致硅片衬底发生变形

6.对衬底材料或下层膜良好的粘附性

5.2 化学气相淀积

5.2.1 化学气相淀积的概念

化学气相淀积(CVD)是通过混合气体的化学反应生成固体反应物并使其淀积在硅片表面形成薄膜的工艺。

反应产生的其他副产物为挥发性气体,离开硅片表面并被抽出反应腔。

硅片表面及其邻近的区域被加热以向反应系统提供附加的能量。

5.2.2 化学气相淀积的原理

化学气相淀积工艺的反应在炉管反应腔内进行,同时必须使化学反应发生在硅片表面或者非常接近表面的区域(表面催化),这样可以生成高质量的薄膜。

而如果反应发生在距离硅片表面较远的地方,会导致反应物粘附性差、密度低和缺陷多,这是必须避免的。

例如:

利用硅烷和氧气经过化学反应淀积SiO2膜,其反应的生成物SiO2淀积在硅片表面,同时生成了气态的副产物氢气,氢气经排气系统排出炉管外。

反应式如下:

图5-6 CVD的主要反应过程

①气态反应剂被输送至反应腔,以平流形式向出口流动。

②反应剂从主气流区以扩散方式通过边界层到达硅片表面。

③反应剂被吸附到硅表面。

④被吸附到硅表面的原子(分子)在衬底表面发生化学反应,生成固态物质淀积成膜。

⑤反应产生的气态副产物和未反应的反应剂离开衬底,排出系统。

5.3 化学气相淀积系统

5.3.1 APCVD

常压化学气相淀积(APCVD)是指在一个大气压下进行的一种化学气相淀积的方法,这是最初采用的CVD方法。

这种方法工艺系统简单,工艺温度是400~600℃,反应速度和淀积速度快(淀积速度可达1000nm/min),但其淀积的薄膜均匀性较差,气体消耗量大,且台阶覆盖能力差,因此APCVD常被用于淀积相对较厚的介质层(如PSG或BPSG等)。

图5-7 APCVD

1.SiO2的淀积

1)硅烷(SiH4)法是用O2氧化SiH4来淀积SiO2。

2)TEOS-O3法是使用正硅酸乙酯(TEOS)与O3反应淀积SiO2。

2.掺杂SiO2的

图5-8 PSG回流后表面平坦化

图5-9 气体分子的运动轨迹

图5-10 LPCVD

1.SiO2的淀积

2.Si3N4淀积

3.多晶硅淀积

图5-11 多晶硅栅自对准工艺示意图

4.典型的LPCVD工艺设备操作

1)做好淀积前的准备工作,包括按流程卡确认程序、工艺、设备及硅片数量。

2)硅片清洗。

3)选择程序。

4)系统充气。

5)装片。

6)按“START”键,设备将按设定的程序进炉。

7)程序结束,自动出舟,同时发出报警声,此时按面板上的“ACK”键,报警声消除。

8)经10min冷却后,取下正片或测试片,放入传递盒待检验和测试。

5.3.3 等离子体辅助CVD

等离子体又叫做电浆,是被电离后的气体,即以离子态形式存在的气体(正离子和电子组成的混合物)。

它广泛存在于宇宙中,常被视为是除固、液、气之外,物质存在的第四态。

在自然界里,火焰、闪电、太阳等都是等离子体。

等离子体有以下两个特点:

①等离子体呈现出高度不稳定态,有很强的化学活性。

等离子体辅助CVD就是利用了这个特点。

②等离子体是一种很好的导电体,利用经过设计的磁场可以捕捉、移动和加速等离子体。

这两个特点在后面的等离子体刻蚀工艺中得到了很好的利用。

等离子体产生方法有辉光放电、射频放电和电晕放电等。

1)有更低的工艺温度(250~450℃)。

2)对高的深宽比间隙有好的填充能力(用高密度等离子体CVD)。

3)淀积的膜对硅片有优良的粘附能力。

4)有较高的淀积速率。

5)有较少的针孔和空洞,因而有较高的膜密度。

6)腔体可利用等离子体清洗。

1.等离子体增强CVD

图5-12 PECVD的反应腔示意图

1)清洗。

2)装片。

3)选择菜单。

4)卸片。

5)测量。

2.高密度等离子体CVD

(1)同步淀积和刻蚀 HDPCVD的一个突破创新之处就在于在同一个反应腔中同步地进行淀积和刻蚀的工艺。

图5-13 同步淀积和刻蚀

(2)浅槽隔离(STI)对于特征尺寸在0.35μm以上的器件,通常采用局部氧化(LOCOS)技术来隔离,如图5-14b所示。

图5-14 两MOS器件间的隔离

3.多腔集成CVD设备

图5-15 多腔集成CVD设备

5.4外延

5.4.1 外延的概念、作用、原理

外延(EPI)工艺是指在单晶衬底上生长一层跟衬底具有相同晶向的单晶薄膜材料,该单晶薄膜层称为外延层。

外延层除晶向必须与衬底一致外,其单晶材料、掺杂类型、掺杂浓度和厚度都可以按设计要求与衬底不同。

若在硅衬底上生长单晶硅外延层称为同质外延层;若在硅衬底上生长锗外延层称为异质外延层;若在重掺杂衬底上生长轻掺杂外延层称为正外延;在轻掺杂衬底上生长的重掺杂外延层称为反外延。

外延层的掺杂厚度、浓度、轮廓等属性容易控制而不受硅衬底影响,因此这为设计者在优化器件性能方面提供了很大的灵活性。

图5-16 外延层的用途

5.4.2 外延生长方法

外延生长有两个重要条件:

一是必须去除表面的自然氧化层及硅片表面的杂质。

如果表面有一层薄的二氧化硅、非晶态层表面或污染物,则会影响外延生长原子的正确定位,结果导致薄膜结构为多晶硅或形成缺陷较多的单晶。

二是衬底的表面温度足够高(气相外延时),只有在高温的情形下,淀积在衬底上的硅原子才有足够的动能移动到适当的位置与衬底形成一致晶向的单晶,而低温淀积形成的薄膜为多晶。

1.气相外延

图5-17 卧式、立式和桶式反应炉示意图

1)清洁。

2)换气。

3)装炉。

4)原位抛光。

5)外延生长。

6)取片。

2.分子束外延

图5-18 MBE系统设备示意图

1)超高真空工艺可以制备高质量(良好的均匀性、纯度和较低的晶体缺陷等)单晶薄膜。

2)低温生长,减少自掺杂。

3)薄膜厚度、成分和浓度可严格控制,可实现厚度在原子层级别的超薄薄膜沉积。

4)系统加入薄膜生长质量分析仪,可进行原位观察,实时反馈以控制生长。

5.4.3 硅外延工艺

1.双极型晶体管中外延层的应用

图5-19 制作双极型晶体管的工艺流程

1)P型硅衬底准备。

2)埋层扩散。

3)外延层的形成。

4)制作隔离区。

5)制作基区。

6)制作发射区。

7)制作引线电极。

2.绝缘硅技术

图5-20 SOI

图5-21 SOI技术使器件占用芯片的面积减小

5.5 CVD质量检测

1.膜厚

表5-1 比色法薄膜颜色表

2.折射率

3.台阶覆盖率

图5-22 椭偏仪测试示意图

4.均匀性

图5-23 硅片中测试点的选取