华中科技大学数字逻辑实验小设计.docx

《华中科技大学数字逻辑实验小设计.docx》由会员分享,可在线阅读,更多相关《华中科技大学数字逻辑实验小设计.docx(12页珍藏版)》请在冰豆网上搜索。

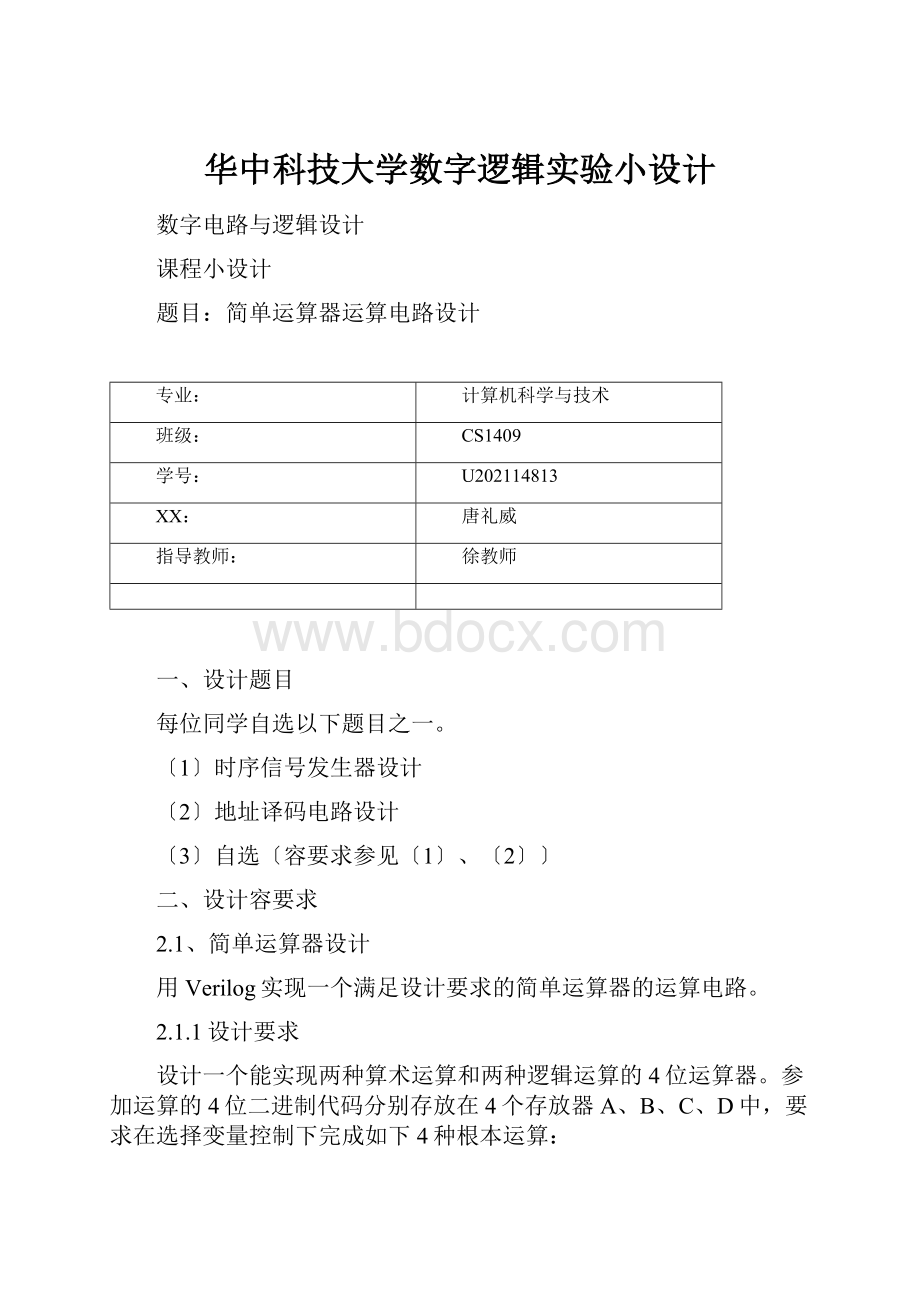

华中科技大学数字逻辑实验小设计

数字电路与逻辑设计

课程小设计

题目:

简单运算器运算电路设计

专业:

计算机科学与技术

班级:

CS1409

学号:

U202114813

XX:

唐礼威

指导教师:

徐教师

一、设计题目

每位同学自选以下题目之一。

〔1〕时序信号发生器设计

〔2〕地址译码电路设计

〔3〕自选〔容要求参见〔1〕、〔2〕〕

二、设计容要求

2.1、简单运算器设计

用Verilog实现一个满足设计要求的简单运算器的运算电路。

2.1.1设计要求

设计一个能实现两种算术运算和两种逻辑运算的4位运算器。

参加运算的4位二进制代码分别存放在4个存放器A、B、C、D中,要求在选择变量控制下完成如下4种根本运算:

〔1〕实现A加B,显示运算结果并将结果送存放器A;

〔2〕实现A减B,显示运算结果并将结果送存放器B;

〔3〕实现A与C,显示运算结果并将结果送存放器C;

〔4〕实现A异或D,显示运算结果并将结果送存放器D。

2.1.2功能描述

根据设计要求,为了区分4种不同的运算,需设置2个运算控制变量。

设运算控制变量为S1和SO,可列出运算器的功能,如表1所示。

根据功能描述可得出运算器的构造框图,如图1所示。

整个电路可由传输控制电路、运算电路、显示电路3局部组成。

S1

S0

功能

说明

0

0

A+B→A

A加B,结果送至A

0

1

A-B→A

A减B,结果送至A

1

0

A·B→C

A与C,结果送至C

1

1

A⊕B→D

A异或D,结果送至D

简单运算功能说明表

运算器的构造框图

由简单运算器的构造图可知其由传输控制电路、运算电路和运算结果显示电路三个大局部构成,其中运算电路又由算术运算电路、逻辑运算电路构成。

这次设计主要是利用Verilog语言设计运算器中运算电路局部。

2.1.3电路设计

运算电路的逻辑电路图如下:

由运算电路的逻辑电路图可以看出运算器中的逻辑关系,运算器主要由一片74LS283芯片和4个存放器及8个异或门和4个与门构成。

由运算电路逻辑电路图可以初步构思设计个子模块的功能。

但是仅有运算电路的逻辑电路图还不够,还需要整体运算器的逻辑电路图才能确定各个子模块的输入与输出关系。

运算电路的完整逻辑电路图如下:

可以看到运算电路逻辑图只是其中一局部,其中74LS283芯片功能为超前进位的全加器,可以将它设计为一个加法器模块。

由以上的分析,知该设计主要要解决的问题:

主模块的设计、存放器模块的设计、加法器模块的设计、仿真验证。

由此写出程序代码如下:

功能代码:

`timescale1ns/1ps

//主模块

moduleJDYS(CIN,S1,S0,CP,A,B,C,D,F);

inputCIN,S1,S0,CP;

input[3:

0]A;

input[3:

0]B;

input[3:

0]C;

input[3:

0]D;

outputreg[3:

0]F;

wire[3:

0]xnor1;

wire[3:

0]and1;

wire[3:

0]xnor2;

wire[3:

0]r1;

wire[3:

0]r2;

wire[3:

0]r3;

wire[3:

0]r4;

wire[3:

0]a;

wireaout;

parameterW=1'b1

xor(xnor1[0],r1[0],r4[0]),

xor(xnor1[1],r1[1],r4[1]),

xor(xnor1[2],r1[2],r4[2]),

xor(xnor1[3],r1[3],r4[3]);

xor(xnor2[0],r2[0],CIN),

xor(xnor2[1],r2[1],CIN),

xor(xnor2[2],r2[2],CIN),

xor(xnor2[3],r2[3],CIN);

registerX1(W,A[3],A[2],A[1],A[0],W,W,W,W,CP,r1[3],r1[2],r1[1],r1[0]),

registerX2(W,B[3],B[2],B[1],B[0],W,W,W,W,CP,r2[3],r2[2],r2[1],r2[0]),

registerX3(W,C[3],C[2],C[1],C[0],W,W,W,W,CP,r3[3],r3[2],r3[1],r3[0]),

registerX4(W,D[3],D[2],D[1],D[0],W,W,W,W,CP,r4[3],r4[2],r4[1],r4[0]);

addX5(CIN,r1,xnor2,a,aout);

and(and1[0],r1[0],r3[0]),

and(and1[1],r1[1],r3[1]),

and(and1[2],r1[2],r3[2]),

and(and1[3],r1[3],r3[3]);

always(*)

begin

case({S1,S0})

2'b00:

begin

F<=a;

end

2'b01:

begin

F<=a;

end

2'b10:

F<=and1;

2'b11:

F<=xnor1;

endcase

end

endmodule

//加法器模块

moduleadd(cin,x,y,z,fc);

inputcin;

input[3:

0]x;

input[3:

0]y;

outputreg[3:

0]z;

outputregfc;

reg[3:

0]c;

always(cin,x,y,z,fc)

begin

z[0]=x[0]^y[0]^cin;

c[0]=((x[0]^y[0])&cin|x[0]&y[0]);

z[1]=x[1]^y[1]^c[0];

c[1]=((x[1]^y[1])&c[0]|x[1]&y[1]);

z[2]=x[2]^y[2]^c[1];

c[2]=((x[2]^y[2])&c[1]|x[2]&y[2]);

z[3]=x[3]^y[3]^c[2];

fc=((x[3]^y[3])&c[2]|x[3]&y[3]);

end

endmodule

//存放器模块

moduleregister(FCLR,D,C,B,A,DR,DL,S1,S0,CP,Q4,Q3,Q2,Q1);

inputFCLR,D,C,B,A,DR,DL,S1,S0,CP;

outputregQ4,Q3,Q2,Q1;

parameterW=1,F=0;

initial{Q4,Q3,Q2,Q1}=4'b0000;

always(posedgeCP)

if(!

FCLR)

{Q4,Q3,Q2,Q1}=0;

elseif((~S1)&(~S0))

{Q4,Q3,Q2,Q1}<={Q4,Q3,Q2,Q1};

elseif(S1&S0)

{Q4,Q3,Q2,Q1}<={D,C,B,A};

elseif((~S1)&S0&DR)

{Q4,Q3,Q2,Q1}<={1,Q3,Q2,Q1};

elseif((~S1)&S0&(!

DR))

{Q4,Q3,Q2,Q1}<={0,Q3,Q2,Q1};

elseif(S1&(~S0)&DL)

{Q4,Q3,Q2,Q1}<={Q3,Q2,Q1,W};

elseif(S1&(~S0)&(~DL))

{Q4,Q3,Q2,Q1}<={Q3,Q2,Q1,F};

Endmodule

仿真程序

`timescale1ns/1ps

moduleJDYS_tb(

);

regCIN,S1,S0,CP;

reg[3:

0]A;

reg[3:

0]B;

reg[3:

0]C;

reg[3:

0]D;

wire[3:

0]F;

JDYSDUT(.A(A),.B(B),.C(C),.D(D),.S1(S1),.S0(S0),.CP(CP),.CIN(CIN),.F(F));

initial

begin

A=4'd12;B=4'd11;C=4'd2;D=4'd8;S1=0;S0=0;CIN=0;CP=1;

#10

S1=0;

S0=1;

CIN=1;

CP=0;

#10

S1=1;

S0=0;

#10

S1=1;

S0=1;

#10

A=4'd5;

B=4'd7;

C=4'd5;

D=4'd1;

S1=0;

S0=0;

CIN=0;

CP=1;

#10

S1=0;

S0=1;

CIN=1;

CP=0;

#10

S1=1;

S0=0;

#10

S1=1;

S0=1;

#10

A=4'd0;

B=4'd15;

C=4'd4;

D=4'd8;

S1=0;

S0=0;

CIN=0;

CP=1;

#10

S1=0;

S0=1;

CIN=1;

CP=0;

#10

S1=1;

S0=0;

#10

S1=1;

S0=1;

#10;

end

endmodule

运算电路电路图:

运算电路仿真波形图:

参考文献:

[1]欧阳星明、于俊清等.?

数字逻辑?

〔第四版〕华中科技大学,.hustp.