FPGA电子表.docx

《FPGA电子表.docx》由会员分享,可在线阅读,更多相关《FPGA电子表.docx(31页珍藏版)》请在冰豆网上搜索。

FPGA电子表

FPGA课程设计报告提纲

1.任务

设计一个电子表微控制器,并且能显示1/10秒、秒、分。

可以预设值,还可以复位清零。

学会板子上的LCD液晶显示屏,按键的使用(消抖),拨动开关。

2.目的

熟悉Sparten-3E板子,会使用它的硬件,比如板子上的LCD液晶显示屏,板子自带的按键,还有拨动开关。

利用这些硬件设计出电子表微控制器,使用按键改变1/10秒,秒,分,使用拨动开关暂停电子表,使用板子上的LCD液晶显示屏来显示时间,和通过按键改变后的时间。

熟练掌握verilog语言的使用。

3.使用环境(软件/硬件环境,设备等)

Modelsim和Xilinx-ISE-10.1

4.FPGA课程设计详细内容

4.1技术规范

电子表微控器设计技术规范

V1.0

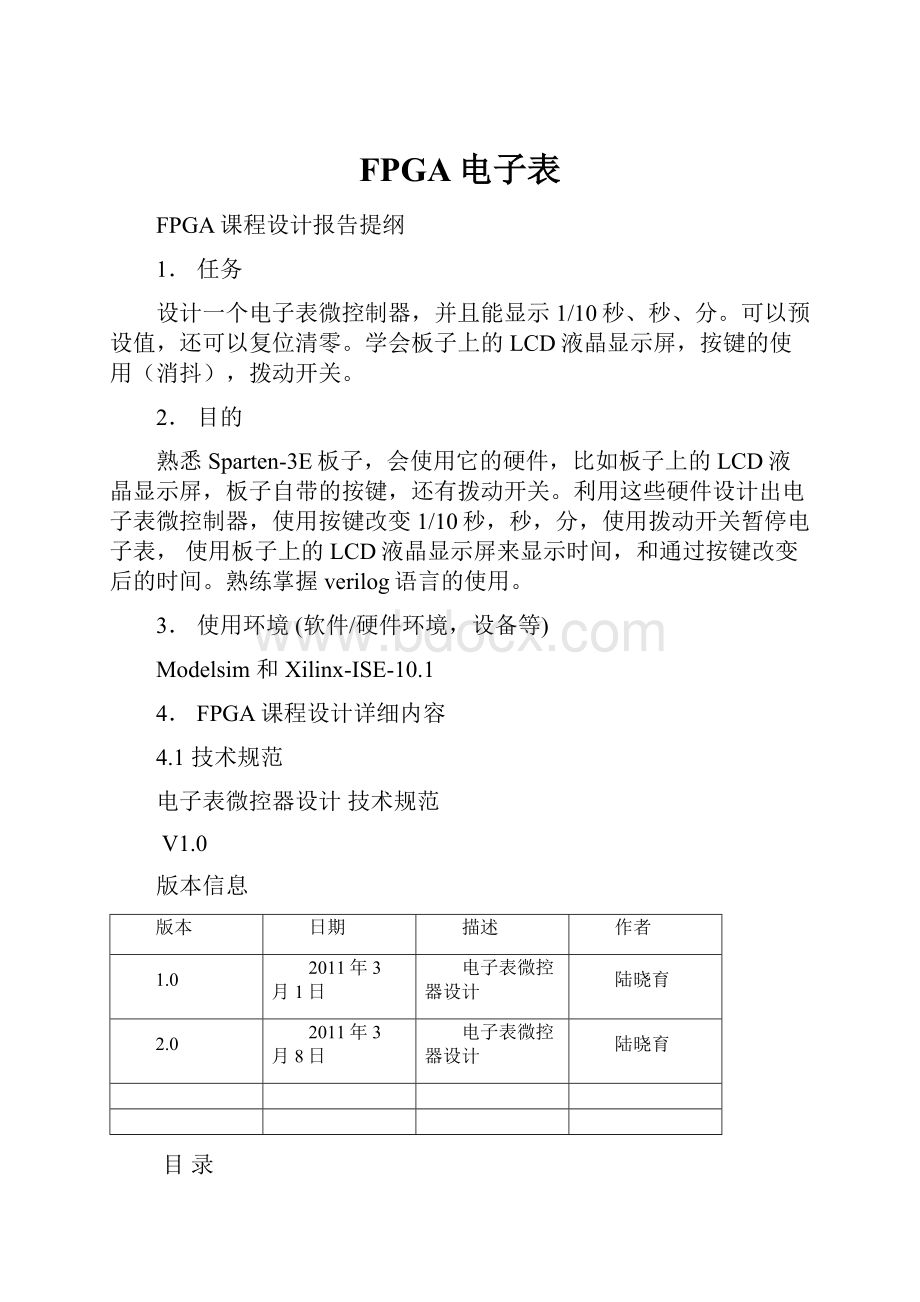

版本信息

版本

日期

描述

作者

1.0

2011年3月1日

电子表微控器设计

陆晓育

2.0

2011年3月8日

电子表微控器设计

陆晓育

目录

1总体描述

1.1功能定义

1.用FPGA开发板的拨动开关作为电子表的时间初值设置控制信号,首先设置出电子表的1/10秒,秒,分初值。

并且在LCD上显示出1/10秒,秒,分

2.使用拨动开关(Switch1)作为电子表的总控制开关,当Switch1为低电平时,才可以修改时间。

3.按键2(Button2)作为1/10秒的初值设置控制键。

4.按键3(Button3)作为秒的初值设置和修改的控制键。

5.按键4(Button4)作为分的初值设置和修改的控制键。

6.在LCD上显示修改后的时间。

7.使用Switch2作为电子表的复位,当它为低电平时,把电子表的1/10秒,秒,分清零。

1.2结构框图

1.3设计工艺

1.3应用范围

作为电子表查看时间,时间更加的精确。

还可以当做跑表使用。

2引脚描述

名称

引脚(inputoroutput)

位宽

描述

1Switch1

INPUT

1

控制初值设置,并且是修改时间的总开关,当它为低电平时,才能修改1/10秒,秒,分

2Button2

INPUT

1

当总开关开启时(为低电平),修改1/10秒

3Button3

INPUT

1

当总开关开启时(为低电平),修改秒

4Button4

INPUT

1

当总开关开启时(为低电平),修改分

5CLOCK_50MHZ

INPUT

1

产生50MHZ的晶振输出,给系统应用

6LCD_EN

OUTPUT

1

LCD的读/写操作允许控制信号,为高电平时允许读写,低电平时不允许

7LCD_RS

OUTPUT

1

寄存器选择控制信号,为低电平时写操作期间LCD的复位端

8LCD_R/W

OUTPUT

1

读写控制信号,0:

写,LCD接受数据1:

读,LCD输出数据

9DB0

OUTPUT

1

FPGA连接LCD的数据端DB4

10DB1

OUTPUT

1

FPGA连接LCD的数据端DB5

11DB2

OUTPUT

1

FPGA连接LCD的数据端DB6

12DB3

OUTPUT

1

FPGA连接LCD的数据端DB7

13reset

INPUT

1

电子表的复位端,当它为低电平时,电子时钟的1/10秒,秒,分都清零。

4功能模块描述

4.1时钟模块

1.1/10秒

秒

分

在这个模块中有1/10秒,秒,分,通过这几个时间来反映做出来的电子表,用板子里面的50MHZ产生出10HZ的分频作为1/10秒,从而进行计时。

2.Switch1:

初值设置开关(总开关):

拨动到低电平时,1/10秒,秒,分都停止,开始设置时间。

拨动到高电平时,说明时间设置完毕,时钟开始正常运行。

Button2按键1(修改1/10秒):

按一次,1/10秒加1。

Button3按键2(修改秒):

按一次,秒加1。

Button4按键3(修改分):

按一次,分加1。

4.2按键模块

这个模块完成的是按键的消抖,使用系统自带50MHZ时钟分频得到的25MHZ,再进行按键采样,人一般的反应时间在50ms左右,所以采样的计数设置为25MHZ*50ms。

4.3LCD显示模块

1.第一行显示“TIME“.

2.LCD上的第二行显示1/10秒,秒,分。

3.LCD上的第二行显示修改后的1/10秒,秒,分。

4.4时钟分频模块

使用FPGA板子中自带的50MHZ时钟分频得到10HZ(用于电子表计时),分频得到25MHZ(用于按键消抖模块时对按键采样的频率)。

5电学指标

6绝对最大范围

7建议工作条件

8其他说明

4.2设计方案

电子表微控器设计方案

V1.0

版本信息

版本

日期

描述

作者

1.0

2011年3月1日

电子表微控器设计

陆晓育

2.0

2011年3月8日

电子表微控器设计

陆晓育

目录

1概述

设计一个电子表微控制器,用FPGA开发板的拨动开关作为电子表的时间初值设置控制信号,并且使用按键改变时间(1/10秒,秒,分),LCD显示当前时间值以及修改后的时间。

2设计目标

2.1功能定义

1.用FPGA开发板的拨动开关作为电子表的时间初值设置控制信号,首先设置出电子表的1/10秒,秒,分初值。

并且在LCD上显示出1/10秒,秒,分

2.使用按键1(Switch1)作为电子表的总控制开关,当Switch1为低电平时,才可以修改时间。

3.使用reset作为电子表的复位,当它为低电平时,把电子表的1/10秒,秒,分清零。

4.按键2(Button2)作为1/10秒的初值设置控制键。

5.按键3(Button3)作为秒的初值设置和修改的控制键。

6.按键4(Button4)作为分的初值设置和修改的控制键。

7.在LCD上显示修改后的时间。

2.2接口描述

名称

引脚(inputoroutput)

位宽

描述

1Switch1

INPUT

1

控制初值设置,并且是修改时间的总开关,当它为低电平时,才能修改1/10秒,秒,分

2Button2

INPUT

1

当总开关开启时(为低电平),修改1/10秒

3Button3

INPUT

1

当总开关开启时(为低电平),修改秒

4Button4

INPUT

1

当总开关开启时(为低电平),修改分

5CLOCK_50MHZ

INPUT

1

产生50MHZ的晶振输出,给系统应用

6LCD_EN

OUTPUT

1

LCD的读/写操作允许控制信号,为高电平时允许读写,低电平时不允许

7LCD_RS

OUTPUT

1

寄存器选择控制信号,为低电平时写操作期间LCD的复位端

8LCD_R/W

OUTPUT

1

读写控制信号,0:

写,LCD接受数据1:

读,LCD输出数据

9LCD_DB0

OUTPUT

1

FPGA连接LCD的数据端DB4

10LCD_DB1

OUTPUT

1

FPGA连接LCD的数据端DB5

11LCD_DB2

OUTPUT

1

FPGA连接LCD的数据端DB6

12LCD_DB3

OUTPUT

1

FPGA连接LCD的数据端DB7

13reset

INPUT

1

电子表的复位端,当它为低电平时,电子时钟的1/10秒,秒,分都清零。

端口定义:

端口名称

引脚定义

1Switch1

N17

2Button2

H13

3Button3

K17

4Button4

D18

5CLOCK_50MHZ

C9

6LCD_EN

M18

7LCD_RS

L18

8LCD_R/W

L17

9LCD_DB0

R15

10LCD_DB1

R16

11LCD_DB2

P17

12LCD_DB3

M15

13reset

H18

2.3引脚时序

Clock

Switch1

Button2

Button3

Button4

LCD_EN

LCD_RS

LCD_R/W

LCD_DB[0:

3]

3顶层方案设计

3.1顶层结构框图

3.2顶层模块划分

1.分频模块

使用FPGA板子中自带的50MHZ时钟分频得到10HZ(用于电子表计时1/10秒),分频得到25MHZ(用于按键消抖模块时对按键采样的频率)。

2.按键模块

这个模块完成的是按键的消抖,使用系统自带50MHZ时钟分频得到的25MHZ,再进行按键采样,人一般的反应时间在50ms左右,所以采样的计数设置为25MHZ*50ms。

Switch1:

用它作为时钟的总开关,当它为低电平有效时,开始设置电子表的初值。

reset:

使用reset作为电子表的复位,当它为低电平时,把电子表的1/10秒,秒,分清零。

Button2:

作为1/10秒的初值设置控制键(每按键一次,1/10秒加1,到9时在返还到0)。

Button3:

作为秒的初值设置和修改控制键(每按键一次,秒加1,累加到59时,返回到0)。

Button4:

作为分的初值设置和修改控制键(每按键一次,分加1,累加到59时,)。

3.时钟模块

利用FPGA板子当中晶振产生的50MHZ分频得到0.1秒,从而可以得到秒,分。

4.LCD液晶显示模块

显示初值设定的时间,并且可以显示修改后的时间。

3.3子模块说明

1.按键模块:

Switch1:

初值设置开关(总开关):

拨动到低电平时,1/10秒,秒,分都停止,开始设置时间。

拨动到高电平时,说明时间设置完毕,时钟开始正常运行。

Button2按键1(修改1/10秒):

按一次,1/10秒加1。

Button3按键2(修改秒):

按一次,秒加1。

Button4按键3(修改分):

按一次,分加1。

2.时钟模块:

1/10秒

秒

分

在这个模块中有1/10秒,秒,分,通过这几个时间来反映做出来的电子表,用板子里面的50MHZ产生出10HZ的分频。

3.LCD液晶显示模块

显示1/10秒,秒,分

显示修改后的1/10秒,秒,分

4.按键消抖模块

这个模块完成的是按键的消抖,使用系统自带50MHZ时钟分频得到的25MHZ,再进行按键采样,人一般的反应时间在50ms左右,所以采样的计数设置为25MHZ*50ms。

4子模块详细设计

4.1键盘模块设计

Switch1:

用它作为时钟的总开关,当它高电平

(1)有效时,开始设置电子表的初值。

Reset:

作为电子表的复位,当它为低电平时,把电子表的1/10秒,秒,分清零。

Button2:

作为1/10秒的初值设置控制键(每按键一次,1/10秒加1,到9时在返还到0并且向秒进位1)。

Button3:

作为秒的初值设置和修改控制键(每按键一次,秒加1,累加到59时,返回到0并且向分进位1)。

Button4:

作为分的初值设置和修改控制键(每按键一次,分加1,累加到59时返回到0)。

4.2时钟模块设计

1.利用FPGA板子中晶振产生的50MHZ频率,把它分频成0.1秒即10HZ。

2.上面分频得到的0.1秒就是电子表的最小时间单位,当1/10秒从0开始走到9时,向秒进位1的同时,从9跳转到0,重新开始从零计时。

3.秒从0开始计数,当从1/10秒得到进位时,秒加1,直到计数计到59时,向分进位1的同时,从59跳转到0,重新开始从零计时。

4.分从0开始计数,当从秒得到进位时,分加1,直到计数计到59时,跳转到0,从零开始重新计时。

4.3LCD液晶显示模块

首先显示初值1/10秒,秒,分,如果有修改,那么LCD液晶显示屏显示出修改后的时间值

4.3功能验证方案

moduletextdianclock;

regclk1,reset;

wire[7:

0]fen,miao;

wire[3:

0]time_one_ten;

dianclockdc(reset,clk1,fen,miao,time_one_ten);

initial

begin

clk1=0;

reset=0;

end

always#5clk1=~clk1;

initial

begin

#15reset=1;

end

endmodule

4.4电路设计源代码,功能仿真激励源代码及功能仿真结果报告

ModuleTOP(CLK_50MHZ,reset,Switch1,Button2,Button3,Button4,LCD_RS,LCD_DB,LCD_RW,LCD_E);

inputCLK_50MHZ;

inputreset;

inputSwitch1,Button2,Button3,Button4;

//inputSwitch1,Button2,Button3,Button4;

outputLCD_RS,LCD_RW,LCD_E;

output[3:

0]LCD_DB;

//wire[3:

0]DATA;

wireclk1,clk2;

wire[7:

0]fen,miao;

wire[3:

0]time_one_ten;

wireButton6,Button7,Button8;

fenpinfp(.CLK_50MHZ(CLK_50MHZ),.clk1(clk1),.clk2(clk2));

//按键消抖

clearjittercj1(.clk2(clk2),.reset(reset),.Button_in(Button2),.Button_out(Button6));

clearjittercj2(.clk2(clk2),.reset(reset),.Button_in(Button3),.Button_out(Button7));

clearjittercj3(.clk2(clk2),.reset(reset),.Button_in(Button4),.Button_out(Button8));

//时钟计时

dianclockdc(.reset(reset),.clk1(clk1),.Button5(Switch1),

.Button6(Button6),.Button7(Button7),.Button8(Button8),

.fen(fen),.miao(miao),.time_one_ten(time_one_ten)

);

//LCD显示

LCDlc(.CLK_50MHZ(CLK_50MHZ),.LCD_RS(LCD_RS),.LCD_DB(LCD_DB),

.LCD_RW(LCD_RW),.LCD_E(LCD_E),

.fen(fen),.miao(miao),.time_one_ten(time_one_ten));

endmodule

modulefenpin(CLK_50MHZ,clk1,clk2);

inputCLK_50MHZ;

outputclk1;

outputclk2;

regclk1;

regclk2;

reg[22:

0]count;

reg[1:

0]count2;

always@(posedgeCLK_50MHZ)//fenpento10hz

begin

if(count==23'h4C4B40)

begin

count=0;

clk1=1;

end

else

begin

clk1=0;

count=count+1;

end

end

always@(posedgeCLK_50MHZ)//fenpento25mhz

begin

if(count2==2'b10)

begin

count2=0;

clk2=1;

end

else

begin

clk2=0;

count2=count2+1;

end

end

endmodule

moduledianclock(reset,clk1,Button5,Button6,Button7,Button8,

fen,miao,time_one_ten);

inputclk1,reset;

inputButton5,Button6,Button7,Button8;

output[7:

0]fen,miao;

output[3:

0]time_one_ten;

reg[7:

0]fen,miao;

reg[3:

0]time_one_ten;

wireclk;

assignclk=Button5&&clk1||Button6||Button7||Button8;

//**timecountmodule**//

always@(posedgeclkornegedgereset)

begin

if(!

reset)begin

time_one_ten=2'b00;fen=2'b00;miao=2'b00;

end

else

begin

if(fen==8'b01011001&&miao==8'b01011001&&time_one_ten==4'b1001)//59:

59:

9

begin

time_one_ten=0;fen=0;miao=0;

end

elseif(miao==8'b01011001&&time_one_ten==4'b1001)//##:

59:

9

begin

if(fen[3]&&fen[0])//#9:

59:

9

begin

fen=fen+7;

miao=0;time_one_ten=0;

end

else

begin//##:

59:

9

fen=fen+1;

miao=0;time_one_ten=0;

end

end

elseif(time_one_ten==4'b1001)//##:

##:

9

begin

if(miao[3]&&miao[0])//##:

#9:

9

begin

time_one_ten=0;

miao=miao+7;

end

else

begin

miao=miao+1;

time_one_ten=0;

end

end

//else

//time_one_ten=time_one_ten+1;//##:

##:

#

elseif(Button8)//correctthefen

begin

if(fen==8'b01011001&&miao==8'b01011001&&time_one_ten==4'b1001)//59:

##:

#

begin

fen=0;

end

elseif(miao==8'b01011001&&time_one_ten==4'b1001)//##:

##:

#

begin

if(fen[3]&&fen[0])//#9:

##:

#

fen=fen+7;

else

fen=fen+1;

end

elsefen=fen+1;

end

elseif(Button7)//correctthemiao

begin

if(fen==8'b01011001&&miao==8'b01011001&&time_one_ten==4'b1001)//59:

59:

#

begin

fen=0;miao=0;

end

elseif(miao==8'b01011001&&time_one_ten==4'b1001)//##:

59:

#

begin

if(fen[3]&&fen[0])

fen=fen+7;

else

fen=fen+1;

miao=0;

end

end

elseif(Button6)//correctthetime_one_ten(1/10)

begin

if(fen==8'b01011001&&miao==8'b01011001&&time_one_ten==4'b1001)//59:

59:

9

begin

time_one_ten=0;fen=0;miao=0;

end

elseif(miao==8'b01011001&&time_one_ten==4'b1001)//##:

59:

9

begin

if(fen[3]&&fen[0])

fen=fen+7;

else

fen=fen+1;

miao=0;

time_one_ten=0;

end

elseif(time_one_ten==4'b1001)//##:

##:

9

begin

if(miao[3]&&miao[0])

miao=miao+7;

else

miao=miao+1;

time_one_ten=0;

end

else

time_one_ten=time_one_ten+1;

end

else

time_one_ten=time_one_ten+1;//##:

##:

#

end//theendofelse

end//theendofalways

endmodule

moduleclearjitter(clk2,reset,Button_in,Button_out);

inputclk2;//50mhzto25mhz

inputreset;

inputButton_in;

outputButton_out;

//wireButton_out;

reg[20:

0]cnt1;

reg[20:

0]cnt2;

regButton_out1_reg;

//samplingtime=50ms*25mhz

assignButton_out=Button_out1_reg;

//caiyanghighlevel

always@(posedgeclk2ornegedgereset)

begin

if(!

reset)

cnt1<=21'h000000;

else

begin

if(Button_in==1'b1)

cnt1<=cnt1+1;//countofhighlevel

else

cnt1<=21'h000000;

end

end

//caiyanglowlevel

always@(posedgeclk2ornegedgereset)

begin

if(!

reset)

cnt2<=21'h000000;

else

begin

if(Button_in==1'b0)

cnt2<=cnt2+1;//countoflowlevel