李清池版图设计.docx

《李清池版图设计.docx》由会员分享,可在线阅读,更多相关《李清池版图设计.docx(28页珍藏版)》请在冰豆网上搜索。

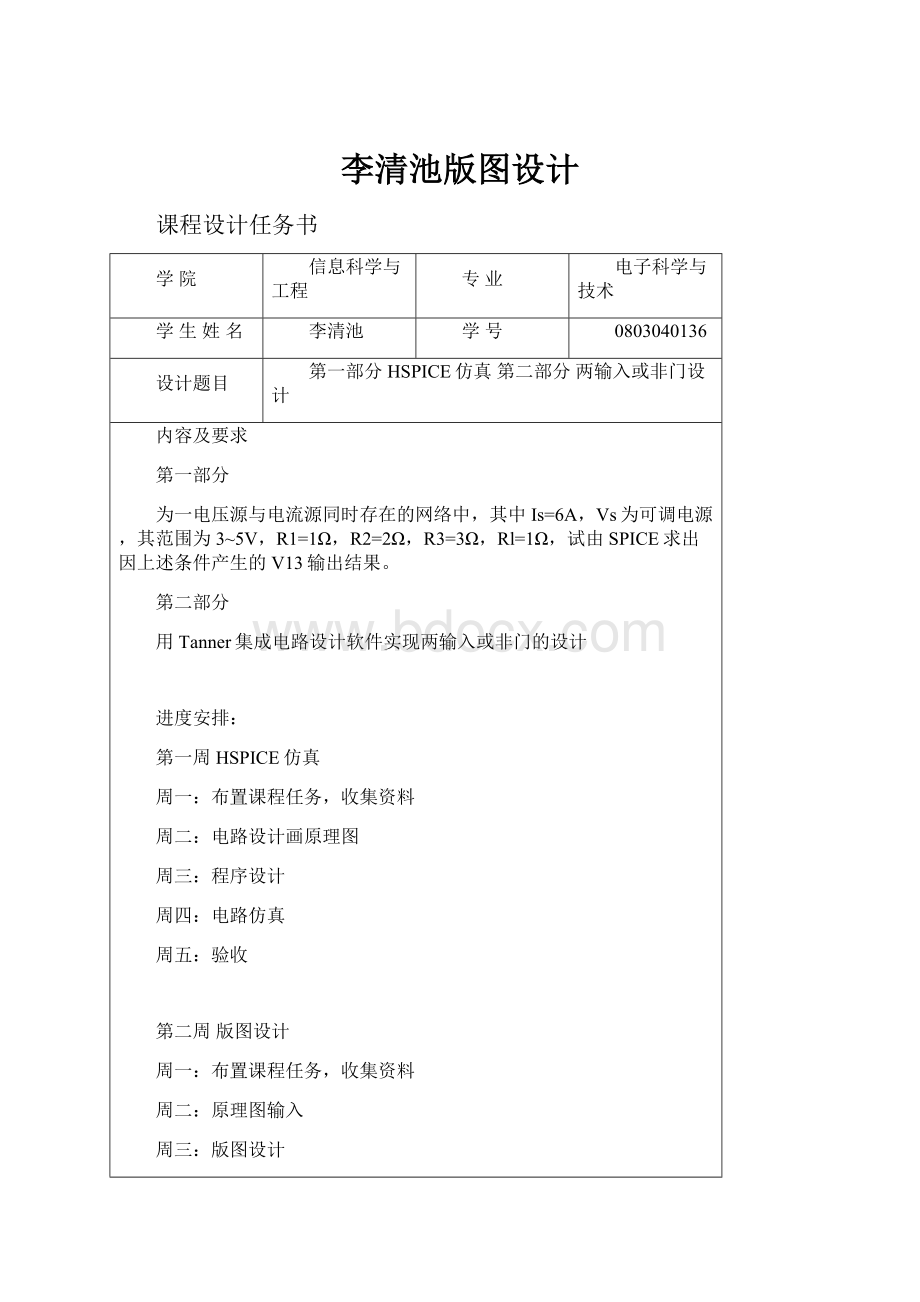

李清池版图设计

课程设计任务书

学院

信息科学与工程

专业

电子科学与技术

学生姓名

李清池

学号

0803040136

设计题目

第一部分HSPICE仿真第二部分两输入或非门设计

内容及要求

第一部分

为一电压源与电流源同时存在的网络中,其中Is=6A,Vs为可调电源,其范围为3~5V,R1=1Ω,R2=2Ω,R3=3Ω,Rl=1Ω,试由SPICE求出因上述条件产生的V13输出结果。

第二部分

用Tanner集成电路设计软件实现两输入或非门的设计

进度安排:

第一周HSPICE仿真

周一:

布置课程任务,收集资料

周二:

电路设计画原理图

周三:

程序设计

周四:

电路仿真

周五:

验收

第二周版图设计

周一:

布置课程任务,收集资料

周二:

原理图输入

周三:

版图设计

周四:

版图验证

周五:

验收,交报告书

指导教师(签字):

年月日

主管院长(签字):

年月日

摘要

随着微电子技术的迅速发展以及集成电路规模不断提高,对电路性能的设计要求越来越严格,这势必对用于大规模集成电路设计的EDA工具提出越来越高的要求。

自1972年美国加利福尼亚大学柏克莱分校电机工程和计算机科学系开发的用于集成电路性能分析的电路模拟程序SPICE(SimulationProgramwithICEmphasis)诞生以来,为适应现代微电子工业的发展,各种用于集成电路设计的电路模拟分析工具不断涌现。

HSPICE是Meta-Software公司为集成电路设计中的稳态分析,瞬态分析和频域分析等电路性能的模拟分析而开发的一个商业化通用电路模拟程序,它在柏克莱的SPICE(1972年推出),MicroSim公司的PSPICE(1984年推出)以及其它电路分析软件的基础上,又加入了一些新的功能,经过不断的改进,目前已被许多公司、大学和研究开发机构广泛应用。

关键词Hspice;EDA;大学;微电子技术

目录

摘要II

引言1

第一部分:

HSPICE仿真2

1.1设计原理2

1.2电路图2

1.3程序代码2

1.4仿真结果7

第二部分:

两输入或非门设计9

2.1原理图的设计10

2.2原理图的仿真11

2.3版图设计13

2.4设计验证17

结论22

参考文献23

引言

数字电路芯片设计按照设计流程通常分为前端设计和后端设计。

前端设计的主要任务是HDL代码的仿真以及网表的生成。

后端设计部分通常是进行自动版图生成以及验证。

本次前端设计使用的软件是Mentor公司的Modelsim以及Synopsys公司的DesignCompiler,后端设计使用的软件是SoCE和IC5141平台。

由于时间及能力限制,实习结果可能不够理想。

要实现出租车计价器的芯片级设计,首先要使用的就是计数器,进行记录输入脉冲的数量,以便实现下一步数据处理。

本次实验采用的是12位的计数器,处理模块保持和计数模块同等数量级的计数器,以方便下一步的操作。

数据处理模块分为两个,分别是金钱处理以及里程数的处理。

第一部分:

HSPICE仿真

1.1设计原理

为一电压源与电流源同时存在的网络中,其中Is=6A,Vs为可调电源,其范围为3~5V,R1=1Ω,R2=2Ω,R3=3Ω,Rl=1Ω,试由SPICE求出因上述条件产生的V13输出结果。

本题为纯电阻电路,其目的是探讨电阻元件的描述、直流操作点计算、直流电压源的扫描分析及列印的描述等应用。

此电路由于同时存在独立的电压源与电流源,因此在理论上分析部分,可利用叠加定理(superpositiontheory)对电路进行分析。

值得注意的是对于独立的电流源与电阻描述时,都以第一节点为电位的正端点。

本次实验使用的是Hspice2009软件,故在细节上和参考资料上有些不同。

1.2电路图

由于HSPICE不存在原理图编辑功能,本次实验采用的是TannerS-edit软件进行原理图的编辑,可能在外观赏上和给定的输入原理图不一样,但本质上是一样的。

图1.1电路的原理图

1.3程序代码

Hspice输入程序如下:

*2-1.spDCNodeVoltageAnalysis

Is01DC6A

Vs40DC3V

R1101

R2302

R3343

RL131

.OP

.DCVs3V5V1V

.PRINTDCV

(1)V(3)V(1,3)

.END

而Hspice的文字程序输出结果如下:

******HSPICE--C-2009.03-SP132-BIT(May252009)winnt******

Copyright(C)2009Synopsys,Inc.AllRightsReserved.

Unpublished-rightsreservedunderUScopyrightlaws.

Thisprogramisprotectedbylawandissubjecttothe

termsandconditionsofthelicenseagreementfromSynopsys.

Useofthisprogramisyouracceptancetobeboundbythe

licenseagreement.HSPICEisthetrademarkofSynopsys,Inc.

InputFile:

c:

\hspice\p2-5.sp

lic:

lic:

FLEXlm:

v8.5b

lic:

USER:

AdministratorHOSTNAME:

LBWin7

lic:

HOSTID:

"0026c7170868c80aa904ed56005056c00001005056c00008"PID:

4

1

lic:

UsingFLEXlmlicensefile:

lic:

D:

\synopsys\hspice_2009-03.lic

lic:

Checkout1hspice

lic:

License/Maintenanceforhspicewillexpireon31-dec-2020/2007.9

lic:

NODELOCKEDlicenseonhostid"0026c7170868c80aa904ed56005056c00001005

0

lic:

Init:

readinstallconfigurationfile:

C:

\synopsys\Hspice_C-2009.03-SP1\meta.cfg

Init:

hspiceinitializationfile:

C:

\synopsys\Hspice_C-2009.03-SP1\hspice.ini

*****************************************************************

******optionsummary

******

runlvl=3bypass=2

******

*2-1.spdcnodevoltageanalysis

******dctransfercurvestnom=25.000temp=25.000*****

x

voltvoltagevoltagevoltage

131

3

3.00000375.0000m750.0000m-375.0000m

4.00000500.0000m1.0000-500.0000m

5.00000625.0000m1.2500-625.0000m

y

1******HSPICE--C-2009.03-SP132-BIT(May252009)winnt******

******

*2-1.spdcnodevoltageanalysis

******operatingpointinformationtnom=25.000temp=25.000*****

*****operatingpointstatusisallsimulationtimeis0.

node=voltagenode=voltagenode=voltage

+0:

1=375.0000m0:

3=750.0000m0:

4=3.0000

****voltagesources

subckt

element0:

vs

volts3.0000

current-750.0000m

power2.2500

totalvoltagesourcepowerdissipation=2.2500watts

*****currentsources

subckt

element0:

is

volts-375.0000m

current6.0000a

power2.2500a

totalcurrentsourcepowerdissipation=2.2500awatts

****resistors

subckt

element0:

r10:

r20:

r30:

rl

rvalue1.00002.00003.00001.0000

vdrop375.0000m750.0000m-2.2500-375.0000m

current375.0000m375.0000m-750.0000m-375.0000m

power140.6250m281.2500m1.6875140.6250m

*****jobconcluded

1******HSPICE--C-2009.03-SP132-BIT(May252009)winnt******

******

*2-1.spdcnodevoltageanalysis

******jobstatisticssummarytnom=25.000temp=25.000*****

******HSPICEThreadsInformation******

CommandLineThreadsCount:

1

AvailableCPUCount:

2

ActualModelEvaluation(Load)ThreadsCount:

1

ActualSolverThreadsCount:

1

******CircuitStatistics******

#nodes=4#elements=6

#resistors=4#capacitors=0#inductors=0

#mutual_inds=0#vccs=0#vcvs=0

#cccs=0#ccvs=0#volt_srcs=1

#curr_srcs=1#diodes=0#bjts=0

#jfets=0#mosfets=0#Uelements=0

#Telements=0#Welements=0#Belements=0

#Selements=0#Pelements=0#vadevice=0

******RuntimeStatistics(seconds)******

analysistime#pointstot.iterconv.iter

oppoint0.0214

dcsweep0.0238

readin0.09

errchk0.00

setup0.03

output0.00

totalmemoryused28kbytes

totalcputime0.16seconds

totalelapsedtime0.22seconds

jobstartedat17:

47:

3301/09/2012

jobendedat17:

47:

3301/09/2012

Init:

hspiceinitializationfile:

C:

\synopsys\Hspice_C-2009.03-SP1\hspice.ini

lic:

Releasehspicetoken(s)

图1.2网表生成文件

图1.3网表生成文件电压增益

上述输出程序资料,第一栏为扫描的电压增益,第二及第三栏位V

(1)、V(3)的输出电压,而第四栏为节点1及节点3的电压差。

1.4仿真结果

验证:

就是通过仿真、时序分析、以及网表生成等手段检验设计正确性。

在芯片设计开发流程中,验证主要包括功能验证和时序验证两个部分。

本次实验用到部分Tanner软件,故先把Tanner软件中的T-spice仿真结果给出:

图1.4Tanner下的分离仿真波形

图1.5Tanner下的混合仿真波形

下面给出Hspice软件中的仿真波形:

图1.6Hspice下的混合仿真波形

图1.7Tanner下的分离仿真波形

第二部分:

两输入或非门设计

本次课程设计使用的是Tanner软件,其中包括根据原理图绘制出或非门版图,并进行DRC检测、T-spice仿真和LVS版图验证。

2.1原理图的设计

或非门是由两个PMOS串联和两个并联的NMOS相连构成了二输入或非门。

在Tanner中进行原理图设计输入的软件是S-edit软件。

多输入的电路图的设计与基本的互补CMOS工艺类似,PMOS提供上拉电压,PMOS提供下拉电压。

下面给出两输入或非门的原理图:

图2.1S-edit或非门原理图

2.2原理图的仿真

在进行完原理图的设计与输入后,要进行的就是原理图的仿真验证。

验证工具tanner下自带的是T-spice。

在进行仿真之前,要对原理图添加激励信号。

添加完成激励后的原理图如下图:

图2.2S-edit仿真或非门原理图

点击T-spice按键,出现如下代码:

*SPICEnetlistwrittenbyS-EditWin327.03

*WrittenonJan10,2012at21:

37:

43

*Waveformprobingcommands

.probe

.optionsprobefilename="D:

\tanner\S-Edit\ornot.dat"

+probesdbfile="D:

\tanner\S-Edit\ornot.sdb"

+probetopmodule="Module0"

*Maincircuit:

Module0

M1outaGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M2outbGndGndNMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M3outbN2VddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

M4N2aVddVddPMOSL=2uW=22uAD=66pPD=24uAS=66pPS=24u

v5VddGnd5.0

v6bGndpulse(0.05.0010n10n100n200n)

v7aGndpulse(0.05.0010n10n100n200n)

*Endofmaincircuit:

Module0

代码中由于缺少部分文件,所以波形不能出来,故对T-spice文件进行修改。

1.添加库文件:

.include"D:

\tanner\TSpice70\models\ml2_125.md"

2.加入输出延时.tran2n600n

3.添加输出信号.printtranaout

.printtranbout

4.修改v6bGndpulse(0.05.0010n10n50n100n)

完成设置后,点击运行,出现如下结果:

图2.3原理图仿真结果

这时的波形比较乱,点击ExpendChart出现如下图形,方便分析:

图2.4分离的原理图仿真结果

经过分析,原理图是正确的,所以进行下一步的操作。

2.3版图设计

本次实验先进行的是PMOS的设计,其设计参数如下表:

名称

宽度x

长度y

N-well

24

15

Active

14

5

Selet

18

9

Poly

2

7

ActiveContact

2

2

Metal1

4

4

表2.1PMOS的版图设计参数

其生成的PMOS版图如下:

图2.5PMOS的版图

第二步做的是NMOS的设计程,NMOS参数与PMOS基本上一致,但是NMOS没有N-well,故其参数如下表:

名称

宽度x

长度y

Active

14

5

Selet

18

9

Poly

2

7

ActiveContact

2

2

Metal1

4

4

表2.2NMOS的版图设计参数

由于缺少N-well,所以NMOS出面积上看比PMOS要小,下面给出NMOS的版图:

图2.6NMOS的版图

设计中,P型衬底的参数如下:

名称

宽度x

长度y

N-well

15

15

Active

5

5

N-select

9

9

ActiveContact

2

2

Metal1

4

4

表2.3PMOS的衬底版图设计参数

PMOS的衬底版图如下所示:

图2.7PMOS的衬底版图

设计中,N型衬底的参数如下:

名称

宽度x

长度y

Active

5

5

P-select

9

9

ActiveContact

2

2

Metal1

4

4

表2.4NMOS的衬底版图设计参数

NMOS的衬底版图如下所示:

图2.8NMOS的衬底版图

版图中,输入端口的参数值为:

名称

宽度x

长度y

Poly

5

5

via

2

2

ActiveContact

2

2

Metal1

10

4

metal2

4

4

port

4

4

表2.5输入接触孔参数

输入端口的版图为:

图2.9输入接触孔版图

输出接触孔的参数为:

名称

宽度x

长度y

via

2

2

metal2

4

4

port

4

4

表2.6输出接触孔参数

输出接触孔的版图为:

图2.10输出接触孔版图

做完这些预备的工作,就可以看到版图了,下面给出两输入或非门的Tanner版图:

图2.11两输入或非门版图

2.4设计验证

首先是DRC检测,DRC检测的结果如下:

图2.12DRC检测结果

完成DRC检测后要做的是LVS验证,先利用版图生成验证文件,内容如下:

*CircuitExtractedbyTannerResearch'sL-EditVersion9.00/ExtractVersion9.00;

*TDBFile:

D:

\tanner\LEdit90\ornot2.tdb

*Cell:

Cell0Version1.06

*ExtractDefinitionFile:

Samples\SPR\example1\lights.ext

*ExtractDateandTime:

01/10/2012-19:

57

*Warning:

LayerswithUnassignedAREACapacitance.

*

*

*

*

*

*

*Warning:

LayerswithUnassignedFRINGECapacitance.

*

*

*

*

*

*

*

*

*Warning:

LayerswithZeroResistance.

*

*

*

*

*NODENAMEALIASES

*1=b(-99,51)

*2=a(-141.5,51.5)

*3=out(-79.5,57)

*3=out/OUT(-79.5,57)

M1outb64PMOSL=2uW=5u

*M1DRAINGATESOURCEBULK(-82.570.5-80.575.5)

M26a44PMOSL=2uW=5u

*M2DRAINGATESOURCEBULK(-134.570.5-132.575.5)

M3outb55NMOSL=2uW=5u

*M3DRAINGATESOURCEBULK(-82.531.5-80.536.5)

M4outa55NMOSL=2uW=5u

*M4DRAINGATESOURCEBULK(-134.531.5-132.536.5)

*TotalNodes:

6

*TotalElements:

4

*TotalNumberofShortedElementsnotwrittentotheSPICEfile:

0

*ExtractElapsedTime:

0seconds

.END

对比上面原理图中的文件,发现MOS管宽长比不一样,所以决定修改原理图,将原理图中的宽长比改为版图中的对应2:

5,进行LVS检测,得到如下结果:

Filew