JK触发器的设计.docx

《JK触发器的设计.docx》由会员分享,可在线阅读,更多相关《JK触发器的设计.docx(14页珍藏版)》请在冰豆网上搜索。

JK触发器的设计

JK触发器的设计

JK触发器的设计

一、JK触发器的组成

在实际的数字系统中往往包含大量的存储单元,而且经常要求他们在同一时刻同步动作,为达到这个目的,在每个存储单元电路上引入一个时钟脉冲(CLK)作为控制信号,只有当CLK到来时电路才被“触发”而动作,并根据输入信号改变输出状态,把这种在时钟信号触发时才能动作的存储单元电路称为触发器。

触发器是边沿触发工作,即只有在上升沿或者是下降沿到来时才会改变内部与输出的电平。

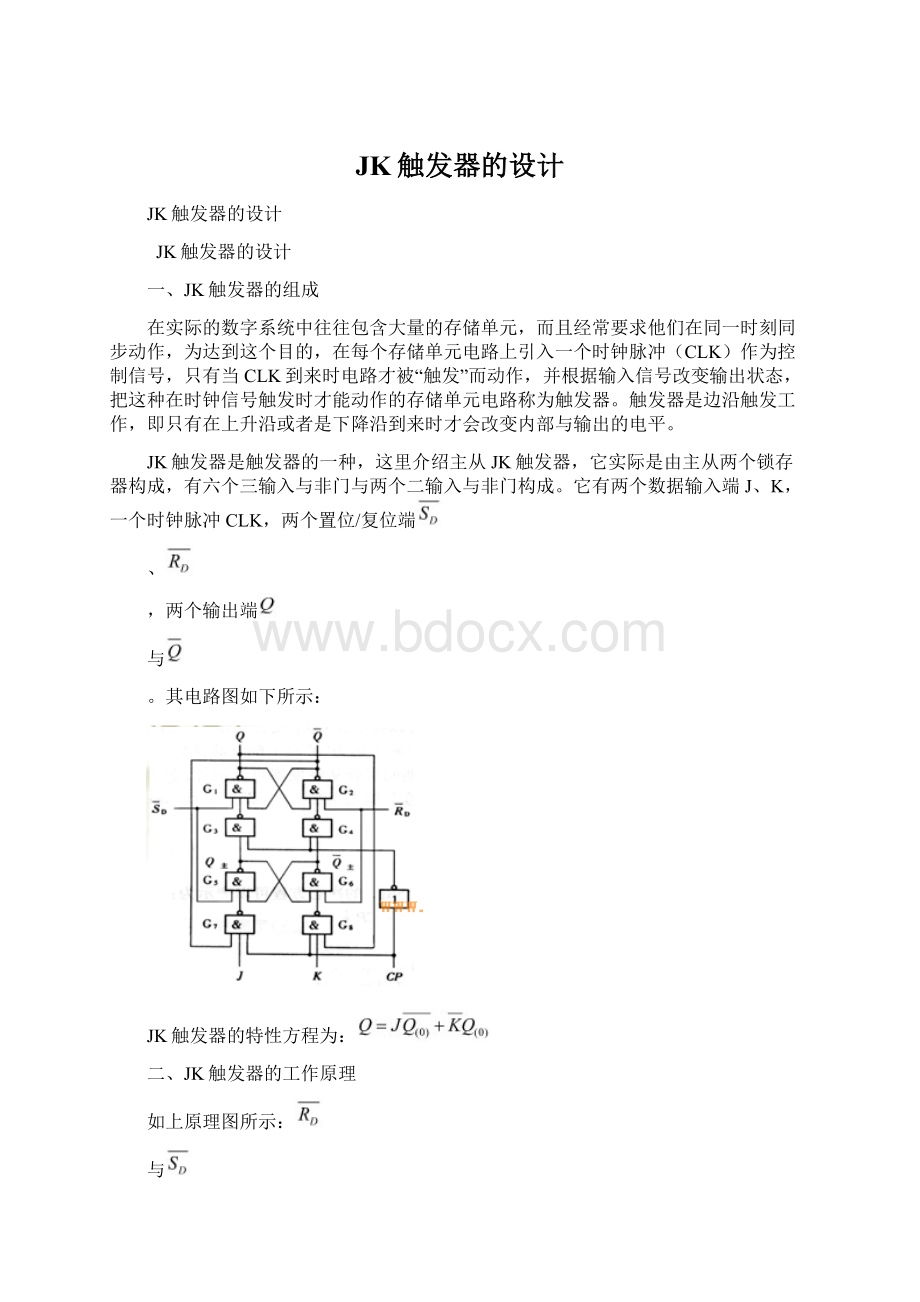

JK触发器是触发器的一种,这里介绍主从JK触发器,它实际是由主从两个锁存器构成,有六个三输入与非门与两个二输入与非门构成。

它有两个数据输入端J、K,一个时钟脉冲CLK,两个置位/复位端

、

,两个输出端

与

。

其电路图如下所示:

JK触发器的特性方程为:

二、JK触发器的工作原理

如上原理图所示:

与

为置位/复位控制端,由于用的是与非门,置位与复位控制端为低电平有效。

当

=0,

=1时,置位端有效,

,

,输出置1;当

=1,

=0时,复位端有效,

,

,输出端置1;当

=1,

=1时,置位与复位端都不起作用,触发器正常工作。

CLK为时钟脉冲,主锁存器是高电平跳变,当CLK=1时,

随着输入信号JK的变化而变化,而当CLK=0时,主锁存器被锁定,

的值不发生变化;从锁存器是低电平跳变,

接着创建二输入与非门的原理图与symbol:

创建反相器的原理图与symbol:

然后通过调用反相器、二输入与非门和三输入与非门的symbol来创建JK触发器的原理图。

红色方框中为主锁存器,在CLK为高电平时跳变;蓝色方框中为从锁存器,由于其时钟脉冲前加了一个反相器,它是在CLK为低电平时跳变。

创建JK触发器的symbol,以便搭建仿真测试电路:

1)JK触发器版图的创建

JK触发器版图的创建与原理图创建一样,也采取模块化设计原则。

先创建三输入与非门的版图,如下左图所示:

接着创建二输入与非门的版图,如上右图所示:

创建反相器的版图,如下所示:

最后通过调用三输入与非门、二输入与非门和反相器的版图来生成JK触发器的版图,如下所示:

对JK触发器的版图进行DRC验证,结果如下:

对JK触发器的版图进行LVS验证,结果如下:

对JK触发器的版图进行PEX验证,结果如下:

2)JK触发器的仿真验证

对JK触发器的功能进行仿真验证。

首先创建一个仿真电路图,如下图所示。

SOUCRE所接电源为5V直流信号,S_,D_,J,K,CLK所接电源分别为周期为30us、40us、1us、7us、8us的0~5V的方波信号,设置好仿真环境,对输入端S_、D_、J、K、CLK和输出端Q、Q_进行瞬态仿真。

仿真波形如下所示:

图中由上到下七个波形分别为S_、R_、CLK、J、K、Q、Q_,对图中波形进行分析。

对于S_与D_,S_=1,D_=1时,输出Q与Q_随J、K信号的变化而变化;当S_=0,D_=1时,Q=1,Q_=0,直接置1,J、K信号无效;当S_=1,D_=0时,Q=0,Q_=1,直接置0,J、K信号无效;当S_=0,D_=0时,Q=1,Q_=1。

J、K无效,此时Q与Q_电位并不是相反。

除了S_、R_均为0的情况外,S_、R_端的功能与真值表中的描述完全一致,而由JK触发器的电路图可以退出S_、R_均为0时,Q与Q_的输出都为1。

将上图中中S_、R_均为1时,CLK、J、K、Q、Q_的图形进行放大可以得到下图。

由上图可以分析触发器中输入端J、K的作用,显然由上图分析可得,J=1,K=1时,实现翻转功能;J=1,K=0时,实现置位(置1)的功能;J=0,K=1时,实现复位(置0)的功能;J=0看,K=0时,则输出情况保持不变。

显然波形图与真值表中J、K的功能一致。

引入寄生参数,对JK触发器进行后仿真,结果如下。

左侧为前仿真波形,右侧为后仿真波形,前后波形一致。

将波形放大来观察前仿真与后仿真延迟时间的差别。

观察放大后的前后仿真波形图进行对比,前后仿真的延迟时间基本一致。