微波炉控制器的设计与分析.docx

《微波炉控制器的设计与分析.docx》由会员分享,可在线阅读,更多相关《微波炉控制器的设计与分析.docx(18页珍藏版)》请在冰豆网上搜索。

微波炉控制器的设计与分析

FPGA系统设计

组成员及负责模块:

冀鹏超状态控制器KZQ设计

陆威数据装载器ZZQ设计

韩华凯烹饪计时器JSQ设计

凌智烹饪计时器JSQ设计

白浚材显示译码器YMQ47设计

孙兵剑微波炉控制器WBLKZQ设计

微波炉控制器的设计与分析

一.系统设计要求

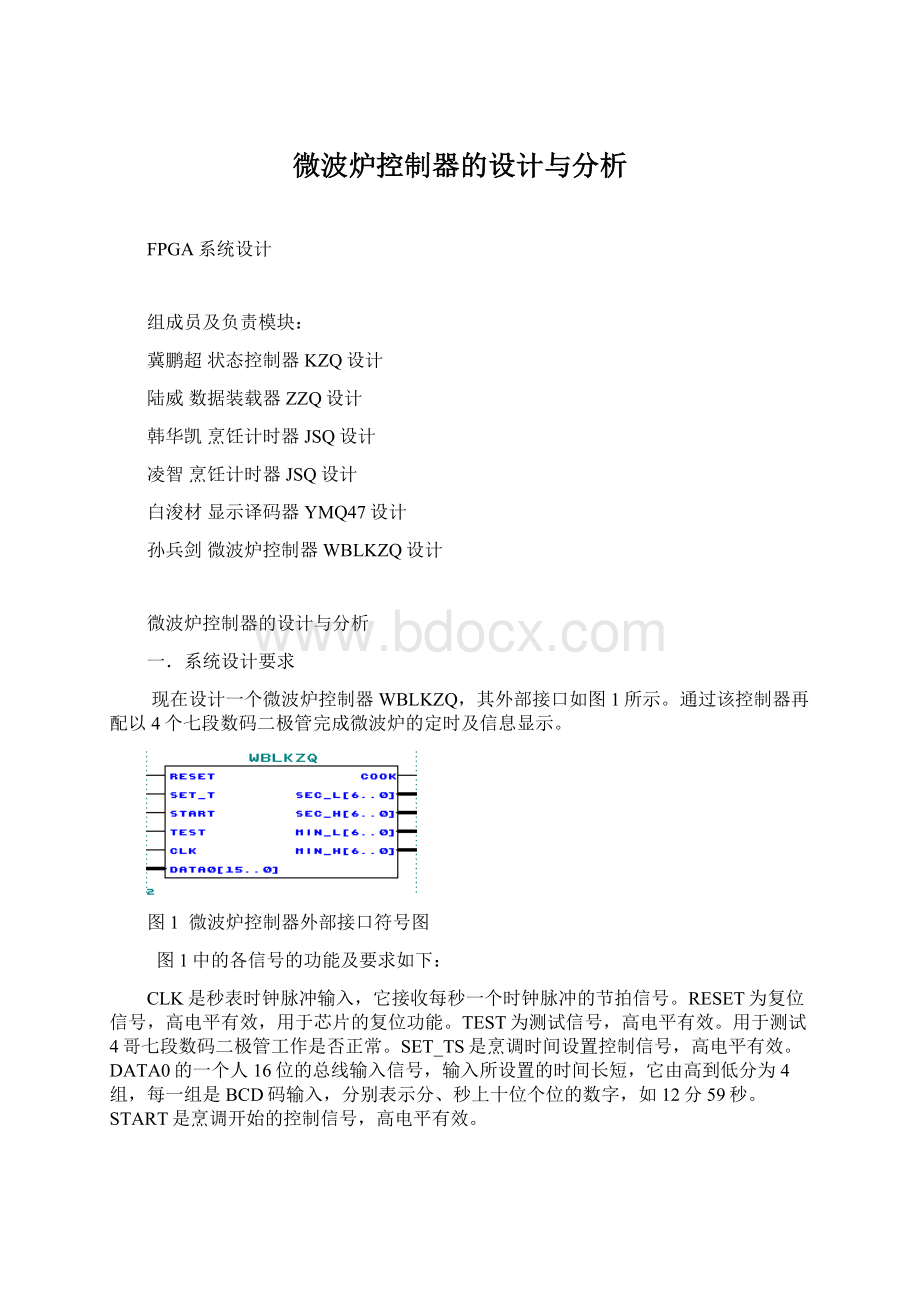

现在设计一个微波炉控制器WBLKZQ,其外部接口如图1所示。

通过该控制器再配以4个七段数码二极管完成微波炉的定时及信息显示。

图1微波炉控制器外部接口符号图

图1中的各信号的功能及要求如下:

CLK是秒表时钟脉冲输入,它接收每秒一个时钟脉冲的节拍信号。

RESET为复位信号,高电平有效,用于芯片的复位功能。

TEST为测试信号,高电平有效。

用于测试4哥七段数码二极管工作是否正常。

SET_TS是烹调时间设置控制信号,高电平有效。

DATA0的一个人16位的总线输入信号,输入所设置的时间长短,它由高到低分为4组,每一组是BCD码输入,分别表示分、秒上十位个位的数字,如12分59秒。

START是烹调开始的控制信号,高电平有效。

COOK是烹调进行信号,它外接用于控制烹调的继电器开关,高电平时表明烹调已经开始或正在进行,低电平表示烹调结束或没有进行。

MIN_H(十分位)、MIN_L(分位)、SEC_H(十秒位)和SEC_L(秒位)是4组七位总线信号,它们分别接4个七段数码管,动态地显示完成烹调所剩的时间以及测试状态信息“8888”、烹调完毕的状态信息“donE”。

该微波炉控制器WBLKZQ的具体功能要求如下:

上电后系统首先处于一种复位状态。

在工作时首先按SEC_L键设置烹调时间,此时系统读入DATA0的数据作为烹调所需时间,然后系统自动回到复位状态,同时4个七段数码管显示时间信息(假设系统最长的烹调时间为59分59秒)。

再按START键后系统进入烹调状态,COOK信号开始为高电平,此时4个七段数码管每隔一秒钟变化一次,用以刷新还剩多少时间结束烹调。

烹调结束后,COOK信号变为低电平,同时4个七段数码管组合在一起显示“donE”的信息,然后系统回到复位状态。

系统可以通过按RESET键随时回到复位状态。

在复位状态下,按TEST键在4个数码管上会显示“8888”的信息,它可以测试4个七段数码管工作是否正常。

二.系统设计要

1.微波炉控制器的总体设计方案

根据该微波炉控制器的功能设计要求,本系统可由以下4个模块组成:

①状态控制器KZQ;②数据装载器ZZQ;③烹调计时器JSQ;④显示译码器YMQ47。

其内部组成原理如图2所示。

图2微波炉控制器WBLKZQ的内部组成原理图

(1)状态控制器KZQ的功能是控制微波炉工作过程中的状态转换,并发出有关控制信息:

输入信号为CLK、TEST、START、SET_T、RESET和DONE,输出信号为LD_DONE、LD_CLK、LD_8888和COOK信号。

KZQ根据输入信号和自身当时所处的状态完成状态的转换和输出相应的控制信号:

LD_DONE指示ZZQ装入烹调完毕的状态信息“donE”的显示驱动信息数据;LD_CLK指示ZZQ装入设置的烹饪时间数据;LD_8888指示ZZQ装入用于测试的数据“8888”以显示驱动信息数据;COOK指示烹饪正在进行之中,并提示计时器进行减计数。

(2)数据装载器ZZQ的功能是根据KZQ发出的控制信号选择定时时间、测试数据或烹调完成信息的装入。

当LD_DONE为高电平时,输出烹调完毕的状态信息数据;LD_CLK为高电平时,输出设置的烹饪时间数据;LD_8888为高电平时,输出测试数据。

输出信号LOAD用于提示JSQ将处于数据装入状态。

(3)计时器JSQ的功能是负责烹调过程中的时间递减计数,并提供烹调完成时的状态信号提供KZQ产生烹调完成信号。

LOAD为高电平时完成装入功能,COOK为高电平时执行逆计数功能。

输入DONE指示烹调完成。

MIN_H、MIN_L、SEC_H、和SEC_L为完成烹调所剩的时间以及测试状态信息“8888”、烹调完毕的状态信息“donE”的BCD码信息。

(4)显示译码器YMQ47的功能就是负责将各种显示信息的BCD转换成七段数码管显示的驱动信息编码。

需要译码的信息有:

数字0~9,字母d、o、n、E。

2.状态控制器KZQ的设计

状态控制器KZQ的功能是控制微波炉工作过程中的状态转换,并发出有关控制信息,因此我们可用一个状态机来实现它。

经过对微波炉工作过程中的状态转换条件及输出信号进行分析,我们可得到其状态转换图如图3所示,其输入、输出端口如图4所示。

图3KZQ的输入输出端口图

图4KZQ的输入输出端口图

3.数据装载器ZZQ的设计

ZZQ的输入、输出端口如5所示,根据其应完成的逻辑功能,它本质上就是一个三选一数据选择器。

本设计采用一个进程来完成,但由于三个被选择的数据只有一个来自输入端口,因此另两个被选择的数据则通过在进程的说明部分定义两个常数来产生。

由于用于显示“8888”的常数ALL-8需分解成4个8,分别经过四个4—7译码器译码后才是真正的显示驱动信息编码,因此该常数应是4个分段的是4位BCD码,故应设为“1000100010001000”。

同理,显示“donE”的常数DONE可设为“1010101111001101”,其中d、o、n、E的BCD码分别为:

“1010”、“1011”、“1100”、“1101”。

该模块的主要程序如下:

图5ZZQ的输入输出端口

PROCESS(DATA1,LD_8888.LD_CLK.LD_DONE)IS

CONSTANTALL_8:

STD_LOGIC_VECTOR(15DOWNTO0):

="1000100010001000";

CONSTANTDONE:

STD_LOGIC_VECTOR(15DOWNTO0):

="1010101111001101";

VARIABLETEMP:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

LOAD<=LD_8888ORLD_DONEORLD_CLK;

TEMP:

=LD_8888&LD_DONE&LD_CLK;

CASETEMPIS

WHEN"100"=>DATA2<=ALL_8;--LOAD_8888=1

WHEN"010"=>DATA2<=DONE;--LOAD_DONE=1

WHEN"001"=>DATA2<=DATA1;--LOAD_CLK=1

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

4.烹调计时器JSQ的设计

烹调计时器JSQ为减数计时器,其最大计时时间为59:

59。

因此我们可用两个减计数十进制计数器DCNT10和两个减计数六进制计数器DCNT6级联构成。

JSQ的内部组成原理如图6所示。

图6JSQ的内部组成原理图

5.显示译码器YMQ47的设计

本显示译码器YMQ47不但要对数字0~9进行显示译码,还要对字母d、o、n、E进行显示译码,其译码对照表如表1所示。

表1YMQ47的译码对照表

显示的数字或字母

BCD编码

七段显示驱动编码(g~a)

0

0000

0111111

1

0001

0000110

2

0010

1011011

3

0011

1001111

4

0100

1100110

5

0101

1101101

6

0110

1111101

7

0111

0000111

8

1000

1111111

9

1001

1101111

d

1010

1011110

o

1011

1011100

n

1100

1010100

E

1101

1111001

三.主要VHDL源程序

1.状态控制器KZQ的VHDL源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYKZQIS

PORT(RESET,SET_T,START,TEST,CLK,DONE:

INSTD_LOGIC;

COOK,LD_8888,LD_CLK,LD_DONE:

OUTSTD_LOGIC);

ENDENTITYKZQ;

ARCHITECTUREARTOFKZQIS

TYPESTATE_TYPEIS(IDLE,LAMP_TEST,SET_CLOCK,TIMER,DONE_MSG);

SIGNALNXT_STATE,CURR_STATE:

STATE_TYPE;

BEGIN

PROCESS(CLK,RESET)IS

BEGIN

IFRESET='1'THEN

CURR_STATE<=IDLE;

ELSIFCLK'EVENTANDCLK='1'THEN

CURR_STATE<=NXT_STATE;

ENDIF;

ENDPROCESS;

PROCESS(CLK,CURR_STATE,SET_T,START,TEST,DONE)IS

BEGIN

NXT_STATE<=IDLE;--DEFAULTNEXSTATEISIDLE

LD_8888<='0';

LD_DONE<='0';

LD_CLK<='0';

COOK<='0';

CASECURR_STATEIS

WHENLAMP_TEST=>LD_8888<='1';COOK<='0';

WHENSET_CLOCK=>LD_CLK<='1';COOK<='0';

WHENDONE_MSG=>LD_DONE<='0';COOK<='0';

WHENIDLE=>

IF(TEST='1')THEN

NXT_STATE<=LAMP_TEST;

LD_8888<='1';

ELSIFSET_T='1'THEN

NXT_STATE<=SET_CLOCK;

LD_CLK<='1';

ELSIF((START='1')AND(DONE='0'))THEN

NXT_STATE<=TIMER;

COOK<='1';

ENDIF;

WHENTIMER=>

IFDONE='1'THEN

NXT_STATE<=DONE_MSG;

LD_DONE<='1';

ELSE

NXT_STATE<=TIMER;

COOK<='1';

ENDIF;

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREART;

2.数据装载器ZZQ的VHDL源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYZZQIS

PORT(DATA1:

INSTD_LOGIC_VECTOR(15DOWNTO0);

LD_8888:

INSTD_LOGIC;

LD_CLK:

INSTD_LOGIC;

LD_DONE:

INSTD_LOGIC;

DATA2:

OUTSTD_LOGIC_VECTOR(15DOWNTO0);

LOAD:

OUTSTD_LOGIC);

ENDENTITYZZQ;

ARCHITECTUREARTOFZZQIS

BEGIN

PROCESS(DATA1,LD_8888,LD_CLK,LD_DONE)IS

CONSTANTALL_8:

STD_LOGIC_VECTOR(15DOWNTO0):

="1000100010001000";

CONSTANTDONE:

STD_LOGIC_VECTOR(15DOWNTO0):

="1010101111001101";

VARIABLETEMP:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

LOAD<=LD_8888ORLD_DONEORLD_CLK;

TEMP:

=LD_8888&LD_DONE&LD_CLK;

CASETEMPIS

WHEN"100"=>DATA2<=ALL_8;

WHEN"010"=>DATA2<=DONE;

WHEN"001"=>DATA2<=DATA1;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

3.烹调计时器JSQ的VHDL源程序

--DCNT10.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDCNT10IS

PORT(CLK:

INSTD_LOGIC;

LOAD:

INSTD_LOGIC;

ENA:

INSTD_LOGIC;

DATAIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

CARRY_OUT:

OUTSTD_LOGIC);

ENDENTITYDCNT10

ARCHITECTUREARTOFDCNT10IS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK,LOAD,ENA)IS

BEGIN

IFLOAD='1'THEN

CQI<=DATAIN;

ELSIFCLK'EVENTANDCLK='1'THEN

IFENA='1'THEN

IFCQI="000"THENCQI<="1001";

ELSECQI<=CQI-'1';ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(CLK,CQI)IS

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCQI="0000"THENCARRY_OUT<='1';

ELSECARRY_OUT<='0';ENDIF;

ENDIF;

ENDPROCESS;

CQ<=CQI;

ENDARCHITECTUREART;

--DCNT6.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDCNT6IS

PORT(CLK:

INSTD_LOGIC;

LOAD:

INSTD_LOGIC;

ENA:

INSTD_LOGIC;

DATAIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

CARRY_OUT:

OUTSTD_LOGIC);

ENDENTITYDCNT6;

ARCHITECTUREARTOFDCNT6IS

SIGNALCQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

PROCESS(CLK,LOAD,ENA)IS

BEGIN

IFLOAD='1'THEN

CQI<=DATAIN;

ELSIFCLK'EVENTANDCLK='1'THEN

IFENA='1'THEN

IFCQI="0000"THENCQI<="0101";

ELSECQI<=CQI-'1';ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

PROCESS(CLK,CQI)IS

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCQI="0000"THENCARRY_OUT<='1';

ELSECARRY_OUT<='0';ENDIF;

ENDIF;

ENDPROCESS;

CQ<=CQI;

ENDARCHITECTUREART;

--JSQ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYJSQIS

PORT(COOK:

INSTD_LOGIC;

DATA3:

INSTD_LOGIC_VECTOR(15DOWNTO0);

LOAD:

INSTD_LOGIC;

CLK:

INSTD_LOGIC;

SEC_L:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

SEC_H:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

MIN_L:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

MIN_H:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

DONE:

OUTSTD_LOGIC);

ENDENTITYJSQ;

ARCHITECTUREARTOFJSQIS

COMPONENTDCNT10IS

PORT(CLK,LOAD,ENA:

INSTD_LOGIC;

DATAIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

CARRY_OUT:

OUTSTD_LOGIC);

ENDCOMPONENTDCNT10;

COMPONENTDCNT6IS

PORT(CLK,LOAD,ENA:

INSTD_LOGIC;

DATAIN:

INSTD_LOGIC_VECTOR(3DOWNTO0);

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

CARRY_OUT:

OUTSTD_LOGIC);

ENDCOMPONENTDCNT6;

SIGNALNEWCLK:

STD_LOGIC;

SIGNALS1:

STD_LOGIC;

SIGNALS2:

STD_LOGIC;

SIGNALS3:

STD_LOGIC;

SIGNALS4:

STD_LOGIC;

BEGIN

U1:

DCNT10PORTMAP(CLK,LOAD,COOK,DATA3(3DOWNTO0),SEC_L,S1);

U2:

DCNT6PORTMAP(S1,LOAD,COOK,DATA3(7DOWNTO4),SEC_H,S2);

U3:

DCNT10PORTMAP(S2,LOAD,COOK,DATA3(11DOWNTO8),MIN_L,S3);

U4:

DCNT6PORTMAP(S3,LOAD,COOK,DATA3(15DOWNTO12),MIN_H,S4);

DONE<=S1ANDS2ANDS3ANDS4;

ENDARCHITECTUREART;

4.显示译码器YMQ47的源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYYMQ47IS

PORT(AIN4:

INSTD_LOGIC_VECTOR(3DOWNTO0);

DOUT7:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDENTITYYMQ47;

ARCHITECTUREARTOFYMQ47IS

BEGIN

PROCESS(AIN4)

BEGIN

CASEAIN4IS

WHEN"0000"=>DOUT7<="0111111";

WHEN"0001"=>DOUT7<="0000100";

WHEN"0010"=>DOUT7<="1011011";

WHEN"0011"=>DOUT7<="1001111";

WHEN"0100"=>DOUT7<="1100110";

WHEN"0101"=>DOUT7<="1101101";

WHEN"0110"=>DOUT7<="1111101";

WHEN"0111"=>DOUT7<="0000111";

WHEN"1000"=>DOUT7<="1111111";

WHEN"1001"=>DOUT7<="1101111";

WHEN"1010"=>DOUT7<="1011110";

WHEN"1011"=>DOUT7<="1011100";

WHEN"1100"=>DOUT7<="1010100";

WHEN"1101"=>DOUT7<="1111001";

WHENOTHERS=>DOUT7<="0000000";

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREART;

5.微波炉控制器WBLKZQ的VHDL源程序

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

USEIEEE.STD_LOGIC_ARITH.ALL;

ENTITYWBLKZQIS

PORT(RESET,SET_T,START,TEST,CLK:

INSTD_LOGIC;

DATA0:

INSTD_LOGIC_VECTOR(15DOWNTO0);

COOK:

OUTSTD_LOGIC;

SEC_L,SEC_H,MIN_L,MIN_H:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

ENDENTITYWBLKZQ;

ARCHITECTUREARTOFWBLKZQIS

COMPONENTKZQIS

PORT(RESET,SET_T,START,TEST,CLK,DONE:

INSTD_LOGIC;

COOK,LD_8888,LD_CLK,LD_DONE:

OUTSTD_LOGIC);

ENDCOMPONENTKZQ;

COMPONENTZZQIS

PORT(DATA1:

INSTD_LOGIC_VECTOR(15DOWNTO0);

LD_8888:

INSTD_LOGIC;

LD_CLK:

INSTD_LOGIC;

LD_DONE:

INSTD_LOGIC;

DATA2:

OUTSTD_LOGIC_VECTOR(15DOWNTO0);

LOAD:

OUTSTD_LOGIC);

ENDCOMPONENTZZQ;

COMPONENTJSQIS

PORT(COOK:

INSTD_LOGIC;

DATA3:

INSTD_LOGIC_VECTOR(15DOWNTO0);

LOAD:

INSTD_LOGIC;

CLK:

INSTD_LOGIC;

SEC_L:

OUTSTD_LOGIC_V