Xinlinx原语的用法.docx

《Xinlinx原语的用法.docx》由会员分享,可在线阅读,更多相关《Xinlinx原语的用法.docx(22页珍藏版)》请在冰豆网上搜索。

Xinlinx原语的用法

Xilinx公司原语的使用方法

原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。

原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。

在Verilog中使用原语非常简单,将其作为模块名直接例化即可。

本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。

其它系列芯片原语的使用方法是类似的。

Xilinx公司的原语按照功能分为10类,包括:

计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。

下面分别对其进行详细介绍。

3.4.1计算组件

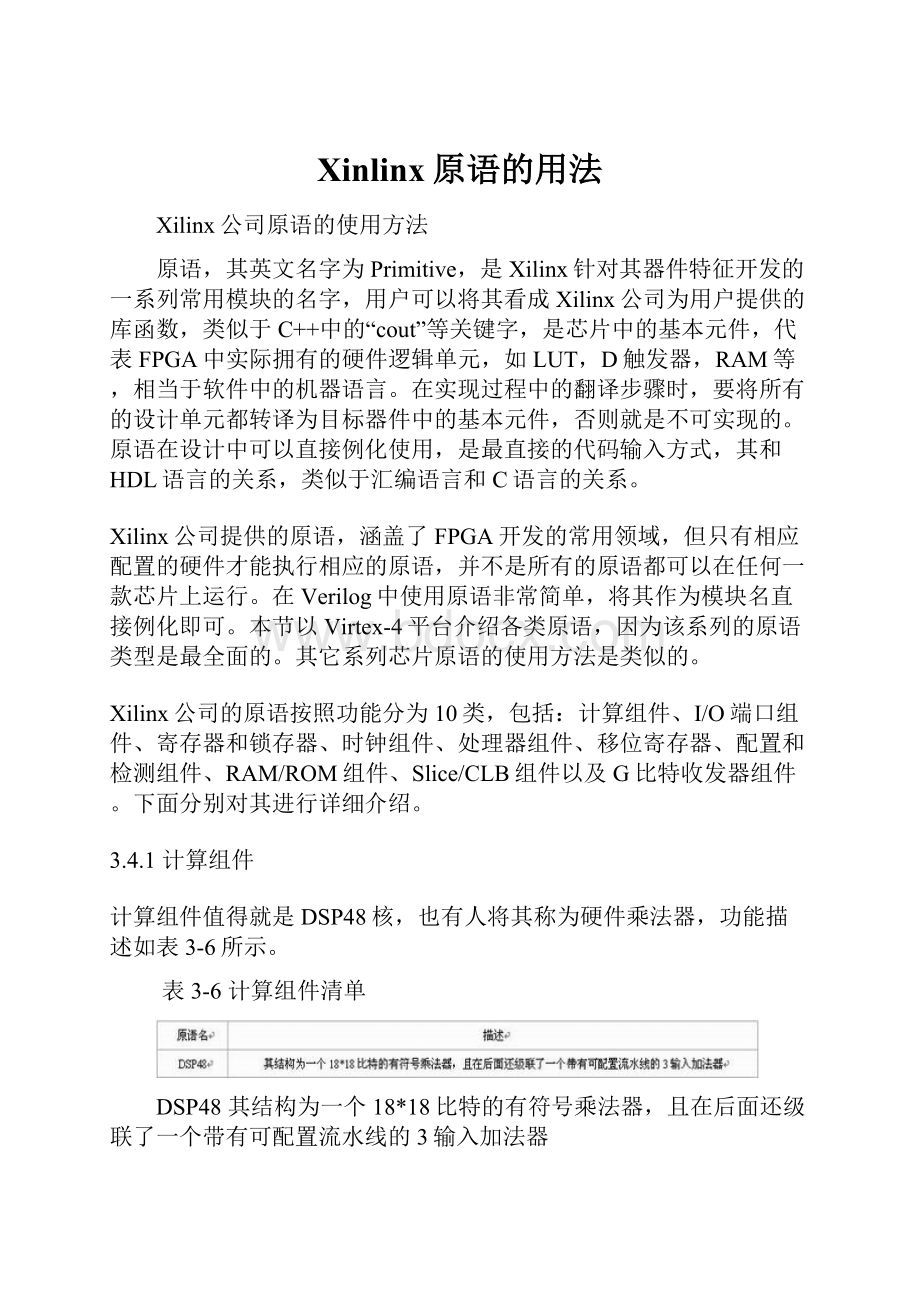

计算组件值得就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。

表3-6计算组件清单

DSP48其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器

DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。

其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。

其在Verilog中的例化模版为:

modulefpga_v4_dsp48(

BCOUT,P,PCOUT,A,B,BCIN,C,CARRYIN,CARRYINSEL,CEA,CEB,

CEC,CECARRYIN,CECINSUB,CECTRL,CEM,CEP,CLK,OPMODE,

PCIN,RSTA,RSTB,RSTC,RSTCARRYIN,RSTM,RSTP,SUBTRACT);

output[17:

0]BCOUT;

output[47:

0]P,PCOUT;//

input[17:

0]A,B;//

input[47:

0]C,PCIN;

input[1:

0]CARRYINSEL;

input[6:

0]OPMODE;

inputBCIN,CARRYIN,CEA,CEB,CEC,CECARRYIN,CECINSUB,CECTRL,CEM,

CEP,CLK,RSTA,RSTB,RSTC,RSTCARRYIN,RSTM,RSTP,SUBTRACT;

//对DSP48原语的功能进行配置。

DSP48#(

.AREG

(1),//NumberofpipelineregistersontheAinput,0,1or2

.BREG

(1),//NumberofpipelineregistersontheBinput,0,1or2

.B_INPUT("DIRECT"),

//BinputDIRECTfromfabricorCASCADEfromanotherDSP48

.CARRYINREG

(1),

//NumberofpipelineregistersfortheCARRYINinput,0or1

.CARRYINSELREG

(1),

//NumberofpipelineregistersfortheCARRYINSEL,0or1

.CREG

(1),//NumberofpipelineregistersontheCinput,0or1

.LEGACY_MODE("MULT18X18S"),

//Backwardcompatibility,NONE,MULT18X18orMULT18X18S

.MREG

(1),//Numberofmultiplierpipelineregisters,0or1

.OPMODEREG

(1),//NumberofpipelineregsitersonOPMODEinput,0or1

.PREG

(1),//NumberofpipelineregistersonthePoutput,0or1

.SUBTRACTREG

(1)

//NumberofpipelineregistersontheSUBTRACTinput,0or1

)fpga_v4_dsp48(

.BCOUT(BCOUT),//18-bitBcascadeoutput

.P(P),//48-bitproductoutput

.PCOUT(PCOUT),//48-bitcascadeoutput

.A(A),//18-bitAdatainput

.B(B),//18-bitBdatainput

.BCIN(BCIN),//18-bitBcascadeinput

.C(C),//48-bitcascadeinput

.CARRYIN(CARRYIN),//Carryinputsignal

.CARRYINSEL(CARRYINSEL),//2-bitcarryinputselect

.CEA(CEA),//Adataclockenableinput

.CEB(CEB),//Bdataclockenableinput

.CEC(CEC),//Cdataclockenableinput

.CECARRYIN(CECARRYIN),//CARRYINclockenableinput

.CECINSUB(CECINSUB),//CINSUBclockenableinput

.CECTRL(CECTRL),//ClockEnableinputforCTRLregsiters

.CEM(CEM),//ClockEnableinputformultiplierregsiters

.CEP(CEP),//ClockEnableinputforPregsiters

.CLK(CLK),//Clockinput

.OPMODE(OPMODE),//7-bitoperationmodeinput

.PCIN(PCIN),//48-bitPCINinput

.RSTA(RSTA),//ResetinputforApipelineregisters

.RSTB(RSTB),//ResetinputforBpipelineregisters

.RSTC(RSTC),//ResetinputforCpipelineregisters

.RSTCARRYIN(RSTCARRYIN),//ResetinputforCARRYINregisters

.RSTCTRL(RSTCTRL),//ResetinputforCTRLregisters

.RSTM(RSTM),//Resetinputformultiplierregisters

.RSTP(RSTP),//ResetinputforPpipelineregisters

.SUBTRACT(SUBTRACT)//SUBTRACTinput

);

endmodule

3.4.2时钟组件

时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通I/O本地的时钟缓冲器以及高级数字时钟管理模块,如表3-7所示。

表3-7时钟组件的清单

下面对几个常用时钟组件进行简单介绍,其余组件的使用方法是类似的。

1.BUFG

BUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其和同类原语的RTL结构如图3-28所示。

全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG组件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。

如果要对全局时钟实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。

其例化的代码模板如下所示:

//BUFG:

全局时钟缓存(GlobalClockBuffer),只能以内部信号驱动

//XilinxHDL库向导版本,ISE9.1

BUFGBUFG_inst(

.O(O),//时钟缓存输出信号

.I(I)///时钟缓存输入信号

);

//结束BUFG_ins模块的例化过程

在综合结果分析中,其和同类原语的RTL结构如图3-32所示。

图3-32全局时钟原语的RTL级结构示意图

2.BUFMUX

BUFMUX是全局时钟复用器,选择两个输入时钟I0或I1中的一个作为全局时钟,其和同类原语BUFMUX1的RTL级结构如图M所示。

当选择信号S为低时,选择I0;否则输出I1,其真值表如表M所示。

BUFMUX原语和BUFMUX1原语的功能一样,只是选择逻辑不同,对于BUFMUX1,当选择信号S为低时,选择I1;否则输出I0。

BUFMUX原语的例化代码模板如下所示:

BUFMUX原语的例化代码模板如下所示:

//BUFGMUX:

全局时钟的2到1复用器(GlobalClockBuffer2-to-1MUX)

//适用芯片:

Virtex-II/II-Pro/4/5,Spartan-3/3E/3A

//XilinxHDL库向导版本,ISE9.1

BUFGMUXBUFGMUX_inst(

.O(O),//时钟复用器的输出信号

.I0(I0),//0时钟输入信号

.I1(I1),//1时钟输入信号

.S(S)//时钟选择信号

);

//结束BUFGMUX_inst模块的例化过程

需要注意的是:

该原语只用用全局时钟处理,不能作为接口使用。

在综合结果分析时,它和同类原语BUFMUX1的RTL级结构如图3-33所示。

图3-33全局时钟复用器的RTL级结构示意图

3.BUFIO

BUFIO是本地I/O时钟缓冲器,其RTL结构如图M所示,只有一个输入与输出,非常简单。

BUFIO使用独立于全局时钟网络的专用时钟网络来驱动纵向I/O管脚,所以非常适合同步数据采集。

BUFIO要求时钟和相应的I/O必须在同一时钟区域,而不同时钟网络的驱动需要BUFR原语来实现。

需要注意的是,由于BUFIO引出的时钟只到达了I/O列,所以不能来驱动逻辑资源,如CLB和块RAM。

BUFIO的例化代码模板如下:

//BUFIO:

本地I/O时钟缓冲器(LocalClockBuffer)

//适用芯片:

Virtex-4/5

//XilinxHDL库向导版本,ISE9.1

BUFIOBUFIO_inst(

.O(O),//本地I/O时钟缓冲器的输出信号

.I(I)//本地I/O时钟缓冲器的输入信号

);

//结束BUFIO模块的例化过程

在综合结果分析时,其RTL级结构如图3-34所示。

图3-34本地I/O时钟缓冲器的RTL级结构示意图

4.BUFR

BUFR是本地I/O时钟、逻辑缓冲器,其RTL结构如图M所示。

BUFR和BUFIO都是将驱动时钟引入某一时钟区域的专用时钟网络,而独立于全局时钟网络;不同的是,BUFR不仅可以跨越不同的时钟区域(最多3个),还能够驱动I/O逻辑以及自身或邻近时钟区域的逻辑资源。

BUFIO的输出和本地内部互联都能驱动BUFR组件。

此外,BUFR能完成输入时钟1~8的整数分频。

因此,BUFR是同步设计中实现跨时钟域以及串并转换的最佳方式。

BUFIO的例化代码模板如下:

//BUFR:

本地I/O时钟、逻辑缓冲器(RegionalClockBuffer)

//适用芯片:

Virtex-4/5

//XilinxHDL库向导版本,ISE9.1

BUFR#(

.BUFR_DIVIDE("BYPASS"),

//分频比,可选择"BYPASS","1","2","3","4","5","6","7","8"。

.SIM_DEVICE("VIRTEX4")

//指定目标芯片,"VIRTEX4"或者"VIRTEX5"

)BUFR_inst(

.O(O),//时钟缓存输出信号

.CE(CE),//时钟使能信号,输入信号

.CLR(CLR),//时钟缓存清空信号

.I(I)//时钟缓存输入信号

);

//结束BUFR模块的例化过程

需要注意的是:

BUFIO和BUFR只能在Virtex-4系列以及更高系列芯片中使用。

在综合结果分析时,其RTL结构如图3-35所示。

图3-35本地I/O时钟、逻辑缓冲器的RTL级结构示意图

5.DCM_BASE

DCM_BASE是基本数字时钟管理模块的缩写,是相位和频率可配置的数字锁相环电路,常用于FPGA系统中复杂的时钟管理。

如果需要频率和相位动态重配置,则可以选用DCM_ADV原语;如果需要相位动态偏移,可使用DCM_PS原语。

DCM系列原语的RTL结构如图3-8所示。

模块接口信号的说明如表3-8所列。

DCM_BASE组件可以通过Xilinx的IPWizard向导产生,也可以直接通过下面的例化代码直接使用。

其Verilog的例化代码模板为:

//DCM_BASE:

基本数字时钟管理电路(BaseDigitalClockManagerCircuit)

//适用芯片:

Virtex-4/5

//XilinxHDL库向导版本,ISE9.1

DCM_BASE#(

.CLKDV_DIVIDE(2.0),

//CLKDV分频比可以设置为:

1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5

//7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0or16.0

.CLKFX_DIVIDE

(1),//Canbeanyintegerfrom1to32

//CLKFX信号的分频比,可为1到32之间的任意整数

.CLKFX_MULTIPLY(4),

//CLKFX信号的倍频比,可为2到32之间的任意整数

.CLKIN_DIVIDE_BY_2("FALSE"),

//输入信号2分频的使能信号,可设置为TRUE/FALSE

.CLKIN_PERIOD(10.0),

//指定输入时钟的周期,单位为ns,数值范围为1.25~1000.00。

.CLKOUT_PHASE_SHIFT("NONE"),

//指定移相模式,可设置为NONE或FIXED

.CLK_FEEDBACK("1X"),

//指定反馈时钟的频率,可设置为NONE、1X或2X。

相应的频率关系都是针对CLK0而言的。

.DCM_PERFORMANCE_MODE("MAX_SPEED"),

//DCM模块性能模式,可设置为MAX_SPEED或MAX_RANGE

.DESKEW_ADJUST("SYSTEM_SYNCHRONOUS"),

//抖动调整,可设置为源同步、系统同步或0~15之间的任意整数

.DFS_FREQUENCY_MODE("LOW"),

//数字频率合成模式,可设置为LOW或HIGH两种频率模式

.DLL_FREQUENCY_MODE("LOW"),

//DLL的频率模式,可设置为LOW、HIGH或HIGH_SER

.DUTY_CYCLE_CORRECTION("TRUE"),

//设置是否采用双周期校正,可设为TRUE或FALSE

.FACTORY_JF(16'hf0f0),

//16比特的JF因子参数

.PHASE_SHIFT(0),

//固定相移的数值,可设置为-255~1023之间的任意整数

.STARTUP_WAIT("FALSE")

//等DCM锁相后再延迟配置DONE管脚,可设置为TRUE/FALSE

)DCM_BASE_inst(

.CLK0(CLK0),//0度移相的DCM时钟输出

.CLK180(CLK180),//180度移相的DCM时钟输出

.CLK270(CLK270),//270度移相的DCM时钟输出

.CLK2X(CLK2X),//DCM模块的2倍频输出

.CLK2X180(CLK2X180),//经过180度相移的DCM模块2倍频输出

.CLK90(CLK90),//90度移相的DCM时钟输出

.CLKDV(CLKDV),//DCM模块的分频输出,分频比为CLKDV_DIVIDE

.CLKFX(CLKFX),//DCM合成时钟输出,分频比为(M/D)

.CLKFX180(CLKFX180),//180度移相的DCM合成时钟输出

.LOCKED(LOCKED),//DCM锁相状态输出信号

.CLKFB(CLKFB),//DCM模块的反馈时钟信号

.CLKIN(CLKIN),//DCM模块的时钟输入信号

.RST(RST)//DCM模块的异步复位信号

);

//结束DCM_BASE模块的例化过程

在综合结果分析时,DCM系列原语的RTL结构如图3-36所示。

图3-36DCM模块的RTL级结构示意图

3.4.3配置和检测组件

配置和检测组件提供了FPGA内部逻辑和JTAG扫描电路之间的数据交换以及控制功能,只要由6个原语组成,如表3-9所示。

表3-9配置和检测原语列表

下面对BSCAN_VIRTEX4组件进行简单介绍,其余组件的使用方法是类似的。

1.BSCAN_VIRTEX4

当JTAGUSER1/2/3/4指令被加载后,BSCAN_VIRTEX4允许设计人员来检测TCK、TMS以及TDI等专用JTAG管脚的数据,并且可以将用户数据写入到TDO管脚上,这样可以在PC上通过JTAG链读取芯片内部的用户数据。

BSCAN_VIRTEX4的管脚信号说明如下:

CAPTURE:

位宽为1的输出信号,用于指示是否加载了用户指令,当JTAG接口处于CAPTURE-DR状态时,输出为高。

DRCK:

位宽为1的输出信号,用于监测JTAG电路的TCK信号。

当JTAG链路处于用户指令模式或者JTAG接口为SHIFT-DR状态时,才有信号输出。

RESET:

位宽为1的输出信号,在加载用户指令时有效。

当JTAG接口控制器处于TEST-LOGIC-RESET状态时置高。

SEL:

位宽为1的输出信号,高有效。

用于指示USER1数据是否加载到JTAG指令寄存器中。

在UPDATE-IR状态时有效,直到加载新的指令之前,一直保持有效电平。

SHIFT:

位宽为1的输出信号,加载用户指令时有效。

当JTAG接口控制器处于SHIFT-DR状态时置高。

TDI:

位宽为1的输出信号,用于检测JTAG链的TDI信号。

UPDATE:

位宽为1的输出信号,加载USER1指令和USER2指令时有效。

当JTAG接口控制器处于UPDATE-DR状态时置高。

TDO:

位宽为1的输入信号,可以将外部JTAG链的TDO信号直接连到该管脚上。

在Virtex-4芯片中,有4个BSCAN_VIRTEX4硬件原语可用。

因此,其属性JTAG_CHAIN的有效值为1~4,默认值为1。

BSCAN_VIRTEX4原语的例化代码模板如下所示:

// BSCAN_VIRETX4:

完成内部逻辑和JTAG接口连接的边界扫描原语(BoundaryScanprimitiveforcon