quarters加法器实验报告.docx

《quarters加法器实验报告.docx》由会员分享,可在线阅读,更多相关《quarters加法器实验报告.docx(11页珍藏版)》请在冰豆网上搜索。

quarters加法器实验报告

加法器数字逻辑实验报告

一、实验目的

1.熟悉QuartusII软件的基本操作,了解各种设计方法(原理图设计、文本设计、波形设计)

2.用VHDL语言设计一个加法器。

3.用VHDL语言设计串行加法器、并行加法器。

二、实验内容

1、熟悉QuartusⅡ软件的基本操作,了解各种设计输入方法(原理图设计、文本设计、波形设计)

2、用VHDL语言设计加法器、串行全加器、并行全加器,再利用波形编辑区进行逻辑功能仿真,以此验证电路的逻辑功能是否正确,最终在FPGA芯片上下载验证逻辑实现。

三、实验原理

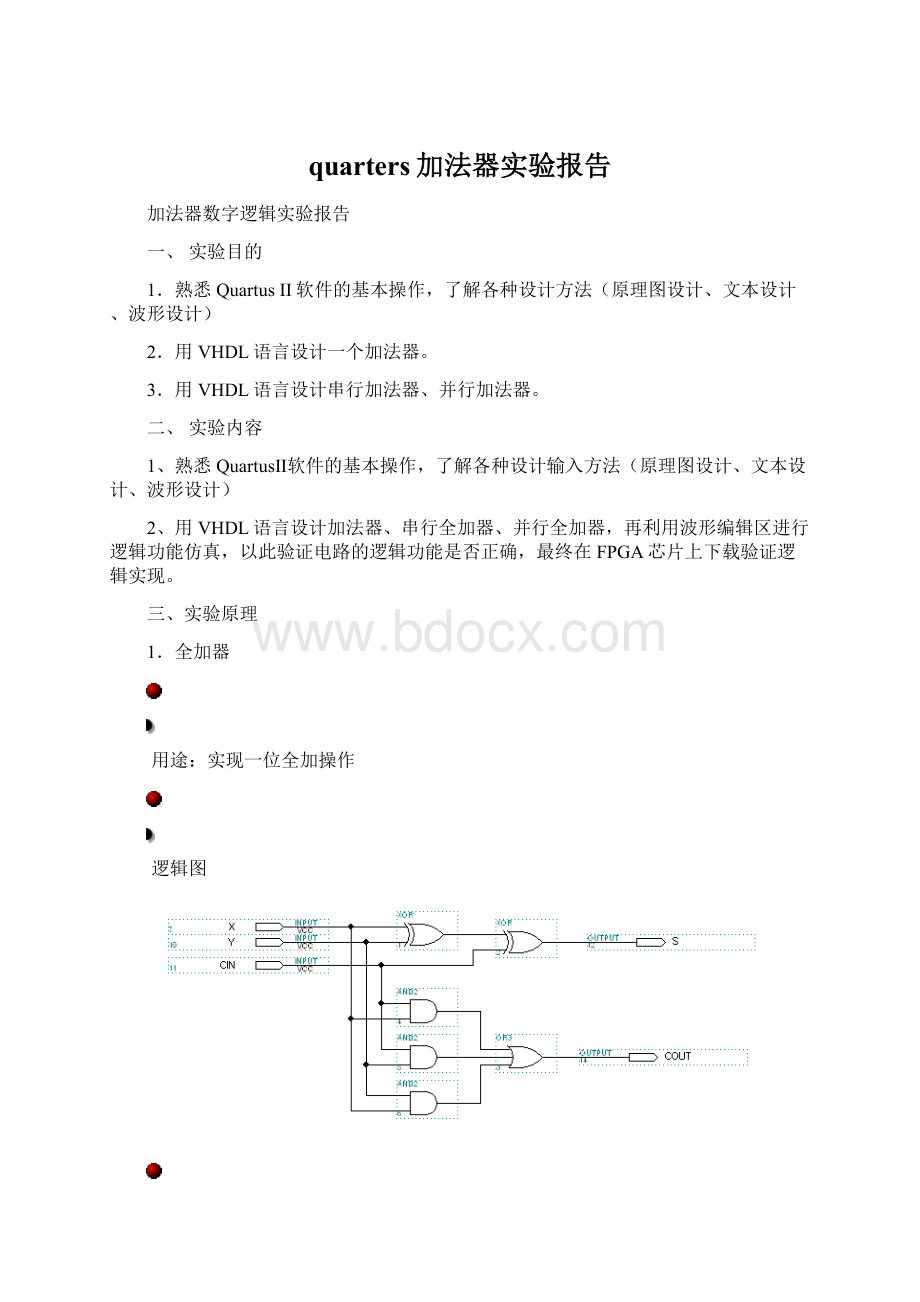

1.全加器

用途:

实现一位全加操作

逻辑图

真值表

X

Y

CIN

S

COUT

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

VHDL程序

数据流描述:

波形图

2.四位串行加法器

逻辑图

波形图

3.74283:

4位先行进位全加器(4-BitFullAdder)

逻辑框图

逻辑功能表

注:

1、输入信号和输出信号采用两位对折列表,节省表格占用的空间,如:

[A1/A3]对应的列取值相同,结果和值[Σ1/Σ3]对应的运算是Σ1=A1+B1和Σ3=A3+B3。

请自行验证一下。

2、C2是低两位相加产生的半进位,C4是高两位相加后产生的进位输出,C0是低位级加法器向本级加法器的进位输入。

四、实验方法与步骤

实验方法:

采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是AlteraEPF10K20TI144_4的FPGA电路板。

实验步骤:

1、

建立工程project,并命名顶层文件为JFQ,按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assignment/Device,选取芯片的类型。

选择“FLEX10K——EPF10K20TI144_4”

2、编写VHDL源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个VHDL文件。

编写的文件名与实体名一致且为JFQ。

VHDL如下:

3、

编译与调试。

确定源代码文件为当前工程文件,点击Processing/ComplierTool进行文件编译。

编译结果有错误或警告,则将要调试修改直至文件编译成功。

4、波形图。

在编译成功后,新建一个波形文件VectorWaveformFile开始设计波形。

点击Edit/Insert/Insertnodeorbus,按照程序所述插入节点。

设置endtime为2μs,网格大小为100ns。

设置x,y,cin的输入波形,cin的输入波形为网格大小200ns的“01”连续时钟变化信号,y的输入波形为网格大小100ns的“01”连续时钟变化信号,x的输入波形为网格大小100ns的“01”连续时钟变化信号。

点击Processing\GenerateFunctionalSimulationNetlist,创建仿真时序网表。

然后在Assingment\setting中选择SimulatorSettings——Functional,再点击StartSimulation进行功能仿真。

6、FPGA芯片编程及验证。

首先进行管脚锁定。

点击Assignment\Pins进入管脚锁定窗口,将x、y、cin锁定到三个输入管脚,cout、s锁定到两个输出管脚。

点击Processing/ComplierTool进行编译,成功后就即可将程序下载到芯片。

把电路板连接到电脑上,点击Tools\Programmer,进入下载到芯片窗口,选择好硬件及驱动后就可以点击Start进行下载了。

7、建立工程CXSWQJQ,并命名顶层文件为CXSWQJQ,重复第一步;

8、

编写VHDL源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致且为CXSWQJQ,点击File/Saveas以“.vhd”为扩展名存盘文件。

VHDL设计源代码如下:

9、将加法器的VHDL文件引入顶层文件夹中,与此VHDL文件一起重复3-6步;

10、建立工程BXSWQJQ,并命名顶层文件为BXSWQJQ,重复第一步;

11、

编写VHDL源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致且为BXSWQJQ,点击File/Saveas以“.vhd”为扩展名存盘文件。

VHDL设计源代码如下:

12、将加法器的VHDL文件引入顶层文件夹中,与此VHDL文件一起重复3-6步;

五、实验结果与分析

1、编译过程

a)编译过程、调试结果

2、写好的VHDL文件要先点击Processing\AnalyzeCurrentFile分析当前文件,成功后进行语法编译Processing\Start\StartAnalyze&Synthesis。

若编译出错,则检查代码,进行调试,再进行以上操作,直至成功。

b)结果分析及结论

代码结构语法均正确,故编译通过。

3、功能仿真

a)加法器:

b)串行加法器:

c)并行加法器

4、Programming芯片编程

a)芯片编程过程

首先进行管脚锁定,一些验证内容并行和串行基本相同,只列一次,又由于串并行加法器是加法器的组合结果,因此如果这一验证正确也可以表面加法器的验证正确。

点击Processing\CompilerTool进行编译,显示成功。

之后可以将程序下载到芯片。

添加硬件,选择驱动。

点击Start开始下载验证。

b)编程芯片FPGA验证结果与分析

打开70、69、51、49管脚,即X输入3,Y输入12,CIN输入0;99、98、97、96管脚亮起,108管脚不亮,即S输出16,不进位。

打开70、67、60、59、49管脚,即X输入9,Y输入13,CIN输入6;98、97管脚亮起,108管脚亮,即S输出6,进位。

c)结果分析与结论

当只打开部分输入管脚时,输入X\Y信号时,输出的S为X+Y或X+Y-16的值,COUT为进位情况。

经多次在电路板上的试验,证明工程实现了串行(并行)加法器的功能。

六、实验结论

实验总结

仿真和下载验证都成功,反应出程序设计的正确性。

成功的用VHDL语言实现了加法器、串行加法器、并行加法器。

实验心得

通过实验,我对QuartusⅡ的操作更加熟练了。

实验过程中需要多次进行编译,波形仿真是也需要多次见网格,有时忘记一步后面就无法成功。

利用波形图进行仿真的功能是非常有用的,将仿真结果、芯片验证结果和真值表进行比较,就能确定工程的正确性。

这次的实验其实十分简单,但却为以后的复杂实验做了铺垫,必须要理解好以及熟练运用软件的功能。