lvdslvpeclcml之间的电路和参数.docx

《lvdslvpeclcml之间的电路和参数.docx》由会员分享,可在线阅读,更多相关《lvdslvpeclcml之间的电路和参数.docx(13页珍藏版)》请在冰豆网上搜索。

lvdslvpeclcml之间的电路和参数

LVDS到LVPECL信号之间的连接

LVDS到LVPECL得连接也分为直流耦合和交流耦合两种方式。

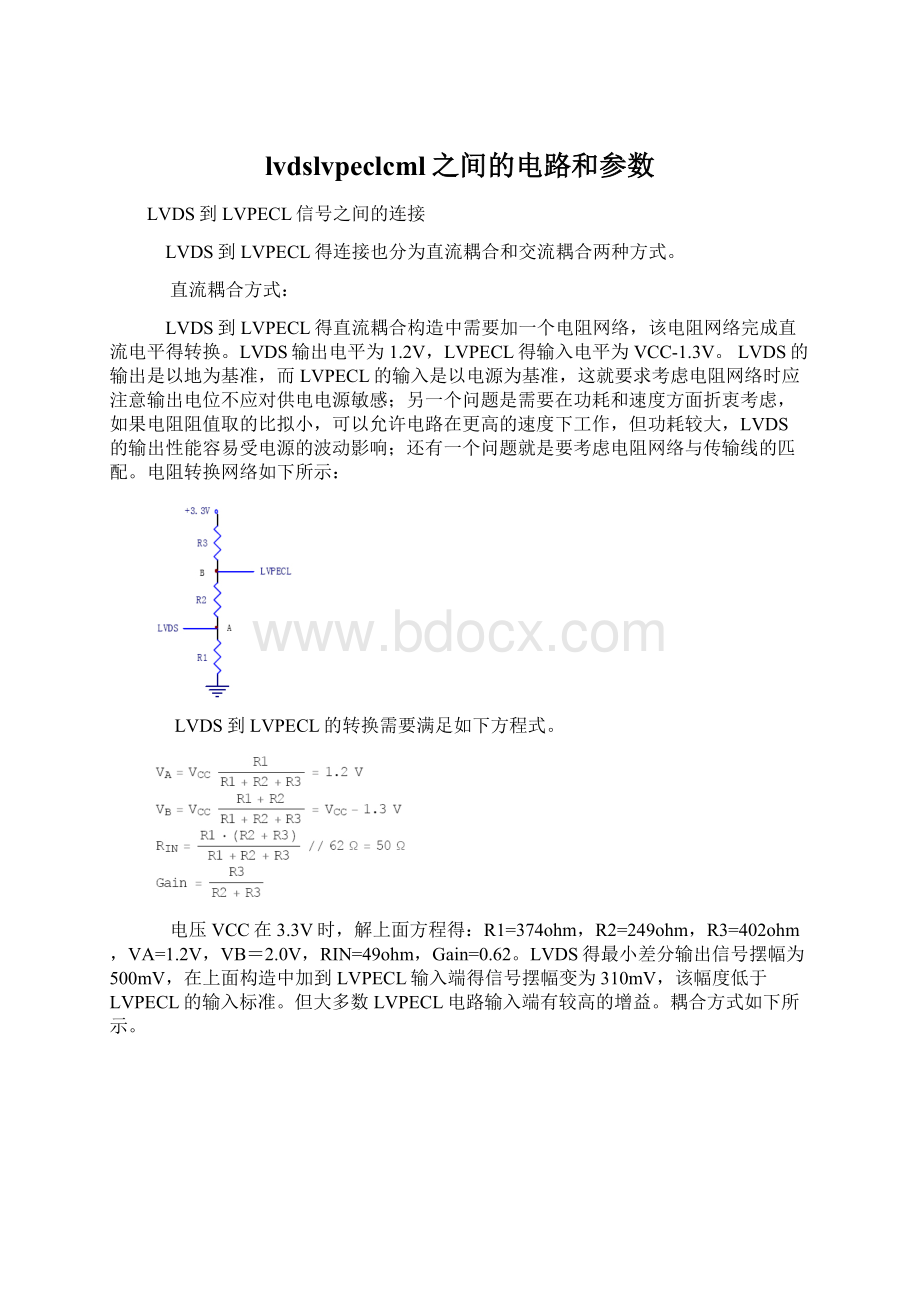

直流耦合方式:

LVDS到LVPECL得直流耦合构造中需要加一个电阻网络,该电阻网络完成直流电平得转换。

LVDS输出电平为1.2V,LVPECL得输入电平为VCC-1.3V。

LVDS的输出是以地为基准,而LVPECL的输入是以电源为基准,这就要求考虑电阻网络时应注意输出电位不应对供电电源敏感;另一个问题是需要在功耗和速度方面折衷考虑,如果电阻阻值取的比拟小,可以允许电路在更高的速度下工作,但功耗较大,LVDS的输出性能容易受电源的波动影响;还有一个问题就是要考虑电阻网络与传输线的匹配。

电阻转换网络如下所示:

LVDS到LVPECL的转换需要满足如下方程式。

电压VCC在3.3V时,解上面方程得:

R1=374ohm,R2=249ohm,R3=402ohm,VA=1.2V,VB=2.0V,RIN=49ohm,Gain=0.62。

LVDS得最小差分输出信号摆幅为500mV,在上面构造中加到LVPECL输入端得信号摆幅变为310mV,该幅度低于LVPECL的输入标准。

但大多数LVPECL电路输入端有较高的增益。

耦合方式如下所示。

交流耦合方式:

LVPECL芯片内有直流偏置情况:

LVPECL芯片内没有直流偏置情况:

LVPECL信号到LVDS信号之间的连接

LVPECL到LVDS的连接方式有直流耦合和交流耦合两种方式。

直流耦合方式:

LVPECL到LVDS的直流耦合构造需要一个电阻网络,设计网络时需要考虑以下几点:

首先,我们知道当负载是50ohm接到VCC-2V时,LVPECL的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL输出信号经衰减后仍能落在LVDS的有效输入X围内。

注意LVDS的输入差分阻抗为100ohm,或者每个单端到虚拟地为50ohm,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等。

分压电阻网络如下所示:

要完成由LVPECL到LVDS的逻辑转换,需要满足如下方程式。

解方程得:

R1=182ohm,R2=48ohm,R3=48ohm,VA=1.14V,RAC=51.8ohm,RDC=62.8ohm,Gain=0.337。

连接方式如下:

交流耦合情况:

LVPECL到LVDS的交流耦合如下列图所示,LVPECL的输出端到地需加直流偏置电阻(142ohm到200ohm),同时信号通道上一定要串接50ohm电阻,以提供一定衰减。

LVDS的输入端到地需加5Kohm电阻,以提供近似0.86V的共模电压。

LVPECL与LVPECL信号之间的连接

LVPECL与LVPECL信号之间的连接分为直流耦合方式和交流耦合方式两种。

直流耦合方式:

直流耦合时,LVPECL负载一般考虑是通过50ohm接到VCC-2V的电源上,一般该电源是不存在的,因此通常的做法是利用电阻分压网络做等效电路。

等效网络如下列图所示:

上图中,各器件应满足如下方程式:

c:

\iknow\docshare\data\cur_work\\batch.download.php?

aid=12556

在3.3V供电时,电阻按5%精度选取,R1为130ohm,R2为82ohm。

而在5V供电时,R1为82ohm,R2为130ohm。

如下列图所示:

交流耦合方式:

LVPECL在交流耦合输出到50ohm的终端负载时,要考虑LVPECL的输出端加一直流偏置电阻。

LVPECL的输出工模电压需固定在VCC-1.3V,在选择直流偏置电阻时仅需该电阻能够提供14mA到地的通路,这样R1=(VCC-1.3V)/14mA。

在3.3V供电时,R1=142ohm,5V供电时,R1=270ohm。

然而这种方式给出的交流负载阻抗低于50ohm,在实际应用种,3.3V供电时,R1可以从142ohm到200ohm之间选取,5V供电时,R1可以从270ohm到350ohm之间选取,原那么是让输出波形到达最正确。

交流耦合方式如下列图所示:

上图中应满足如下公式:

由上面的公式可知,此种耦合方式的直流功耗比拟大,如果对功耗有要求时,可以用(b)所示电路。

计算如下:

LVPECL交流耦合另外有两种改良构造,一种是在信号通路上串接一个电阻,从而可以增大负载阻抗使之接近50ohm;另一种方式是在直流偏置通道上串接电感,以减小该偏置通道影响交流阻抗。

LVPECL信号原理

c:

\iknow\docshare\data\cur_work\\batch.download.php?

aid=12515 LVPECL即LowVoltagePositiveEmitter-CoupleLogic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源,LVPECL是由PECL演变而来的,PECL即PositiveEmitter-CoupleLogic,也就是正发射极耦合逻辑的意思,使用5.0V电源,而PECL是由ECL演变而来的,ECL即Emitter-CoupleLogic,也就是发射极耦合逻辑,ECL有两个供电电压VCC和VEE。

当VEE接地时,VCC接正电压时,这时的逻辑称为PECL;当当VCC接地时,VEE接负电压时,这时的逻辑成为NECL,VEE一般接-5.2V电源;一般狭义的ECL就是指NECL。

ECL分类:

c:

\iknow\docshare\data\cur_work\\batch.download.php?

aid=12515

ECL/PECL/LVPECL逻辑的优点:

1. 输出阻抗低(6~8ohm),输出阻抗高(可以看作无穷大),所以驱动能力特别强,它可以驱动50~130ohm特征阻抗的传输线而交流特性并没有明显的改变。

由于驱动能力强,所以支持更远距离的传输,所以背板走线或长线缆传输根本上都使用ECL逻辑。

2. ECL器件对电压和温度的变化不如TTL和CMOS器件敏感,ECL时钟驱动器产生的各路时钟的并发性更好,skew更小。

3. 相对于同为差分信号的LVDS,ECL支持的速率更高,受工艺的限制,LVDS的逻辑很少有高于1.5GHz的应用,而ECL可以应用高于10GHz的场合,可以说,高于5GHz的场合,根本上是ECL和CML的天下。

在所有的数字电路中,ECL的工作速度最高,其延时小于1ns,在中小规模集成电路,高速,超高速数字系统和设备中应用

4. 对传输线阻抗的适应X围更宽。

LVDS属于电流型驱动,其终端的100ohm匹配电阻兼有产生电压的功能。

因此,为了不改变信号的摆幅,终端电阻的阻值必须取100ohm,为了保证较好的信号完整性,LVDS的传输线阻抗也必须准确控制在50ohm,否那么容易产生反射等SI问题。

ECL/PECL/LVPECL逻辑的缺点:

跟它的优点一样,ECL的缺点也很明显,那就是功耗大,噪声容限小,抗干扰能力弱。

ECL电路的逻辑摆幅只有0.8V,直流噪声容限只有200mV。

可以说,ECL的高速性能是用高功耗、低噪声容限为代价换来的。

PECL的标准输出负载是50ohm至VCC-2V的电平上,在这种负载条件下,OUT+与OUT-的静态电平典型值为VCC-1.3V,OUT+与OUT-的输出电流为14mA。

PECL的输出电路构造:

PECL的输入是一个具有高输入阻抗的差分对,该差分对的共模电压需要偏置到VCC-1.3V,这样允许的输入信号电平动态最大。

有的芯片在内部已经集成了偏置电路,使用时直接连接即可,有的芯片没有加,使用时需要在芯片外部加直流偏置。

PECL的输入电路构造:

PECL的逻辑电平指标:

LVDS信号原理

LVDS即LowVoltageDifferentialSignaling的缩写,是当今流行最广泛的低压差分信号之一,它具有功耗低、抗扰性好,最新的LVDS标准能够实现3Gbps以上的数据速率。

LVDS信号的摆幅只有350mV。

3.3VLVDS线驱动器的输入电平对于逻辑0为0.0VDC到0.8VDC、对于逻辑1为2.0VDC到3.0VDC。

0.8VDC和2.0VDC之间的输入电平公平定义,这意味着驱动的开关转换阈值电平也未定义。

LVDS驱动器中含有一个3.5mA的电流源,接收端的输入阻抗很高,所以,整个电路电流全部流过100Ω垮接电阻,于是在垮接电阻上产生了350mV的电压。

改变电流的方向即可在垮接电阻上产生相反方向的电压,以这种方式来产生逻辑1和0。

LVDS的优点:

1. 由于LVDS的电流源始终导通,此特性可以消除开关噪声带来的尖峰和大电流晶体管不断开合造成的EMI干扰。

2. 差分线的间距很短,受到的干扰一样,所以在接收端进展差模运算后,干扰正好抵消。

3. LVDS差分线中传输的电流一样,方向相反,产生的EMI很低。

CML与CML信号的连接:

CML到CML之间的连接分为两种情况,当收发两端的器件使用一样的电源时,CML到CML可以采用直流耦合方式,这时不需要加任何器件;当收发两端器件采用不同电源时,一般要考虑交流耦合,注意这时选用的耦合电容要足够大,以防止在较长连0或连1情况出现时,接收端差分电压变小。

:

]txB$w;o-r/~#h5YE0

直流耦合:

p&N;`q+J'D;]m0

t,VRsam&d,N,V0 交流耦合:

中国通信人博客1WouWQL:

H

F6x(FT"t0 中国通信人博客H$[-~!

Y'mq"T

LVDS到LVDS信号的连接:

中国通信人博客{Ni4hcg5I$e

F

因为LVDS的输入与输出都是内部匹配的,所以LVDS间的连接可以直接连接。

中国通信人博客kFXR,r'u:

q8H]

Zbrn,?

)Gh.FZ0

CML与LVDS的连接:

中国通信人博客(RY,Bm&?

1\0j

中国通信人博客e0h1f\)O3UO4M一般情况下,实际应用中没有CML和LVDS进展互联的情况,因为LVDS通常用作并联数据的传输,数据速率为155MHz,622MHz,或1.25GHz,而CML常用来做串行数据的传输,传输速率为2.5GHz或10GHz。

作为特殊情况,下面给出他们互联的解决方案。

DO'Z*rR5B0 中国通信人博客G&vrIB-s;lh

LVDS到CML的连接:

中国通信人博客)M'M6C)y8d2uo9{O

UZ&W8v_'A?

?

T0

CML到LVDS的连接:

中国通信人博客,}c\*CrE[y'[

中国通信人博客N*Qt2MYcB2G~

中国通信人博客Ys.tZ:

G/Sqh

LVPECL与CML的连接有直流和交流两种耦合方式。

uQW;U.a#Y01USJ#y6m_e-p0 交流耦合方式:

中国通信人博客oI)|&sXE5C

在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取X围可以从142ohm到200ohm。

如果LVPECL的输出信号摆幅大于CML的接收X围,可以在信号通道上串接一个25ohm的电阻,这时CML输入端的电压摆幅变为原来的0.67倍。

交流耦合方式如下列图所示:

中国通信人博客&FZD?

w{CJhR0Ex

"|G

C:

K|0ZIrjj0

%o2y}1[#H6h0 +?

MER~0 直流耦合情况:

EO$`9|7.A`#m7O0

在LVPECL到CML的直流耦合连接方式中需要一个电平转换网络,该电平转换网络的作用是匹配LVPECL的输出与CML的输入共模电压。

一般要求该电平转换网络引入的损耗要小,以保证LVPECL的输出经过衰减后仍能满足CML输入灵敏度的要求;另外还要求来自LVPECL端看到的负载阻抗近似为50ohm。

下列图为电平转换网络。

中国通信人博客2GT&w1VnYXXQ

o4BY:

_TP$Us4J.Ud0

中国通信人博客`5M3n,fA*m"_&J$c

CUl"}`0 该电阻转换网络必须满足如下方程式:

中国通信人博客P&L9d+X7Gy.[

+G;X5wE"M&FY/l0E0

0e.U2~eiV(`0 中国通信人博客2"Y

LU7z?

求解上面的方程组,得到R1=182ohm,R2=82ohm,VA=1.35V,VB=3.11V,Gain=0.147,Zin=49ohm。

直流耦合方式如下列图所示:

中国通信人博客fm'Y_,b/B4mA-m

6B+AV7]6Ks0

CML即CurrentModeLogic,也就是电流模式逻辑,CML电路主要靠电流驱动,可以说CML是所有高速数据接口形式中最简单的一种,它的输入与输出是匹配好的,从而减少了外围器件,使用时直接连接就可以,根本上不需要在IC外面做匹配,此特点使单板硬件设计更简单,单板看起来更简洁,CML的摆幅较小,功耗比拟低。

HJ)Jc$g"gS/K0_0]!

Ro;Z}yU7F0 CML输出构造:

5N!

]0d*bn)?

v9w0

中国通信人博客^VwWJ/MQxLa

中国通信人博客,q!

g$J5\:

w2S'W0Ls^

如上图所示,CML的输出电路形式是一个差分对,该差分对的集电极电阻为50ohm,输出信号的上下电平切换是靠共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为16mA,假定CML的输出负载为一50ohm上拉电阻,那么单端CML输出信号的摆幅为VCC~VCC-0.4V。

在这种情况下,差分输出信号摆幅为800mV,共模电压为VCC-0.2V。

假设CML输出采用交流耦合至50ohm负载,这时的直流阻抗由集电极电阻决定,为50ohm,CML输出工模电压变为VCC-0.4V,差分信号摆幅仍为800mV。

*R6emd+slBi|0 CML波形:

w+v^|/J6lZ5D^2u"r0

中国通信人博客$J6^\8U3O:

Fg~Es

kXW~%[/Eh;n'?

0 CML的输入一般都是片内匹配好的,50ohm上拉到VCC,而且大局部是交流耦合。

中国通信人博客d0x9Z+`2S)\4g+{

MEM1]0mQ0sq[)Y0 CML的输入构造:

m^G#UlU'SegX}0rL[p;QOKM*^~0

中国通信人博客#B|zB;Tn1x0[3H

中国通信人博客1\X"{Ekn4RCML的摆幅一般在600mV-100mV之间,典型值为800mV。

:

A6f5Cdx5p6X08RkZ2yQJ5~[uO0

CML逻辑参数:

*AG^:

x6y.\F6?

0s2N-V-zC.\Z7T0

中国通信人博客)C"XQ+[n

TH#`N!

Tm6bcG0 CML的优点是功耗低,速度高,但是驱动能力不如LVPECL,传输距离也没有ECL远。

o0z!

Pv(A9SN8q"y

{0 中国通信人博客1N;t&z-^+Un

LVPECL/LVDS/CML三种逻辑比拟:

[CP$`,j

G3imQ

t0Ts1m,o)N^0

中国通信人博客k8AM_7VjK)qLt5{

中国通信人博客T+I7f6[eC;L

中国通信人博客GMnQL?

M