计算机组成原理实验报告单周期CPU的设计与实现.docx

《计算机组成原理实验报告单周期CPU的设计与实现.docx》由会员分享,可在线阅读,更多相关《计算机组成原理实验报告单周期CPU的设计与实现.docx(46页珍藏版)》请在冰豆网上搜索。

计算机组成原理实验报告单周期CPU的设计与实现

电子科技大学计算机科学与工程学院

标准实验报告

(实验)课程名称:

计算机组成原理实验

电子科技大学教务处制表

电子科技大学

实验报告

学生姓名:

郫县尼克杨学号:

2014666666666指导教师:

陈虹

实验地点:

主楼A2-411实验时间:

12周-15周

一、实验室名称:

主楼A2—411

二、实验项目名称:

单周期CPU的设计与实现。

三、实验学时:

8学时

四、实验原理:

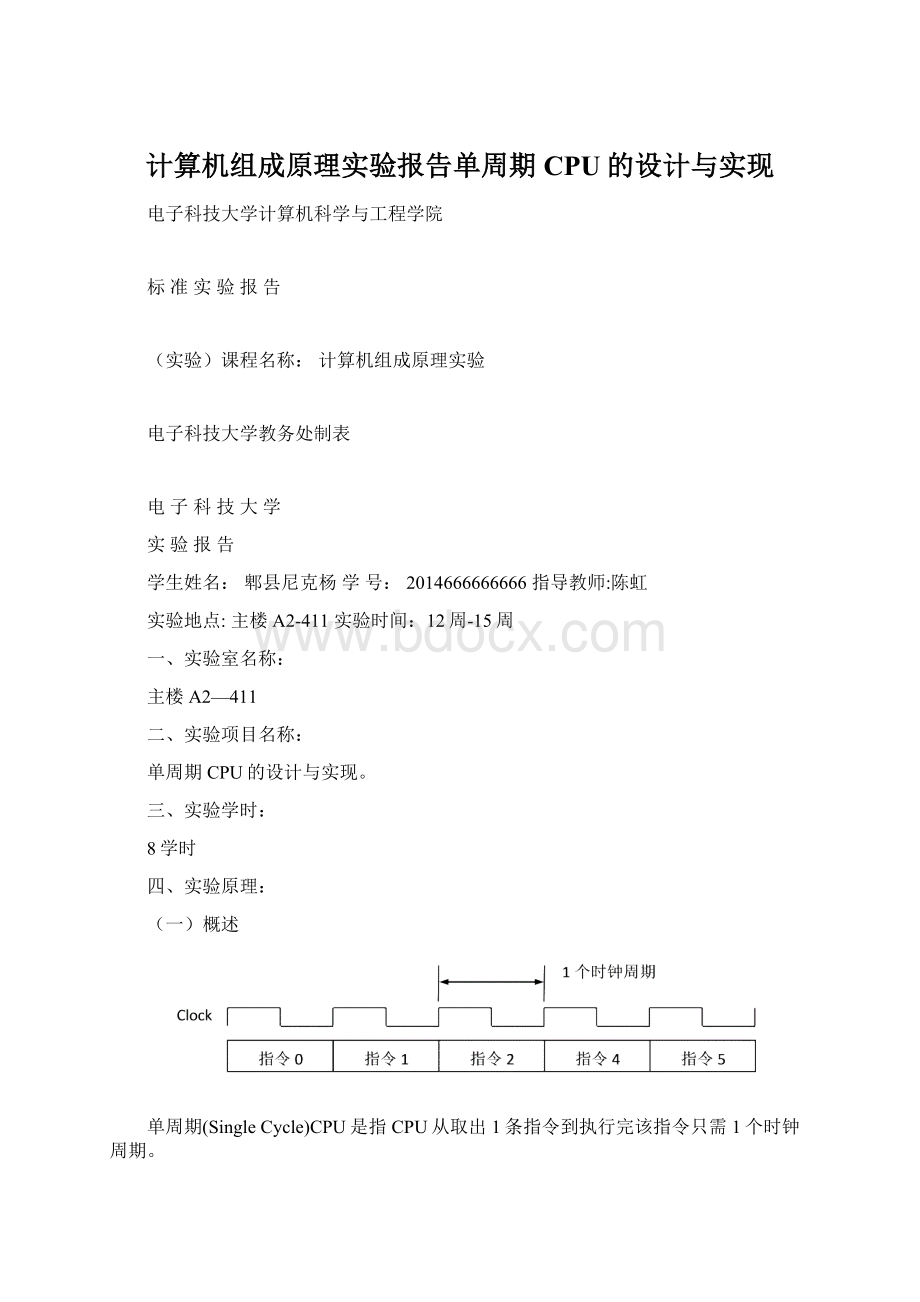

(一)概述

单周期(SingleCycle)CPU是指CPU从取出1条指令到执行完该指令只需1个时钟周期。

一条指令的执行过程包括:

取指令→分析指令→取操作数→执行指令→保存结果。

对于单周期CPU来说,这些执行步骤均在一个时钟周期内完成。

(二)单周期cpu总体电路

本实验所设计的单周期CPU的总体电路结构如下。

(三)MIPS指令格式化

MIPS指令系统结构有MIPS-32和MIPS—64两种。

本实验的MIPS指令选用MIPS-32。

以下所说的MIPS指令均指MIPS—32。

MIPS的指令格式为32位.下图给出MIPS指令的3种格式.

本实验只选取了9条典型的MIPS指令来描述CPU逻辑电路的设计方法。

下图列出了本实验的所涉及到的9条MIPS指令.

五、实验目的

1、掌握单周期CPU的工作原理、实现方法及其组成部件的原理和设计方法,如控制器、运算器等。

2、认识和掌握指令与CPU的关系、指令的执行过程.

3、熟练使用硬件描述语言Verilog、EDA工具软件进行软件设计与仿真,以培养学生的分析和设计CPU的能力。

六、实验内容

(一)拟定本实验的指令系统,指令应包含R型指令、I型指令和J型指令,指令数为9条.

(二)CPU各功能模块的设计与实现。

(三)对设计的各个模块的仿真测试。

(四)整个CPU的封装与测试.

七、实验器材(设备、元器件):

(一)安装了XilinxISEDesignSuite13。

4的PC机一台

(二)FPGA开发板:

AnvylSpartan6/XC6SLX45

(三)计算机与FPGA开发板通过JTAG(JointTestActionGroup)接口连接,其连接方式如图所示。

八、实验步骤

一个CPU主要由ALU(运算器)、控制器、寄存器堆、取指部件及其它基本功能部件等构成。

在本实验中基本功能部件主要有:

32位2选1多路选择器、5位2选1多路选择器、32位寄存器堆、ALU等。

(一)新建工程(NewProject)

启动ISEDesignSuite13。

4软件,然后选择菜单File→NewProject,弹出NewProjectWizard对话框,在对话框中输入工程名CPU,并指定工作路径D:

\Single_Cycle_CPU。

(二)基本功能器件的设计与实现

(1)多路选择器的设计与实现

a。

5位2选1多路选择器(MUX5_2_1)的设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

MUX5_2_1,然后输入其实现代码:

moduleMUX5_2_1(

input[4:

0]A,

input[4:

0]B,

inputSel,

output[4:

0]O

);

assignO=Sel?

B:

A;

endmodule

在ISE集成开发环境中,对模块MUX5_2_1进行综合(Synthesize),综合结果如图所示:

在ISE集成开发环境中,对模块MUX5_2_1进行仿真(Simulation)。

输入如下测式代码:

moduleMUX5_2_1_T;

//Inputs

reg[4:

0]A;

reg[4:

0]B;

regsel;

//Outputs

wire[4:

0]C;

//InstantiatetheUnitUnderTest(UUT)

MUX5_2_1uut(

.A(A),

。

B(B),

.sel(sel),

.C(C)

);

initialbegin

//InitializeInputs

A=0;

B=0;

sel=0;

//Wait100nsforglobalresettofinish

#100;

A=5'b10100;

B=0;

sel=1;

//Wait100nsforglobalresettofinish

#100;

A=1;

B=5’b10000;

sel=0;

//Wait100nsforglobalresettofinish

#100;

A=5'b00000;

B=5'b11000;

sel=1;

//Addstimulushere

end

endmodule

然后进行仿真,仿真结果如图所示:

b.32位2选1多路选择器的设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

MUX32_2_1,然后输入其实现代码:

moduleMUX32_2_1(

input[31:

0]A,

input[31:

0]B,

inputsel,

output[31:

0]O

);

assignO=sel?

B:

A;

endmodule

在ISE集成开发环境中,对模块MUX32_2_1进行综合(Synthesize),综合结果如图所示:

在ISE集成开发环境中,对模块MUX32_2_1进行仿真(Simulation)。

首先输入如下测式代码:

moduleMUX32_2_1_T;

//Inputs

reg[31:

0]A;

reg[31:

0]B;

regsel;

//Outputs

wire[31:

0]O;

//InstantiatetheUnitUnderTest(UUT)

MUX32_2_1uut(

。

A(A),

。

B(B),

。

sel(sel),

。

O(O)

);

initialbegin

A=0;

B=0;

sel=0;

//Wait100nsforglobalresettofinish

#100;

A=32’h00000001;

B=32’h00000000;

sel=1;

#100;

A=32’h00000101;

B=32’h00000010;

sel=0;

//Addstimulushere

end

endmodule

然后进行仿真,仿真结果如图所示:

(2)符号扩展(Sign_Extender)的设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

Sign_Extender,然后输入其实现代码:

moduleSign_Extender(

input[15:

0]d,

output[31:

0]o

);

assigno=(d[15:

15]==1’b0)?

{16’b0,d[15:

0]}:

{16’b1,d[15:

0]};

endmodule

在ISE集成开发环境中,对模块Sign_Extender进行综合(Synthesize),综合结果如图所示。

在ISE集成开发环境中,对模块MUX32_2_1进行仿真(Simulation).首先输入如下测式代码:

moduleSign_Extender_t;

//Inputs

reg[15:

0]d;

//Outputs

wire[31:

0]o;

//InstantiatetheUnitUnderTest(UUT)

Sign_Extenderuut(

。

d(d),

.o(o)

);

initialbegin

//InitializeInputs

d=0;

//Wait100nsforglobalresettofinish

#100;

//Addstimulushere

d=16'h0011;

#100;

d=16’h1011;

end

endmodule

然后进行仿真,仿真结果如图所示:

(3)32位寄存器堆(RegFile)的设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

RegFile,然后输入其实现代码:

moduleRegFile(

input[4:

0]Rn1,Rn2,Wn,

inputWrite,

input[31:

0]Wd,

output[31:

0]A,B,

inputClock

);

reg[31:

0]Register[1:

31];

assignA=(Rn1==0)?

0:

Register[Rn1];

assignB=(Rn2==0)?

0:

Register[Rn2];

always@(posedgeClock)begin

if(Write&&Wn!

=0)

Register[Wn]〈=Wd;

end

endmodule

在ISE集成开发环境中,对模块RegFile进行综合(Synthesize),综合结果如图所示。

在ISE集成开发环境中,对模块RegFile进行仿真(Simulation)。

输入如下测式代码:

moduleRegfile_t;

//Inputs

reg[4:

0]Rn1;

reg[4:

0]Rn2;

reg[4:

0]Wn;

regWrite;

reg[31:

0]Wd;

regClock;

//Outputs

wire[31:

0]A;

wire[31:

0]B;

//InstantiatetheUnitUnderTest(UUT)

RegFileuut(

。

Rn1(Rn1),

.Rn2(Rn2),

.Wn(Wn),

.Write(Write),

.Wd(Wd),

.A(A),

。

B(B),

.Clock(Clock)

);

initialbegin

//InitializeInputs

Rn1=0;

Rn2=0;

Wn=0;

Write=0;

Wd=0;

Clock=0;

//Wait100nsforglobalresettofinish

#100;

Rn1=5'b00001;

Rn2=5’b00001;

Wn=5'b00001;

Write=1;

Wd=0;

Clock=0;

#100;

Clock=1;

#50;

Wd=32’hBBBBBBBB;

#50;

Clock=0;

#100;

Clock=1;

#100

Clock=0;

//Addstimulushere

end

endmodule

然后进行仿真,仿真结果如图所示:

(4)运算器(ALU)设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

ALU,然后输入其实现代码:

moduleALU(

input[31:

0]A,B,

input[2:

0]ALU_operation,

output[31:

0]Result,

outputZero

);

assignResult=(ALU_operation==3'b000)?

A+B:

(ALU_operation==3'b100)?

A—B:

(ALU_operation==3'b001)?

A&B:

(ALU_operation==3'b101)?

A|B:

(ALU_operation==3’b010)?

A^B:

(ALU_operation==3’b110)?

{B[15:

0],16’h0}:

32’hxxxxxxxx;

assignZero=~|Result;

endmodule

在ISE集成开发环境中,对模块ALU进行综合(Synthesize),综合结果如图所示:

在ISE集成开发环境中,对模块ALU进行仿真(Simulation).输入如下测式代码:

moduleALU_tb;

//Inputs

reg[31:

0]A;

reg[31:

0]B;

reg[2:

0]ALU_operation;

//Outputs

wire[31:

0]Result;

wireZero;

//InstantiatetheUnitUnderTest(UUT)

ALUuut(

。

A(A),

.B(B),

.ALU_operation(ALU_operation),

.Result(Result),

。

Zero(Zero)

);

initialbegin

//InitializeInputs

A=0;

B=0;

ALU_operation=0;

//Wait100nsforglobalresettofinish

#100;

A=1;

B=1;

ALU_operation=0;

//Addstimulushere

#100

A=2;

B=2;

ALU_operation=4;

#100

A=1;

B=1;

ALU_operation=1;

#100

A=1;

B=1;

ALU_operation=5;

#100

A=1;

B=1;

ALU_operation=2;

end

endmodule

然后进行仿真,仿真结果如图所示:

(5)控制器(Controller)的设计与实现

为了简化设计,控制器由控制单元Control和控制单元ALUop组成,控制器结构如下所示.

a.Control的设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

Control,然后输入其实现代码:

moduleControl(

input[5:

0]op,

outputRegDst,

outputRegWrite,

outputALUSrc,

outputMemWrite,

outputMemRead,

outputMemtoReg,

outputBranch,

output[1:

0]ALUctr

);

wirei_Rt=~|op;

wirei_Lw=op[5]&~op[3];

wirei_Sw=op[5]&op[3];

wirei_Beq=op[2]&~op[1];

wirei_Lui=op[3]&op[2];

assignRegDst=i_Rt;

assignRegWrite=i_Rt|i_Lw|i_Lui;

assignALUSrc=i_Lw|i_Sw|i_Lui;

assignMemWrite=i_Sw;

assignMemRead=i_Lw;

assignMemtoReg=i_Lw;

assignBranch=i_Beq;

assignALUctr[1]=i_Rt|i_Lui;

assignALUctr[0]=i_Beq|i_Lui;

endmodule

在ISE集成开发环境中,对模块Control进行综合(Synthesize),综合结果如图:

在ISE集成开发环境中,对模块Control进行仿真(Simulation)。

首先输入如下测式代码:

moduleControl_tb;

//Inputs

reg[5:

0]op;

//Outputs

wireRegDst;

wireRegWrite;

wireALUSrc;

wireMemWrite;

wireMemRead;

wireMemtoReg;

wireBranch;

wire[1:

0]ALUctr;

//InstantiatetheUnitUnderTest(UUT)

Controluut(

.op(op),

。

RegDst(RegDst),

.RegWrite(RegWrite),

。

ALUSrc(ALUSrc),

。

MemWrite(MemWrite),

.MemRead(MemRead),

.MemtoReg(MemtoReg),

。

Branch(Branch),

.ALUctr(ALUctr)

);

initialbegin

//InitializeInputs

op=0;

//Wait100nsforglobalresettofinish

#100;

op=6'b000000;

#100;

op=6’b100011;

#100;

op=6'b101011;

#100;

op=6'b000100;

#100;

op=6'b001111;

end

endmodule

然后进行仿真,仿真结果如图所示:

b.ALUop的设计与实现

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

ALUop,然后输入其实现代码:

moduleALUop(

input[5:

0]func,

input[1:

0]ALUctr,

output[2:

0]ALU_op

);

wirei_Rt=ALUctr[1]&~ALUctr[0];

assignALU_op[2]=(i_Rt&((~func[2]&func[1])|(func[2]&func[0])))|ALUctr[0];

assignALU_op[1]=(i_Rt&func[2]&func[1])|(ALUctr[1]&ALUctr[0]);

assignALU_op[0]=(i_Rt&func[2]&~func[1]);

endmodule

在ISE集成开发环境中,对模块ALUop进行综合(Synthesize),综合结果如图:

在ISE集成开发环境中,对模块ALUop进行仿真(Simulation)。

首先输入如下测式代码:

moduleALU_tb;

//Inputs

reg[31:

0]A;

reg[31:

0]B;

reg[2:

0]ALU_operation;

//Outputs

wire[31:

0]Result;

wireZero;

//InstantiatetheUnitUnderTest(UUT)

ALUuut(

。

A(A),

。

B(B),

.ALU_operation(ALU_operation),

。

Result(Result),

.Zero(Zero)

);

initialbegin

//InitializeInputs

A=0;

B=0;

ALU_operation=0;

//Wait100nsforglobalresettofinish

#100;

A=1;

B=1;

ALU_operation=0;

//Addstimulushere

#100

A=2;

B=2;

ALU_operation=4;

#100

A=1;

B=1;

ALU_operation=1;

#100

A=1;

B=1;

ALU_operation=5;

#100

A=1;

B=1;

ALU_operation=2;

end

endmodule

然后进行仿真,仿真结果如图所:

c.将Control与ALUop封装成Controller

在ISE集成开发环境中,在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择NewSource命令,创建一个VerilogModule模块,名称为:

Controller,然后输入其实现代码:

moduleController(

input[5:

0]op,

input[5:

0]func,

outputRegDst,

outputRegWrite,

outputALUSrc,

outputMemWrite,

outputMemRead,

outputMemtoReg,

outputBranch,

output[2:

0]ALU_op

);

wire[1:

0]ALUctr;

ControlU0(op,RegDst,RegWrite,ALUSrc,MemWrit