基于Quartus II的400240像素液晶显示驱动设计综述.docx

《基于Quartus II的400240像素液晶显示驱动设计综述.docx》由会员分享,可在线阅读,更多相关《基于Quartus II的400240像素液晶显示驱动设计综述.docx(12页珍藏版)》请在冰豆网上搜索。

基于QuartusII的400240像素液晶显示驱动设计综述

一、实验要求

要求根据图2-1及表2-1的参数,选用Altera公司的Cyclone系列芯片EP1C12Q240C8,在Quartus9.0环境下编写该液晶显示器的驱动程序,使得该液晶显示器(400*240像素)可以进行两种显示模式,即黑白隔行显示、黑白隔列显示,并在Quartus9.0环境下编译通过。

其中给定外部时钟频率为40MHz,四分频后10MHz信号提供给DOTCLK输入。

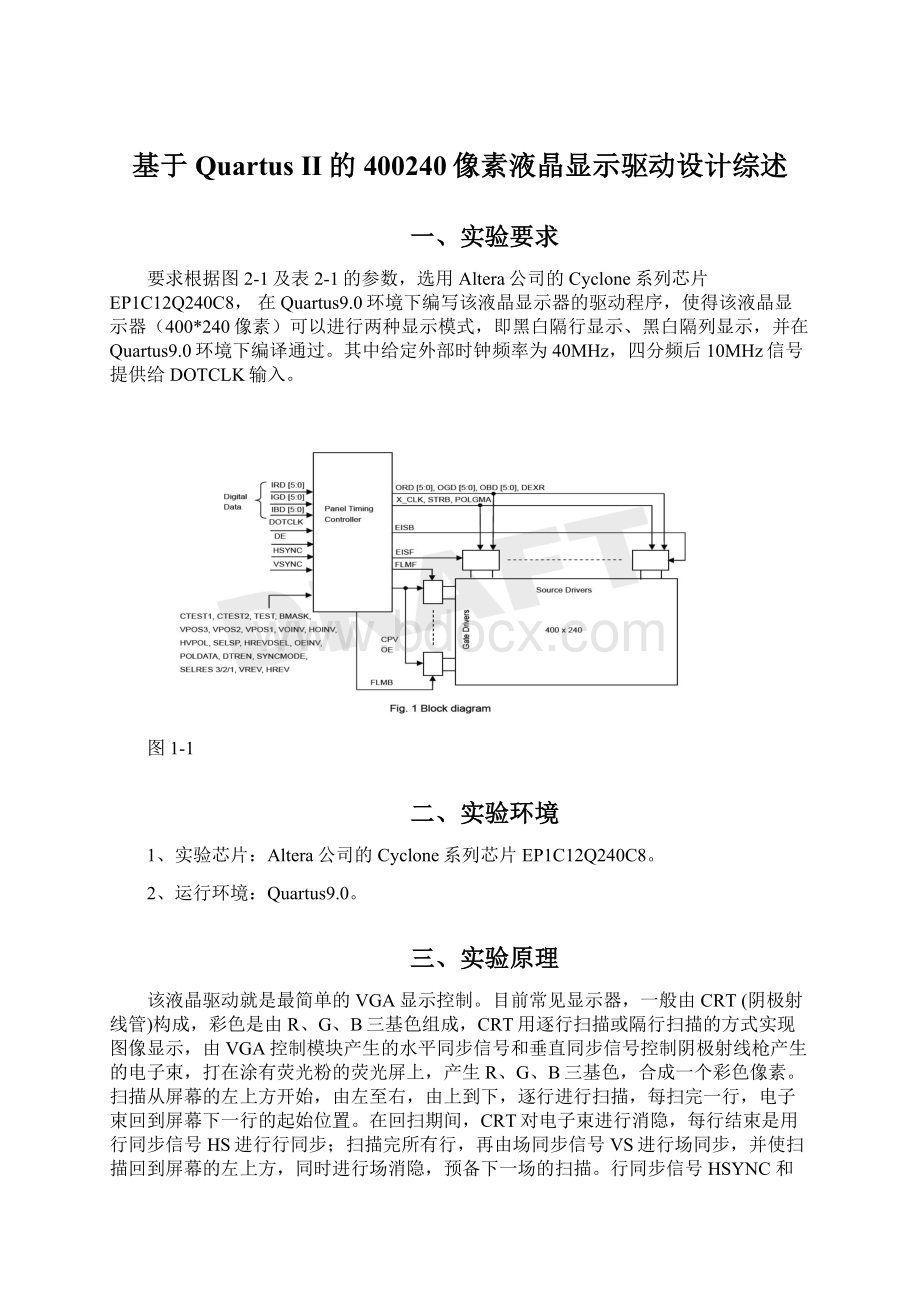

图1-1

二、实验环境

1、实验芯片:

Altera公司的Cyclone系列芯片EP1C12Q240C8。

2、运行环境:

Quartus9.0。

三、实验原理

该液晶驱动就是最简单的VGA显示控制。

目前常见显示器,一般由CRT(阴极射线管)构成,彩色是由R、G、B三基色组成,CRT用逐行扫描或隔行扫描的方式实现图像显示,由VGA控制模块产生的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

扫描从屏幕的左上方开始,由左至右,由上到下,逐行进行扫描,每扫完一行,电子束回到屏幕下一行的起始位置。

在回扫期间,CRT对电子束进行消隐,每行结束是用行同步信号HS进行行同步;扫描完所有行,再由场同步信号VS进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

行同步信号HSYNC和场同步信号VSYNC是两个重要的信号。

显示过程中,HSYNC和VSYNC的极性可正可负,显示器内可自动转换为正极性逻辑。

显示器每扫描完一行,再扫描下一行时会花一定时间来准备,因此要满足时序要求,如图2-1所示。

图2-1VGA行扫描时序图

同样每扫描完一帧,再扫描下一帧行时也会花一定时间来准备,因此也要满足其时序要求,如图2-2所示。

图2-2VGA场扫描时序图

分析图1-1和表2-1可知,该液晶驱动程序需要产生七个信号,即IRD、IGD、IBD、HSYNC、VSYNC、DE和DOTCLK。

其中IRD、IGD、IBD分表表示R、G、B三种颜色,HSYNC和VSYNC分别表示行扫描和场扫描,DE表示信号输入,DOTCLK是外部时钟四分频后的时钟信号。

表2-1液晶驱动引脚说明

实验要求时序图,如下图2-3和所示:

图2-3输出时序图

表2-2参数表

观察输出时序图2-3和参数说明表2-2,对照图2-1VGA行扫描时序图和图2-2场扫描时序图,可以计算出行扫描时序要求和场扫描时序要求。

表2-3行扫描时序要求(单位:

像素,即输出一个像素的时间间隔)

行同步头

行图像

行周期

对应位置

Tf

Ta

Tb

Tc

Td

Te

Tg

时间(Pixels)

0

2

6

0

400

0

408

表2-4场扫描时序要求(单位:

像素,即输出一个像素的时间间隔)

行同步头

行图像

行周期

对应位置

Tf

Ta

Tb

Tc

Td

Te

Tg

时间(Pixels)

0

1

0

0

240

0

241

本实验要求隔行黑白显示和隔列黑白显示,且表示三基色R、G、B的IRD、IBD和IGD均是六位输出,故R、G、B对应颜色编码如下表所示:

表2-5颜色编码

颜色

R

G

B

黑

000000

000000

000000

白

111111

111111

111111

四、实验源代码

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYLCD_DRIVERIS

PORT(

SCLKIN:

INSTD_LOGIC;

MODE:

INSTD_LOGIC;

IRD:

OUTSTD_LOGIC_VECTOR(5DOWNTO0);

IGD:

OUTSTD_LOGIC_VECTOR(5DOWNTO0);

IBD:

OUTSTD_LOGIC_VECTOR(5DOWNTO0);

DOT_CLK:

OUTSTD_LOGIC;

DE:

OUTSTD_LOGIC;

HSYNC:

OUTSTD_LOGIC;

VSYNC:

OUTSTD_LOGIC);

ENDLCD_DRIVER;

ARCHITECTUREONEOFLCD_DRIVERIS

SIGNALSYS_CLK:

STD_LOGIC;

SIGNALVDOT_CNT,CC:

STD_LOGIC_VECTOR(7DOWNTO0):

="00000000";--COUNTVERTICALPIXEL

SIGNALHDOT_CNT,LL:

STD_LOGIC_VECTOR(8DOWNTO0):

="000000000";--COUNTHORIZONTAIPIXEL

SIGNALRGBX:

STD_LOGIC_VECTOR(5DOWNTO0):

="000000";--COLUMNDISPLAY

SIGNALRGBY:

STD_LOGIC_VECTOR(5DOWNTO0):

="000000";--LINEDISPALY

SIGNALRGBP:

STD_LOGIC_VECTOR(5DOWNTO0):

="000000";

SIGNALDE_SIG:

STD_LOGIC:

='1';--DESIGNAL

SIGNALHSYNC_SIG:

STD_LOGIC:

='1';

SIGNALVSYNC_SIG:

STD_LOGIC:

='1';

CONSTANTH_A:

INTEGER:

=402;CONSTANTH_B:

INTEGER:

=408;CONSTANTH_D:

INTEGER:

=400;

CONSTANTV_A:

INTEGER:

=241;CONSTANTV_D:

INTEGER:

=240;

BEGIN

--FOURDIVIDEDCLOCK

PROCESS(SCLKIN)

VARIABLESYS_DIV:

STD_LOGIC_VECTOR(1DOWNTO0);

BEGIN

IFSCLKIN'EVENTANDSCLKIN='1'THEN

SYS_DIV:

=SYS_DIV+1;

ENDIF;

SYS_CLK<=SYS_DIV

(1);

ENDPROCESS;

PROCESS(SCLKIN,MODE)BEGIN

IFMODE='1'THENRGBP<=RGBX;

ELSIFMODE='0'THENRGBP<=RGBY;

ENDIF;

ENDPROCESS;

--GENERATEHYSNCSIGNAL

PROCESS(SYS_CLK)

BEGIN

IFSYS_CLK'EVENTANDSYS_CLK='1'THEN

HDOT_CNT<=HDOT_CNT+1;

ENDIF;

IFHDOT_CNTDE_SIG<='1';

HSYNC_SIG<='0';

ENDIF;

IFHDOT_CNT=H_DTHEN

DE_SIG<='0';

ENDIF;

IFHDOT_CNT=H_ATHEN

HSYNC_SIG<='1';

ENDIF;

IFHDOT_CNT=H_A+2THEN

HSYNC_SIG<='0';

ENDIF;

IFHDOT_CNT=H_BTHEN

HDOT_CNT<="000000000";

ENDIF;

ENDPROCESS;

--GENERATEVETICALSIGNAL

PROCESS(SYS_CLK)

BEGIN

IFSYS_CLK'EVENTANDSYS_CLK='1'THEN

IFHDOT_CNT=H_B-1THEN

VDOT_CNT<=VDOT_CNT+1;

IFVDOT_CNT=V_ATHEN

VDOT_CNT<="00000000";

ENDIF;

ENDIF;

ENDIF;

IF(VDOT_CNT>=V_D)AND(VDOT_CNTVSYNC_SIG<='1';

ELSE

VSYNC_SIG<='0';

ENDIF;

ENDPROCESS;

LL<=HDOT_CNT;CC<=VDOT_CNT;--JUSTFORKEYCODESIMPLY

PROCESS(LL,CC)

BEGIN

IFLL<40THENRGBX<="111111";--DISPLAYWHITE

ELSIFLL<80THENRGBX<="000000";--DISPLAYBALCK

ELSIFLL<120THENRGBX<="111111";

ELSIFLL<160THENRGBX<="000000";

ELSIFLL<200THENRGBX<="111111";

ELSIFLL<240THENRGBX<="000000";

ELSIFLL<280THENRGBX<="111111";

ELSIFLL<320THENRGBX<="000000";

ELSIFLL<360THENRGBX<="111111";

ELSIFLL<400THENRGBX<="000000";

ELSERGBX<="000000";

ENDIF;

IFCC<20THENRGBY<="111111";

ELSIFCC<40THENRGBY<="000000";

ELSIFCC<60THENRGBY<="111111";

ELSIFCC<80THENRGBY<="000000";

ELSIFCC<100THENRGBY<="111111";

ELSIFCC<120THENRGBY<="000000";

ELSIFCC<140THENRGBY<="111111";

ELSIFCC<160THENRGBY<="000000";

ELSIFCC<180THENRGBY<="111111";

ELSIFCC<200THENRGBY<="000000";

ELSIFCC<220THENRGBY<="111111";

ELSIFCC<240THENRGBY<="000000";

ELSERGBY<="000000";

ENDIF;

ENDPROCESS;

PROCESS(VSYNC_SIG)

BEGIN

IFSYS_CLK'EVENTANDSYS_CLK='1'THEN

HSYNC<=HSYNC_SIG;

VSYNC<=VSYNC_SIG;

IFVDOT_CNTIRD<=RGBP;

IGD<=RGBP;

IBD